HDMI高清音視頻系統的高速PCB的研究及實現

李俊杰,曹旭東,梁華慶,曹生彪,張少華

(中國石油大學(北京) 地球物理與信息工程學院,北京102249)

?

HDMI高清音視頻系統的高速PCB的研究及實現

李俊杰,曹旭東,梁華慶,曹生彪,張少華

(中國石油大學(北京) 地球物理與信息工程學院,北京102249)

為了能夠消除高速PCB技術中信號完整性的問題,需要在高速PCB設計過程中解決時序、噪聲、電磁干擾等關鍵問題。研究了HDMI高清音視頻系統的高速PCB設計過程中出現的串擾、電磁干擾、振鈴和電源完整性等信號問題,提出削弱或消除以上噪聲的方法。用Altium Designer,PADS軟件繪制電路原理圖和PCB,借助Hyper Lynx和ADS仿真軟件進行前端和后端可靠性驗證,最后通過對完成布線的PCB進行信號完整性驗證。測試結果表明此方案設計的HDMI高清音視頻系統工作穩定,在智能設備的升級替換和建設方面有重要的借鑒作用。

高速PCB;信號完整性;HDMI;音視頻

現代的電子系統向著封裝小、規模大、速度快的趨勢發展,與此同時,在超大規模集成電路中,芯片的密度越來越大,這就不可避免地會帶來一些問題,即如何分析和處理高速電路設計中互連線和疊層特征等因素。當今電子產品的時鐘頻率達到幾百上千MHz,信號的上升沿和下降沿變得越來越陡。因此,設計此類產品時,PCB的布局布線規則和板材介電常數對系統的電氣特性至關重要。

高速PCB電路設計是當前眾多電子產品研發的必要流程和重要環節,時序問題、噪聲干擾、電磁滋擾等是高速PCB電路設計的主要難題,這些問題的解決將關系到系統設計的正常運行[1]。

本文在HDMI高清音視頻系統中,以高速PCB仿真與設計作為主要研究內容,利用Hyper Lynx和ADS軟件進行PCB布局布線前端仿真,按照仿真結果確定元器件和接插件的分布以及走線規則,最后通過對完成布線的PCB進行信號完整性驗證[2],確保設計的產品達到進入市場的標準。

1 系統方案設計

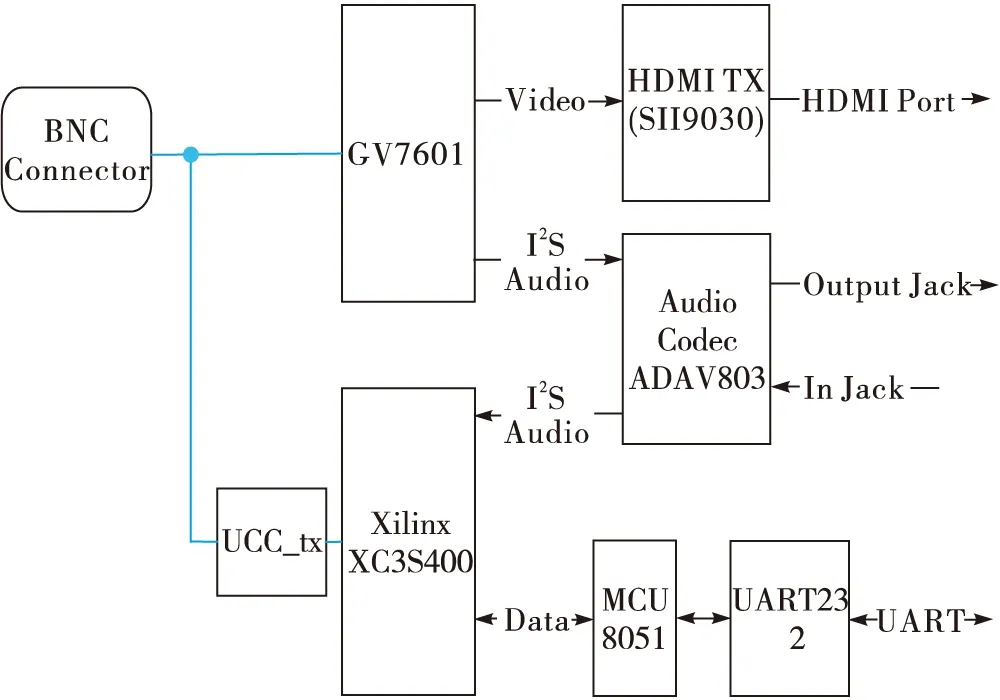

HDMI是分辨率很高的音視頻接口,攜帶4組差分對,完成音視頻信息的高速傳輸[3]。該系統是基于新唐的51單片機W78E516D和Xilinx的XC3S400,當圖像分辨率為1 080p時,20 bit并行數據流傳輸速率高達148.5 MHz。為了保證音頻和視頻數據輸出的并行性,提高傳輸質量,本文采用GV7601對音視頻信號進行硬解碼,并且輸出的MCLK提供給Audio設備ADAV803,輸出的PCLK提供給Video設備SIL9030。

音頻通道選擇由8051通過四線制SPI配置,音頻信號以I2S協議給ADAV803,由8051以I2C兼容性串口進行編程控制,進行Audio Code成模擬信號到耳機等發聲器;由8051通過I2C編程SIL9030寄存器,將輸入的YCbCr 4∶2∶2數據轉換成YCbCr 4∶4∶4,然后傳送到HDMI Link。系統設計框架如圖1所示。

圖1 HDMI系統框架

2 系統硬件設計

根據設計的要求,硬件主要包括電源模塊、音頻和視頻處理單元、音頻模數處理單元和視頻處理單元4個部分。圖2所示為實際設計的電路板。

圖2 HDMI音視頻電路板

2.1 系統PCB疊層設計

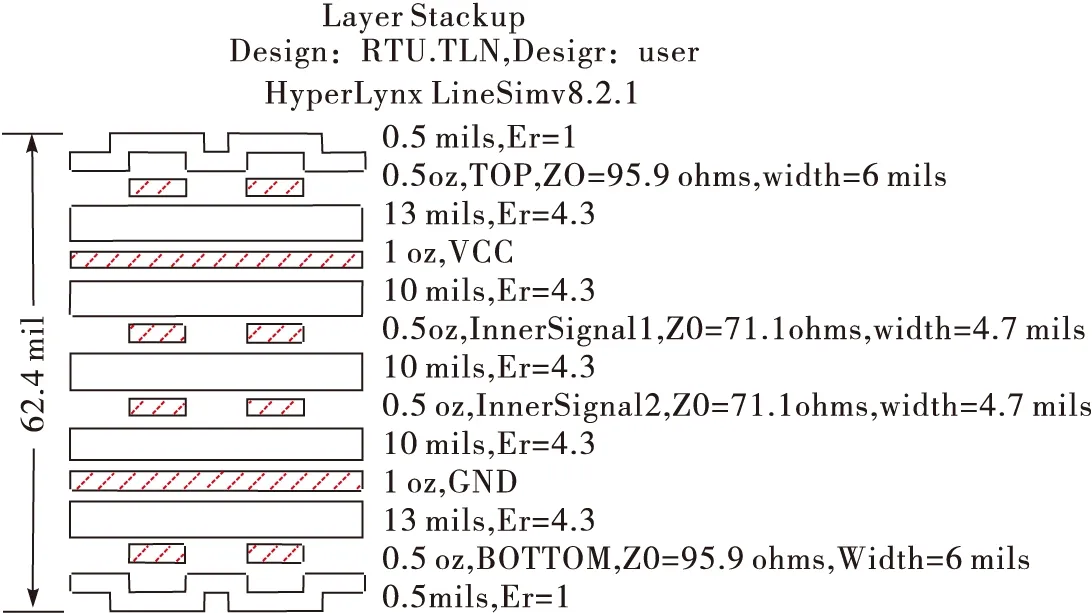

該HDMI音視頻系統元器件的封裝密集、布局布線空間小、信號頻率高等因素決定設置6層PCB。

PCB疊層設計如圖3所示。頂層是電氣層,用于布線;第2層是內電層,整層都是數字地網絡;第3、4層是電氣層,用于布線;第5層是內電層,用于不同電源網絡的分割;底層是電氣層,用于布線[4]。

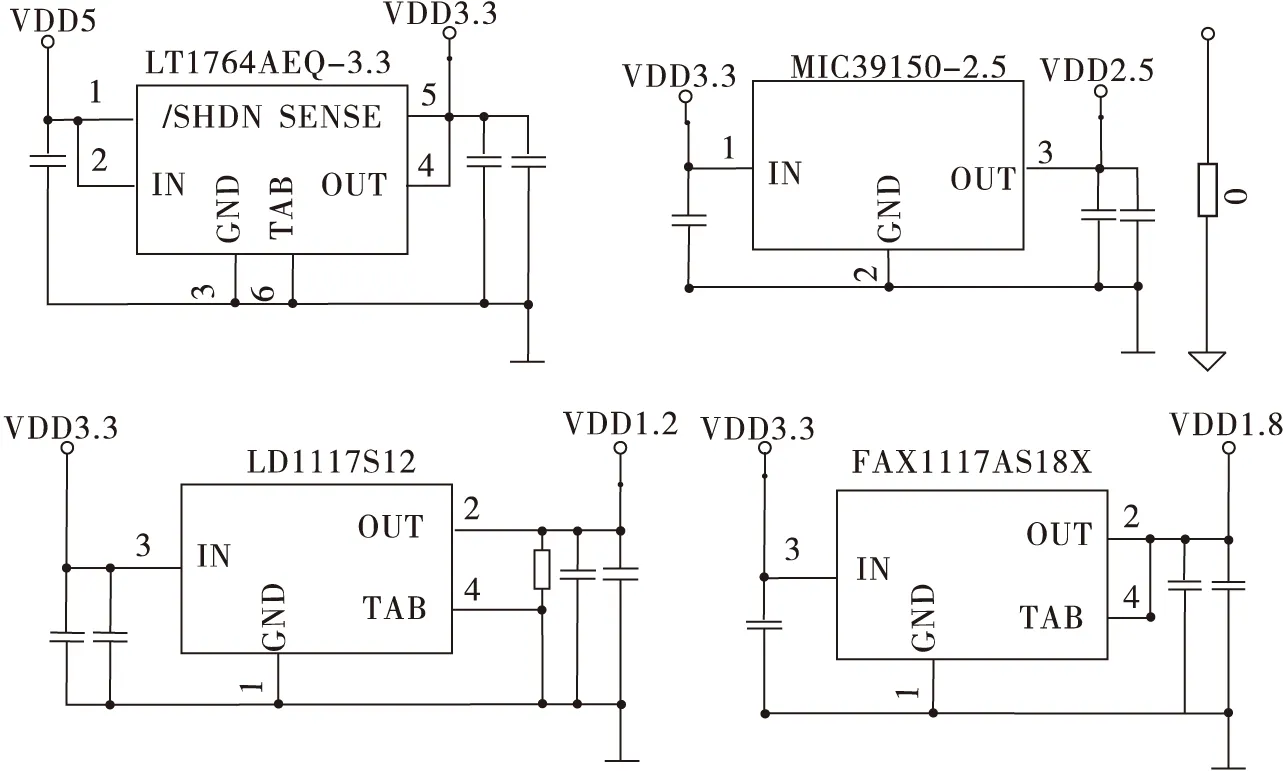

2.2 電源單元設計

該HDMI高清音視頻系統需要的電源種類多,布局復雜,圖4所示為主要電平轉換穩壓電路,系統輸入電源為5 V,通過LT1764穩壓模塊輸出3.3 V的電源,3.3 V電源再分別通過MIC39150-2.5BU,LD1117S12,FAN1117AS18X穩壓模塊輸出2.5 V,1.2 V和1.8 V電源。

圖3 高速PCB疊層分布

圖4 系統電源電路

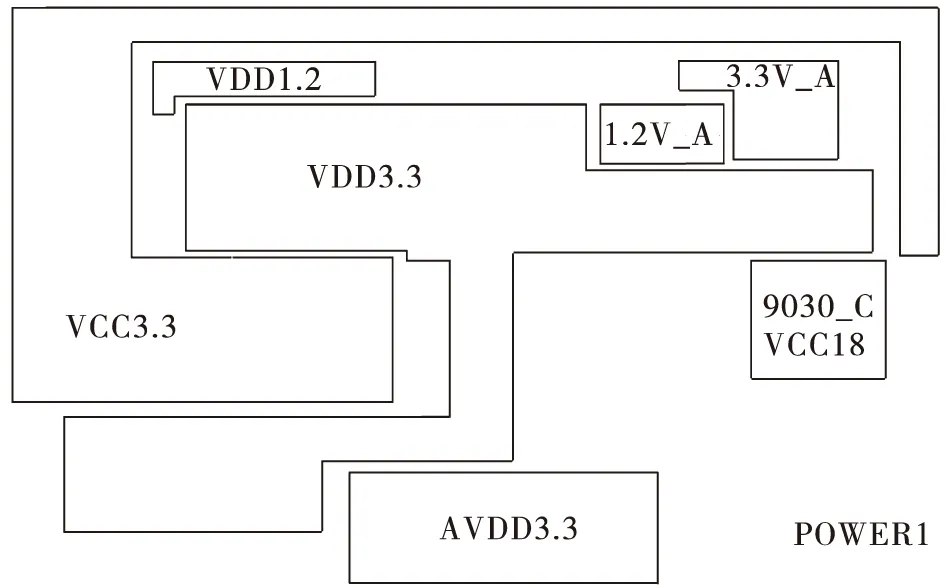

圖4中的VDD3.3,VDD2.5和VDD1.2通過磁珠隔離輸出VCC3.3,VCC2.5和VCC1.2,放置較大的極性電容和小容值的無極性電容給XC3S400供電;VDD3.3和VDD1.2通過0 Ω電阻隔離輸出3.3 V_A和1.2 V_A給GV7601供電;VDD3.3通過磁珠隔離輸出P3.3 VA,通過0 Ω電阻隔離輸出AVDD3.3給ADAV803供電;VDD5通過SMDC110自恢復保險絲輸出9030_5V;VDD33通過BLM21PG221SN1D隔離輸出9030_AVCC,再通過3個0 Ω電阻隔離輸出9030_PVCC1,9030_PVCC2和9030_IOCC;VDD18通過BLM21PG221SN1D隔離輸出9030_CVCC18,這些電源是給SIL9030供電的。圖5所示為POWER1電源內電層的分割圖。

圖5 系統電路板的電源分布

2.3 音視頻輸入單元設計

音視頻數據以串行的形式進入GV7601,經過解析輸出數據流的速率有270 Mbit/s、1.485 Gbit/s和2.97 Gbit/s三種模式,在基于同軸電纜的視頻系統中,逐行分量數字視頻高達1 920×1 080。圖6所示為音視頻輸入單元基本電路。

應用投入導向規模效率可變BCC模型,運用DEAP2.1軟件,對2009年和2016年我國各區域高技術產業技術創新效率進行測算,結果見表2。

圖6 音視頻輸入電路

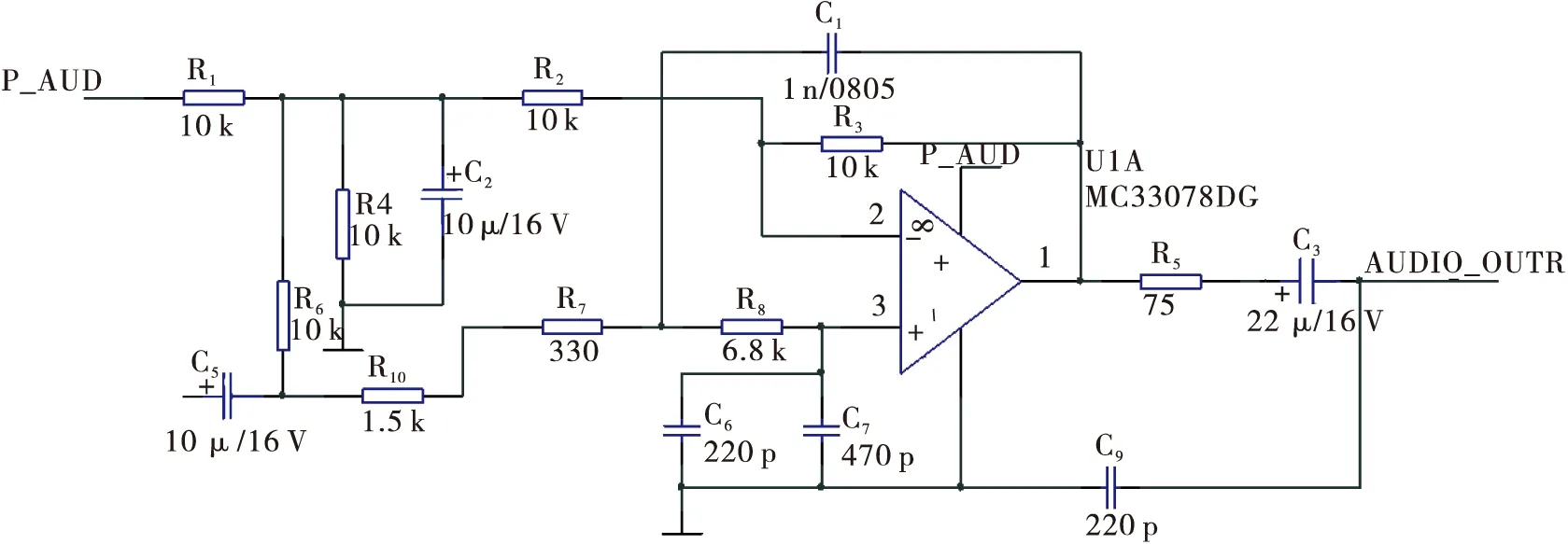

2.4 音頻輸出單元設計

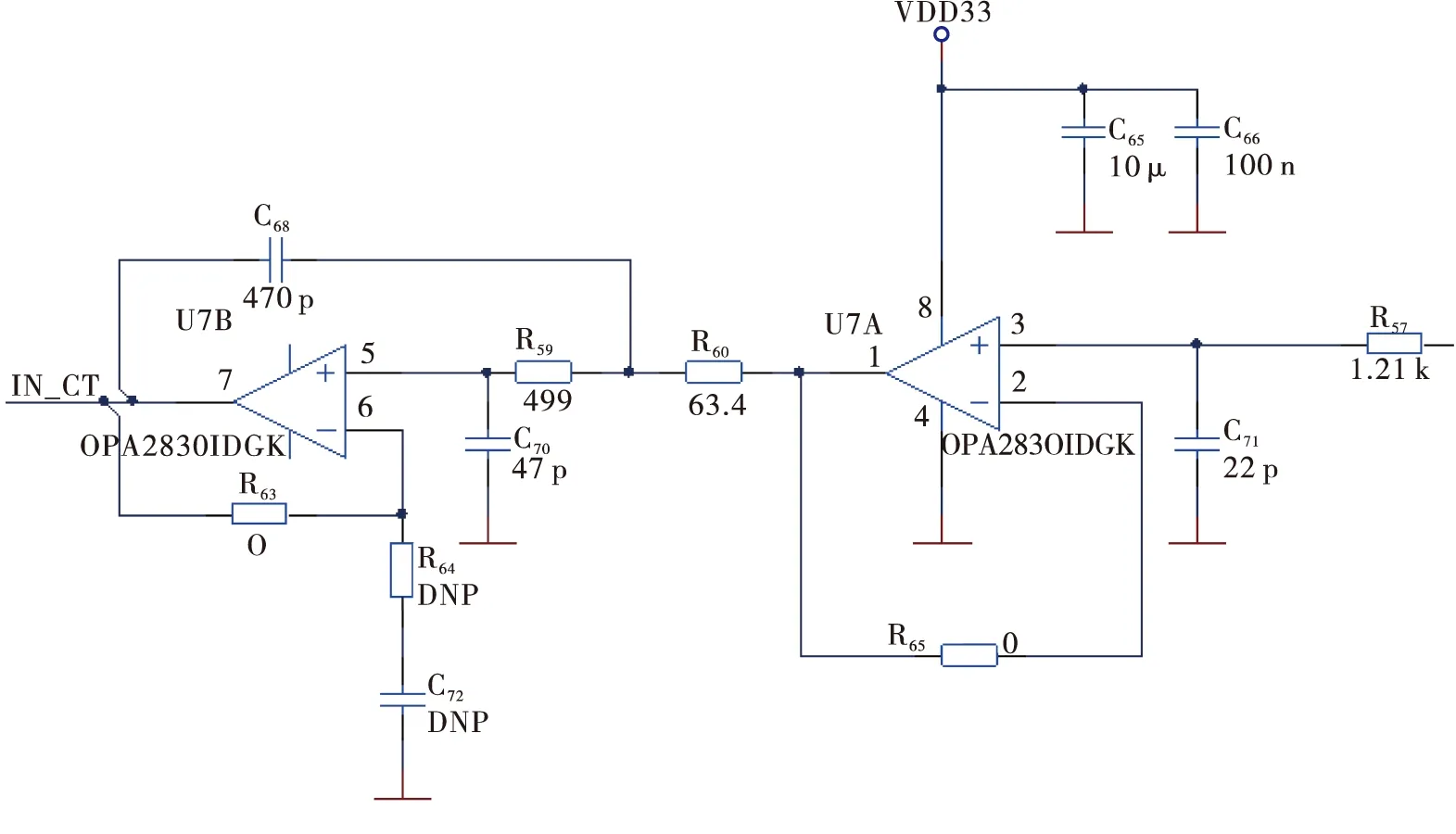

ADAV803是ADI公司的立體音頻編解碼器,其操作指令是通過一個I2C兼容型串行接口,對各個控制寄存器的設定進行編程控制。ADC提供采樣頻率可選,分辨率高達24位的輸出字。圖7所示為左右兩個聲道音頻信號進出的電路圖。

圖7 音視輸出電路圖

2.5 視頻輸出單元設計

SIL9030是Silicon Image公司生產的第二代數字接口產品,是以HMDI接口單元為背景,增加了音頻數據傳輸功能,支持1 080p的視頻分辨率。SIL9030是一款高性能的HDMI發送器,被廣泛應用于DVD播放器、A/V接收機和D-VHS唱片機等家庭影音產品[5]。W78E516D通過I2C總線與它通信,完成視頻編碼,輸出3路YCbCr(4∶2∶2)的TMDS數據流和1路時鐘信號到HDMI接口[2],如圖8所示。

圖8 視頻輸出單元電路圖

3 電源完整性設計

當前電源完整性(PI)指的是電能從電源端被傳遞到負載的線性度,可以從交流和直流兩方面進行分析。PCB電路系統中以阻容器件為主,信號線容易造成電感效應,這三者之間存在著相互作用。信號經過感性傳輸線會產生一個壓降,導致正在給IC供電的電源電壓降低,影響電子單元的正常工作。在高頻電路中,容性和感性容易造成諧振,降低信號傳輸質量,甚至引發IC誤操作[6]。

要驅動整個系統的負載需要提供很大的電流,這會使電源產生壓降,為了保持電源電壓容差不超過負載的極限值,必須進行DC分析。例如設計中沿導軌1.8 V的電位差下降必須小于0.1 V,否則就會發生故障。電源分配網絡的特征阻抗隨著頻率響應造成SI、抖動和EMI等問題,因此AC分析也必不可少[7]。

4 高速PCB信號環路設計

4.1 內電層分割設計

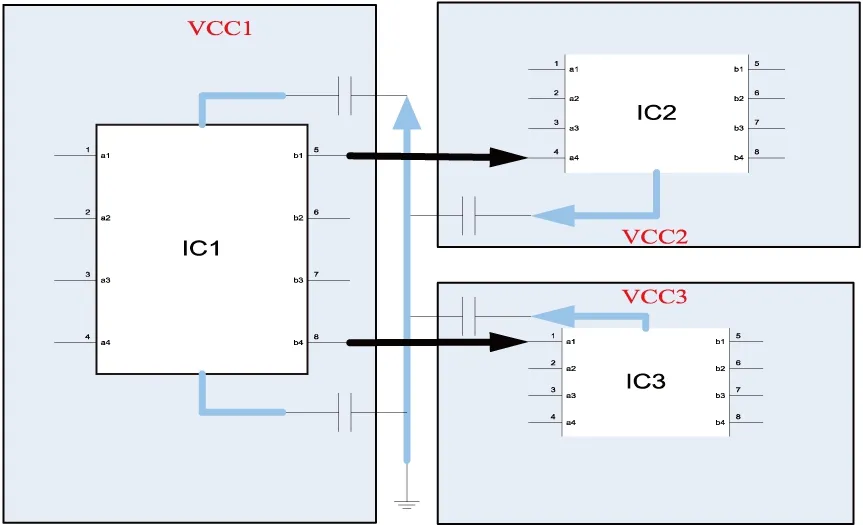

在一個電路系統中可能存在多種電源和地,靠鋪銅、打孔已經不能連接信號的回流路徑,這時多是采用分割內電層的技術,按照電源網絡的分布情況分割電源內電層,對于地網絡內電層,一般不予分割。如圖9所示,將電源層分割成多個相互獨立的部分,并標注相應的網絡標號,此時會造成信號參考層的分裂,返回信號是無法穿越這條裂縫的,只能通過耦合電容和過孔返回地層。

圖9 電源分割情況下的信號回流路徑(截圖)

在2個參考層的間隙放置高頻和低頻耦合電容,能夠減小信號回路面積。一些芯片具有多組電源管腳,在設計過程中每一個電源管腳附近都選配一個耦合電容,一是可以濾除噪聲干擾,給芯片提供文波較小的電源,一是為信號搭建最佳的返回路徑[9]。高速PCB布線應盡量避開信號線穿越裂縫上方,而且要保持地層完整,這樣才能得到較好的信號完整性。

4.2 過孔連接信號環路

信號從驅動端到達接收端有時需要放置過孔切換層次,在高速數字電路設計中一般會有2個參考層,信號線在參考層之間的電氣層布線,信號不可能透過絕緣介質返回驅動端,使用過孔連接參考層可以縮短信號環路。

電源層和地層對于信號來說都是參考層,設置疊層分布時應該減小二者之間的間距。如果信號傳輸過程中是以電源層為參考層,沿過孔表面切換到其他電氣層,這時信號的參考平面可能變成地層,雖然也能返回驅動端,但是會產生地陷或電源塌陷等信號完整性問題。所以,切換布線層后一般在過孔附近安裝耦合電容,為信號搭建有利的返回路徑。如圖10所示,這樣就能保證整個環路的參考平面相同,避免產生信號完整性和電磁干擾等問題。

圖10 信號通過耦合電容返回驅動端

5 電磁兼容性設計

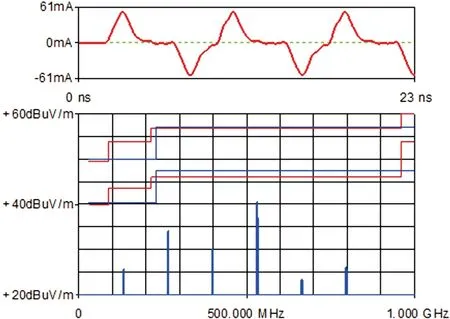

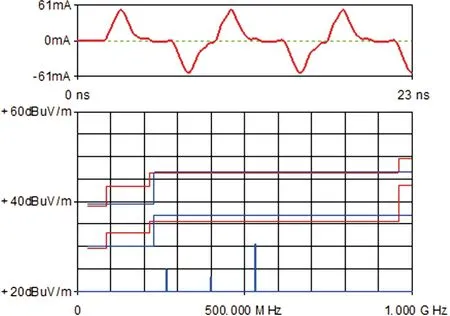

電磁輻射主要由干擾源、傳導介質和受害源三者組成。干擾源可以是自然因素,如熱噪聲和雷電噪聲等,還可能來自人為干擾,如家用電器、高頻儀器、手機和電視廣播等[10]。電磁干擾通常是以耦合的形式摻雜有用信號作為載體傳導。本文使用Hyper Lynx仿真軟件對初步設計完成的PCB做輻射強度分析。選擇系統中的關鍵信號線EBI_D4,分別設置探針位置3 m和10 m,提供220 MHz的激勵源,得到FCC和CISPR國際標準的仿真數據,如圖11和圖12所示。

圖11 信號線EBI_D4的3 m探針電磁輻射仿真分析(截圖)

圖12 信號線EBI_D4的10 m探針電磁輻射仿真分析(截圖)

6 HDMI接口PCB的設計及仿真

高速PCB設計與普通低速PCB設計不同,布線完成后,還要利用信號完整性分析軟件對整板PCB進行EMC分析和仿真,這期間會多次調整走線參數以達到改善PCB信號完整性的目的。PCB前端仿真使用的是理想傳輸線模型,一次只能對有限數量信號線進行仿真,而PCB后端仿真中的傳輸線是實際的PCB走線,摻雜了過孔、切換層次等影響特征阻抗的因素,這種情況下得到的仿真結果真實性強[11]。

6.1 蛇形等長線設計

該系統的PCB設計應該按照“高速”標準繪制,為了保證并行數據流的同步性,必須控制所有的傳輸線等長及它們的間距,然而由于布局布線空間限制,此處采用蛇形走線技術完成等長布線。蛇形線可以減小一組并行相關信號的延時,實現同組信號的等長布線,保證系統各單元通信的正確性。

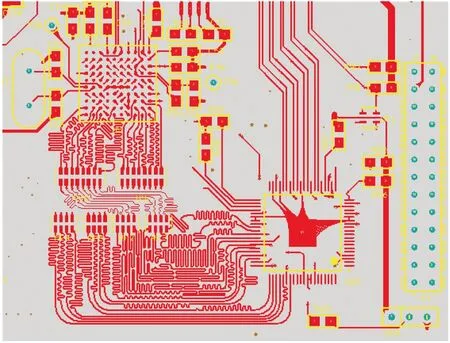

系統的關鍵走線是GV7601和SIL9030之間的并行數據線,查看手冊要求傳輸線阻抗匹配50 Ω,在二者之間各端接33 Ω的排阻消除反射、振鈴等問題。如果蛇形等長線太長,會對流動的信號產生感性作用,使信號在傳輸過程中發生相移和波動,造成接收端信號質量惡化。那么,應該怎樣確定蛇形等長線的長度呢?這里以GV7601為驅動器,以SIL9030為接收器,查看GV7601的IBIS模型,其dV/dt_r值為5.86373×101/2.82828×1010,即2.07 ns,介電常數為4.3的板材布線長度不能超過1/6×2.07×5.79=50.8 mm,經過多次修改,最終設置布線長度為31.75 mm,寬度為0.18 mm,線間距為0.38 mm。圖13所示為部分蛇形等長線。

圖13 系統蛇形等長線(截圖)

6.2 TMDS差分總線的設計

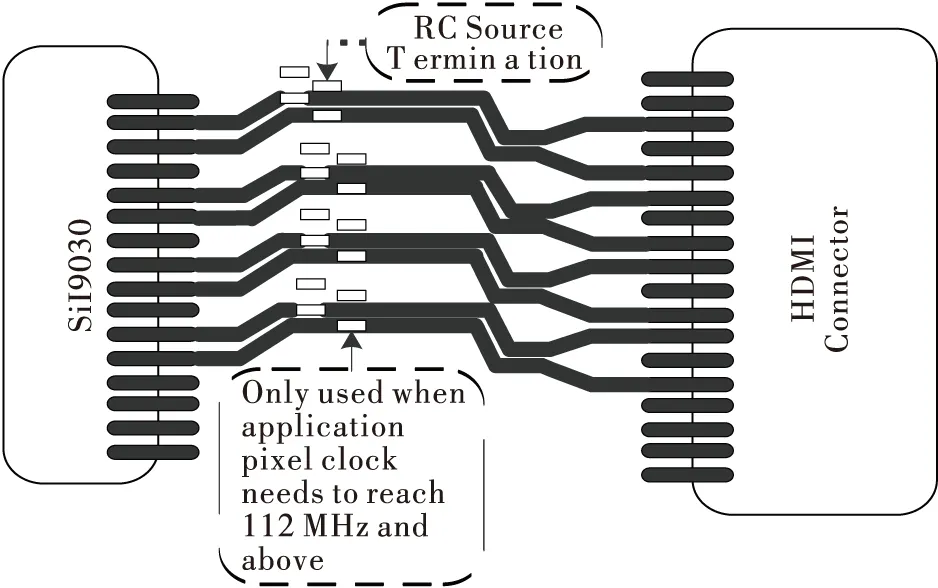

TMDS通道傳輸的是幅值相等,相位對稱的差分信號,包括編解碼數據和時鐘,接收端通過二者的差值得出邏輯“1”和“0”。對于TMDS時鐘頻率高于112 MHz的場合,為了保證信號質量,不建議使用防靜電二極管和共模電感,而是在HDMI發送端放置RC網絡[12],因為放置防靜電設備會增加TMDS數據和時鐘傳輸線的電容,導致差分阻抗不連續。圖14所示為SiL9030和HDMI接口之間的8條TMDS傳輸線,在布線過程中應避免使用過孔,同時控制100 Ω的差分阻抗。

圖14 頻率高于112 MHz時HDMI接口的布局布線

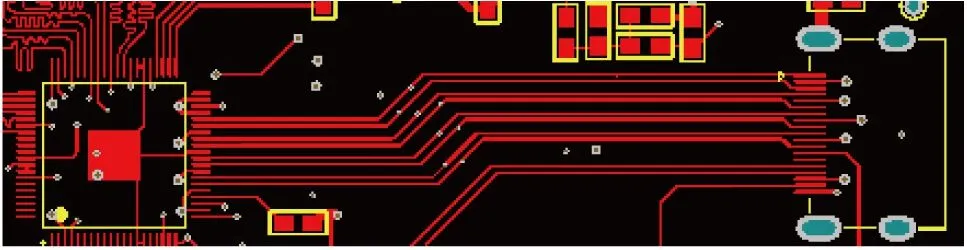

6.3 TMDS差分對耦合分析

進行PCB繪制之前,在Hyper Lynx的Line Sim建立仿真平臺,不斷修正線間距、傳輸線類型和差分對耦合長度等因素,最終設置該評估板的TMDS差分總線PCB設計的布線參數為:線寬0.15 mm,線長58.42 mm,差分對中的兩條走線間距0.2 mm且等長,4組差分對相互間隔0.26 mm,為了減少過孔效應,傳輸線采用微帶線在頂層,RC網絡對稱布局在底層。設計差分線,最基本的原則是等長和等間距。等長的目的是保持TMDS傳輸線信號的每個時刻都是同步的,消除共模干擾;等間距的目的是保證TMDS傳輸線的差分阻抗處處一致,而且兩條差分線應盡量靠近,防止產生反射。圖15所示為TMDS差分對的PCB布線。

圖15 TMDS差分對的PCB布線(截圖)

PCB布線完成并不能保證所設計的走線一定符合指標,對其進行仿真分析是必要的。選擇SIL9030的9030_TX1P和9030_TX1N差分對作為驅動端,提供112 MHz的時鐘源,在Board Sim中進行仿真,查看信號傳輸質量。

7 結束語

現如今,HDMI產品種類繁多,諸如數字機頂盒、4K超高清電視、智能教育平臺等不斷進入千家萬戶,所以產品的穩定性成為市場占有率的決定性因素。本文設計的高清HDMI音視頻評估板充分考慮了電源分布、阻抗匹配、反射、串擾等信號完整性問題,包括蛇形等長線和TMDS差分總線的設計。完成了原理圖和板級仿真驗證,能夠提高設計的成功率,對于此類產品的研發有一定的參考價值。

[1] 彭大芹,許海嘯,谷勇,等. 高速電路PCB及其電源完整性設計[J].自動化儀表,2016,37(3):5-8.

[2] 張春暉.基于PADS軟件對高速電路的設計與實現[J].電子設計工程,2013,21(22):123-125.

[3] 杜斐,田澤,許宏杰,等. 一種高效的視頻編碼系統存儲器接口的驗證[J].計算機技術與發展,2014,24(4):186-188.

[4] 李俊杰, 曹旭東, 梁華慶. 嵌入式應用系統中高速PCB設計技術的研究及實現[J]. 計算機測量與控制,2016(6):268-270.

[5] 潘磊,葛中芹,莊建軍,等. 基于FPGA的HDMI視頻流圖像處理的系統設計[J]. 實驗室研究與探索,2015,34(10):76-80.

[6] 曹世偉.高速電路中的信號完整性和電源完整性研究[D].西安:西安電子科技大學,2015.

[7] 魏曉敏.基于HDMI高速傳輸線的信號完整性分析[D].呼和浩特:內蒙古大學,2014.

[8] 鄧思維,凌凱.DDR2高速PCB設計和信號完整性分析[J].電子科技,2015,28(4):132-134.

[9] 連龍剛,徐文寬,王保成. 高速PCB設計中的EMI問題研究[J]. 電子技術應用,2015,41(3):17-19.

[10] 陳蘭兵. Cadence高速電路設計Allegro Sigrity SI/PI/EMI設計指南[M].北京:電子工業出版社,2014.

[11] 黃繼承,黃繼文,彭星波,等. 高速電路設計研究[J].通信電源技術,2015,32(6):41-44.

[12] 王雅芳.高速PCB信號完整性分析及應用[J].北京電子科技學院學報,2014,22(4):81-86.

李俊杰(1989— ),碩士生,主研電子信息與通信技術、油田測井儀器;

曹旭東(1968— ),副教授,研究生導師,主要從事DSP、SOPC、ARM等嵌入式微處理器的應用技術研究和計算機軟件系統設計及石油物探、測井儀器的研制;

梁華慶(1964— ),女,博士,教授,博士生導師,主要從事石油探測與鉆采過程的微弱信號的檢測與信息處理、電法測井數值模擬、數據反演方面的理論與方法的研究。

責任編輯:閆雯雯

Design of high-speed PCB in HDMI high definition audio and video system

LI Junjie, CAO Xudong, LIANG Huaqing, CAO Shengbiao, ZHANG Shaohua

(CollegeofGeophysicsandInformationEngineering,ChinaUniversityofPetroleum-Beijing,Beijing102249,China)

In order to eliminate the incompleteness of signals in high-speed PCB technology, there are some key issues should be solved, including timing, noise, electromagnetic and so on, in the design process of the high-speed PCB technology. In the process of high-speed PCB of HDMI high definition audio and video, the problems like crosstalk, electromagnetic interference, ringing effect and power integrity and so on are studied, and the ways to weaken or eliminate those noises are proposed. Circuit schematics and PCB are drawn by using Altium Designer, PADS software and the reliability of the front and rear parts is verified by means of Hyper Lynx and ADS simulation software. Finally, the completeness of signal through the wiring of the PCB is verified. The test results indicate that this program designed for HDMI high definition audio and video is stable, there are important references in the replacement and upgrade of smart devices and building.

high speed PCB; signal integrity; HDMI; audio and video

李俊杰,曹旭東,梁華慶,等. HDMI高清音視頻系統的高速PCB的研究及實現[J].電視技術,2016,40(12):34-39. LI J J, CAO X D, LIANG H Q,et al. Design of high-speed PCB in HDMI high definition audio and video system[J]. Video engineering,2016,40(12):34-39.

TN919

A

10.16280/j.videoe.2016.12.007

國家發改委下一代互聯網技術在智慧油田的應用示范項目(CNGI-12-03-043)

2016-06-14