基于IIC總線的串行數(shù)據(jù)通信

吳海洲

摘要:IIC總線結(jié)構(gòu)簡(jiǎn)單且易于實(shí)現(xiàn),廣泛應(yīng)用于設(shè)備或模塊間的連接。簡(jiǎn)述了IIC總線的硬件結(jié)構(gòu)和串行通信控制協(xié)議,協(xié)議規(guī)定了完整的起始狀態(tài)和讀寫時(shí)序。根據(jù)協(xié)議要求,采用控制狀態(tài)機(jī)的方式設(shè)計(jì)了一種通用的IIC接口模塊,介紹了讀寫數(shù)據(jù)過程和狀態(tài)機(jī)的轉(zhuǎn)換方式。經(jīng)過驗(yàn)證,F(xiàn)PGA與外部設(shè)備間通過IIC總線數(shù)據(jù)傳輸,響應(yīng)速度快,符合設(shè)計(jì)要求。

關(guān)鍵詞:IIC總線 FPGA 狀態(tài)機(jī)

中圖分類號(hào):TN402 文獻(xiàn)標(biāo)識(shí)碼:A 文章編號(hào):1007-9416(2016)11-0018-01

1 引言

串行總線是連接外部設(shè)備的一個(gè)串口總線標(biāo)準(zhǔn),可以簡(jiǎn)化系統(tǒng)的硬件設(shè)計(jì)、減小設(shè)備體積、提高設(shè)備的可靠性,并且易于進(jìn)行系統(tǒng)的更改和擴(kuò)充。常用的串行總線有:IIC(Inter IC BUS)總線、單總線(1-WIRE BUS)、SPI(Serial Peripheral Interface)總線及Microwire/PLUS等。由于IIC總線的連線少并且可以直接用導(dǎo)線互聯(lián)外部設(shè)備,許多半導(dǎo)體廠商都引進(jìn)了此項(xiàng)總線技術(shù),并推出了不少帶IIC總線接口的芯片或模塊。本文即論述基于FPGA的IIC總線接口,實(shí)現(xiàn)設(shè)備間的串行數(shù)據(jù)通信。

2 IIC總線簡(jiǎn)介

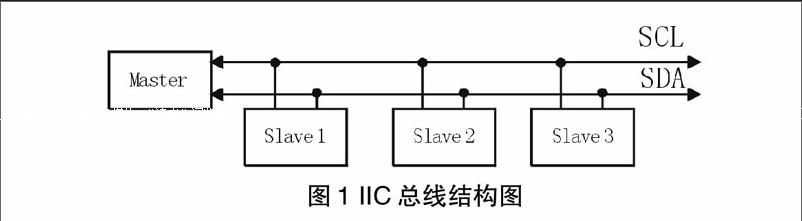

IIC總線是PHILIPS公司開發(fā)的一種簡(jiǎn)單、雙向、二進(jìn)制、同步串行總線,可解決各個(gè)設(shè)備間的串行通信[1]。物理上IIC總線只有兩根雙向信號(hào)線,分別為數(shù)據(jù)線SDA(Serial Data)和時(shí)鐘線SCL(Serial Clock)。如圖1所示。

IIC總線通過上拉電阻接正電源。總線空閑時(shí),兩根線均為高電平。總線上的任一設(shè)備輸出低電平都會(huì)使總線的信號(hào)變低,即個(gè)設(shè)備的SDA及SCL都是線“與”的關(guān)系。每一個(gè)接入IIC總線上的設(shè)備都有其在總線上的唯一地址。每一個(gè)設(shè)備都可以作為主機(jī)(Master發(fā)起通信)或是從機(jī)(Slave應(yīng)答通信)。

3 IIC總線通信控制協(xié)議

IIC通信協(xié)議是基于起止?fàn)顟B(tài)識(shí)別的[2],傳輸起始信號(hào)為在SCL為高電平時(shí)SDA出現(xiàn)一個(gè)從高到低的跳變沿,停止信號(hào)為在SCL為高電平時(shí)SDA出現(xiàn)一個(gè)從低到高的上升沿,應(yīng)答信號(hào)為SCL為高電平時(shí)SDA為低電平,非應(yīng)答信號(hào)為SCL為高電平時(shí)SDA也為高電平。正常數(shù)據(jù)傳輸bit序列時(shí),與應(yīng)答和非應(yīng)答的時(shí)序相同。在其他時(shí)刻,只有SCL為低電平時(shí),SDA才能發(fā)生變化,否則,SDA的電平需保持不變。

IIC總線的數(shù)據(jù)傳輸是以字節(jié)為單位進(jìn)行的,在一個(gè)起止?fàn)顟B(tài)之間,可傳輸若干個(gè)數(shù)據(jù)字節(jié),每個(gè)數(shù)據(jù)字節(jié)間有確認(rèn)信號(hào)。確認(rèn)信號(hào)在SDA上以每一個(gè)8bit字節(jié)后面的第9bit表示。圖2表示一個(gè)完整的IIC總線數(shù)據(jù)傳輸過程。IIC發(fā)出起始信號(hào)后,從器件發(fā)出7位尋址地址和1位讀寫標(biāo)志位R/W,當(dāng)R/W為0時(shí)表示寫狀態(tài),當(dāng)R/W為1時(shí)表示讀狀態(tài)。有應(yīng)答信號(hào)后開始傳輸數(shù)據(jù),否則就停止發(fā)送,直到發(fā)送停止信號(hào)后結(jié)束數(shù)據(jù)傳輸過程。

4 IIC接口模塊設(shè)計(jì)

本文以某FPGA及其外接設(shè)備為例,對(duì)完整的基于IIC總線的串行數(shù)據(jù)通信進(jìn)行說明。FPGA和外接設(shè)備以IIC總線進(jìn)行連接,F(xiàn)PGA為主設(shè)備,外接設(shè)備為從設(shè)備,IIC總線的控制器工作在FPGA中。IIC控制器的主要作用是發(fā)送控制命令到從設(shè)備和讀取從設(shè)備的狀態(tài)。主要包括三部分:控制狀態(tài)機(jī)、寫過程和讀過程。其中讀、寫過程的時(shí)序需遵守IIC總線通信控制協(xié)議。

寫過程:①FPGA在檢測(cè)到總線空閑時(shí),發(fā)送S信號(hào)占用總線;②FPGA給總線發(fā)送一個(gè)地址字節(jié),其中包括7位地址信號(hào)和1位寫信號(hào)(R/W信號(hào)為0);③外設(shè)檢測(cè)到總線上的地址與自己的地址相同時(shí),發(fā)送一個(gè)應(yīng)答信號(hào)ACK;④FPGA收到ACK后發(fā)送第一個(gè)數(shù)據(jù)字節(jié);⑤外設(shè)收到數(shù)據(jù)字節(jié)后發(fā)送ACK表示繼續(xù)發(fā)送或其他操作;⑥重復(fù)④、⑤,F(xiàn)PGA發(fā)送完全部的數(shù)據(jù)后發(fā)送一個(gè)停止位P,結(jié)束寫過程并釋放總線。

讀過程:①FPGA在檢測(cè)到總線空閑時(shí),發(fā)送S信號(hào)占用總線;②FPGA給總線發(fā)送一個(gè)地址字節(jié),其中包括7位地址信號(hào)和1位寫信號(hào)(R/W信號(hào)為1);③外設(shè)檢測(cè)到總線上的地址與自己的地址相同時(shí),發(fā)送一個(gè)應(yīng)答信號(hào)ACK;④FPGA收到ACK后釋放總線,開始接收第一個(gè)數(shù)據(jù)字節(jié);⑤外設(shè)收到數(shù)據(jù)字節(jié)后發(fā)送ACK表示繼續(xù)發(fā)送或其他操作;⑥重復(fù)④、⑤,F(xiàn)PGA接收完全部的數(shù)據(jù)后發(fā)送一個(gè)停止位P,結(jié)束寫過程并釋放總線。

控制狀態(tài)機(jī):根據(jù)IIC總線通信控制協(xié)議克制,IIC總線有六個(gè)固定的狀態(tài),分別為:空閑(Idle)、開始(Start)、寫數(shù)據(jù)(Write)、讀數(shù)據(jù)(Read)、應(yīng)答(ACK)停止(Stop)。如圖3所示。

①空閑狀態(tài):當(dāng)無(wú)數(shù)據(jù)傳輸時(shí), IIC總線處于空閑狀態(tài);②起始狀態(tài):當(dāng)收到開始信號(hào)后占用總線,轉(zhuǎn)入讀、寫數(shù)據(jù)狀態(tài);③寫數(shù)據(jù)狀態(tài):串行數(shù)據(jù)傳輸寫入外設(shè),完成后進(jìn)入應(yīng)答狀態(tài);④讀數(shù)據(jù)狀態(tài):FPGA讀取總線上的串行數(shù)據(jù),完成后進(jìn)入應(yīng)答狀態(tài);⑤應(yīng)答狀態(tài):根據(jù)外設(shè)的響應(yīng)情況轉(zhuǎn)入停止?fàn)顟B(tài)或空閑狀態(tài);⑥停止?fàn)顟B(tài):數(shù)據(jù)傳輸結(jié)束,釋放總線,轉(zhuǎn)入空閑狀態(tài)。

5 FPGA原型驗(yàn)證

本設(shè)計(jì)選用的FPGA是ALTERA公司的FPGA產(chǎn)品EP3C80F780I7N,采用Verilog語(yǔ)言描述[3],在Quartus II平臺(tái)上完成了系統(tǒng)的仿真、綜合、映射、布局等。在仿真結(jié)果正確后,通過編程器下載到FPGA中進(jìn)行系統(tǒng)調(diào)試。該模塊性能穩(wěn)定,響應(yīng)速度快,完成了基于IIC總線協(xié)議的串行數(shù)據(jù)通信,符合設(shè)計(jì)要求。

6 結(jié)語(yǔ)

本文介紹了一種基于FPGA的IIC總線串行數(shù)據(jù)通信方法,用控制狀態(tài)機(jī)的模式,采用Verilog語(yǔ)言設(shè)計(jì)完成了IIC總線控制模塊,并進(jìn)行了FPGA硬件驗(yàn)證,結(jié)果表明本設(shè)計(jì)滿足IIC總線通信控制協(xié)議,設(shè)計(jì)簡(jiǎn)單,易于實(shí)現(xiàn)。

參考文獻(xiàn)

[1]Philips Semiconductors. The IIC- Bus Specification[M] Version2.1,2001:6-19.

[2]董秀潔,王莉萍.基于FPGA的IIC總線控制器設(shè)計(jì)[J].中原工學(xué)院報(bào),2014,25(1):11-14.

[3]朱誠(chéng)誠(chéng),石晶晶,陳斯,張萌.基于Verilog HDL的IIC總線IP設(shè)計(jì)[J].電子器件,2015,38(6)1336-1340.