基于USB 3.0接口的高速數(shù)據(jù)傳輸系統(tǒng)設(shè)計

宋中喆+裴東興+楊少博

摘 要: 針對目前存儲測試系統(tǒng)中存有的數(shù)據(jù)傳輸慢,經(jīng)常出現(xiàn)錯誤的顯著問題,設(shè)計基于USB 3.0接口的高速數(shù)據(jù)傳輸系統(tǒng)。該設(shè)計以FPGA作為主控芯片,采用負延遲與乒乓緩存的方式將A/D轉(zhuǎn)換的數(shù)據(jù)高速緩存到DDR2 SDRAM中。設(shè)計了GPIF Ⅱ 通用可編程接口和手動 DMA 通道,實現(xiàn)了USB 3.0同步從FIFO模式的高速數(shù)據(jù)傳輸。系統(tǒng)分析測試和實驗結(jié)果表明,該系統(tǒng)實現(xiàn)了數(shù)據(jù)的高速可靠傳輸,能有效解決大容量數(shù)據(jù)采集后的數(shù)據(jù)高速傳輸問題。

關(guān)鍵詞: 存儲測試; USB 3.0接口; 高速數(shù)據(jù)傳輸; 負延遲; 乒乓緩存

中圖分類號: TN919.6?34; TP334.7 文獻標識碼: A 文章編號: 1004?373X(2017)04?0159?04

Design of high?speed data transmission system based on USB 3.0 interface

SONG Zhongzhe1,2, PEI Dongxing1,2, YANG Shaobo1,2

(1. National Key Laboratory for Electronic Measurement Technology, North University of China, Taiyuan 030051, China;

2. MOE Key Laboratory of Instrumentation Science and Dynamic Measurement, North University of China, Taiyuan 030051, China)

Abstract: Since the current memory test system has the prominent problems of low data transmission speed and frequent fault occurrence, a high?speed data transmission system based on USB 3.0 interface was designed. The FPGA is taken as the main control chip of the design. The modes of negative delay and Ping?Pong cache are adopted to cache the data transformed through A/D into the DDR2 SDRAM with high speed. The general programming interface GPIF II and manual DMA channel were designed to realize the high?speed data transmission based on USB 3.0 synchronous slave FIFO mode. The system analysis, test and experimental results show that the system has realized the high?speed and reliable data transmission, and can effectively solve the high?speed data transmission problem occurring after large?capacity data acquisition.

Keywords: memory testing; USB 3.0 interface; high?speed data transmission; negative delay; Ping?Pong cache

0 引 言

隨著當前存儲測試系統(tǒng)[1]中存儲容量的急劇增加,對數(shù)據(jù)的傳輸速度的要求隨之也越來越高,此外在某些需要對數(shù)據(jù)進行實時傳輸處理的場合,人們對數(shù)據(jù)傳輸系統(tǒng)的速度要求也越來越嚴格[2]。本實驗室以前一直在使用USB 2.0接口作為存儲測試系統(tǒng)的數(shù)據(jù)傳輸接口,但受限于其理論最大480 Mb/s的傳輸速度,現(xiàn)在已逐漸難以滿足數(shù)據(jù)傳輸?shù)囊蟆P乱淮?USB 3.0繼承了 USB 2.0 的所有優(yōu)勢,能夠向下兼容 USB 2.0,且在USB 2.0的基礎(chǔ)上新增了超速傳輸模式,理論傳輸速度[3?4]可高達 5 Gb/s。并且在固件程序開發(fā)、電源管理等方面有了更好的提高。故而USB 3.0接口可以很好地解決那些問題。在未來的幾年內(nèi),USB 3.0 必定能夠較好地應(yīng)對數(shù)字時代要求的高速性能和可靠互聯(lián)性[5]。

1 系統(tǒng)總體方案設(shè)計

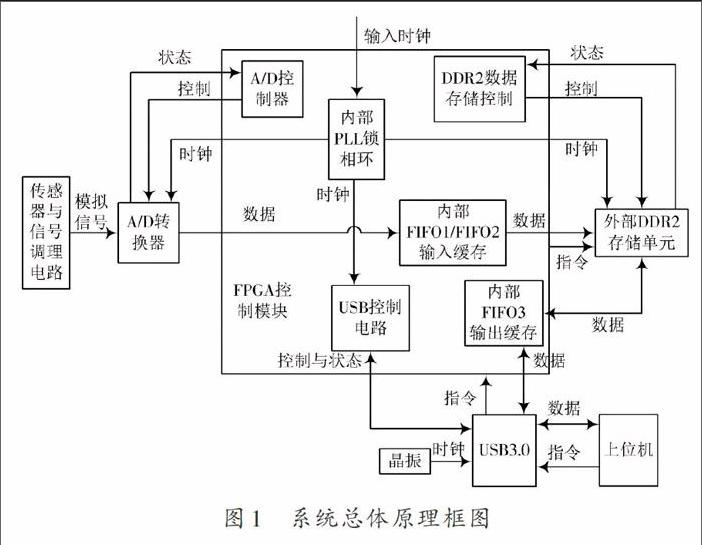

本文設(shè)計的系統(tǒng)主要包含五部分:傳感器與信號調(diào)理電路、ADC數(shù)據(jù)轉(zhuǎn)換電路、DDR2數(shù)據(jù)存儲單元、FPGA控制電路和USB 3.0數(shù)據(jù)傳輸接口。圖1為系統(tǒng)的總體原理框圖。傳感器將需要測量的物理量轉(zhuǎn)換為相應(yīng)的模擬電信號,信號調(diào)理電路用來將傳感器輸出的微弱模擬信號進行放大濾波等處理[6]。ADC數(shù)據(jù)轉(zhuǎn)換電路將經(jīng)過調(diào)理通道的采樣模擬信號轉(zhuǎn)換為數(shù)字信號。DDR2數(shù)據(jù)存儲單元用來按所接收的指令來對數(shù)據(jù)進行高速緩存。數(shù)據(jù)轉(zhuǎn)換和存儲的操作在FPGA控制單元的控制下進行,在FPGA內(nèi)部構(gòu)建有PLL鎖相環(huán),用來對輸入時鐘進行頻率轉(zhuǎn)換,并將不同的輸出時鐘提供給A/D轉(zhuǎn)換器、DDR2及USB 3.0控制電路。USB 3.0接口電路傳輸上位機指令,F(xiàn)PGA接收指令并對其解碼,然后將FIFO中緩存的數(shù)據(jù)傳輸至上位機[7]。

2 硬件及實現(xiàn)原理

2.1 系統(tǒng)芯片選型

對于FPGA芯片的選擇,本文采用Altera公司的低成本Cyclone Ⅲ系列 EP3C16F484芯片來作為系統(tǒng)的控制中心。該芯片內(nèi)部包含較多的RAM容量,利用IP核可以搭建自己所需要的電路模塊,如FIFO緩存模塊,PLL鎖相環(huán)等。USB 3.0接口協(xié)議芯片采用Cypress公司的CYUSB3014,DDR2 SDRAM選用MT47H64M16HR。

2.2 FPGA與DDR2存儲接口設(shè)計

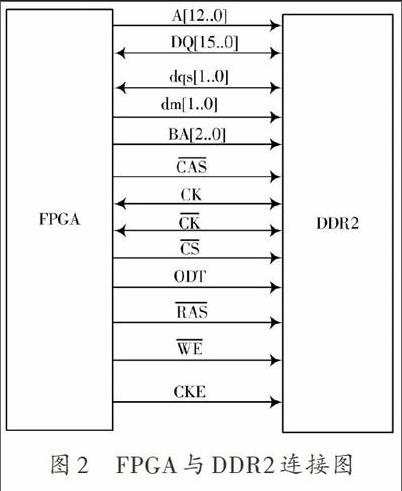

在實際應(yīng)用中為防止有效數(shù)據(jù)在FIFO中累積而造成數(shù)據(jù)丟失,故設(shè)計了DDR2數(shù)據(jù)緩存模塊,用來對海量的數(shù)據(jù)進行緩存。圖2為FPGA與DDR2連接圖。DDR2 能夠以內(nèi)部控制總線4倍的速度運行,還能夠以外部總線的4倍的速度進行讀/寫操作。DDR2 協(xié)議包括很多用戶命令,如存儲器初始化、讀/寫命令和自動刷新等。為確保 DDR2能夠在正常情況下工作,對這些命令的時序,以及命令間的順序及間隔都有著特別嚴格的要求。FPGA內(nèi)部有集成的高性能 DDR2 控制器內(nèi)核,直接調(diào)用該模塊,即可較方便地實現(xiàn)對數(shù)據(jù)的讀/寫操作。

2.3 FPGA與USB3.0通信接口設(shè)計

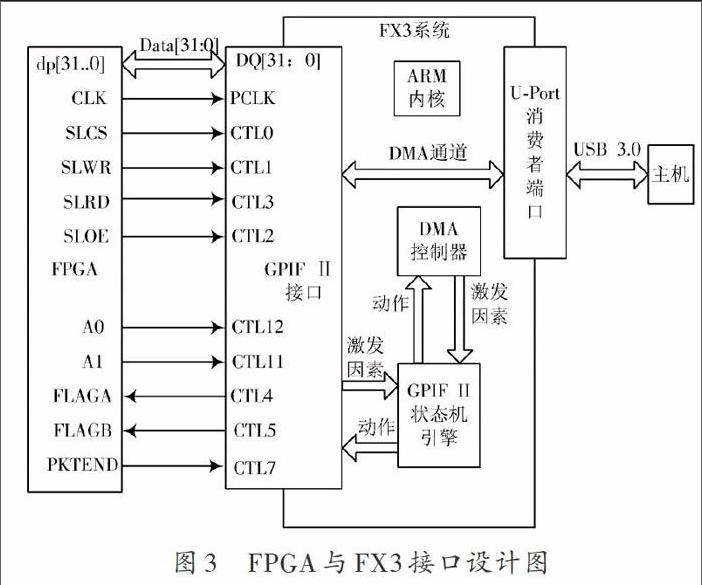

圖3為FPGA與FX3的接口設(shè)計圖。本系統(tǒng)將 GPIF Ⅱ(通用可編程接口)配置為32位的同步從FIFO 模式,GPIF Ⅱ的32位DQ數(shù)據(jù)總線與FPG相應(yīng)的32位數(shù)據(jù)端口相連,在 FX3 系統(tǒng)內(nèi)部,GPIF Ⅱ沒有直接與 USB端口緩沖區(qū)相連,而是直接連接到FX3的內(nèi)部 DMA網(wǎng)絡(luò)。FLAGA和FLAGB為CYUSB3014的狀態(tài)標志信號,用來反饋給外部主控制器 FPGA。PCLK與FPGA的CLK相連,用來接收時鐘信號。此外,SLCS為片選,SLWR為寫使能,SLOE為輸出使能,SLRD為讀使能,PKTEND為短包發(fā)送信號,均在低電平時被激活,A[1:0]為線程地址選擇信號。GPIF Ⅱ的端口操作和控制信號由內(nèi)部可編程的狀態(tài)機引擎控制,外部處理器通過配置輸入到FX3的控制信號來控制狀態(tài)機的操作[8]。

3 系統(tǒng)程序設(shè)計

3.1 A/D采集與數(shù)據(jù)緩存流程

本設(shè)計主要完成從系統(tǒng)上電開始,A/D采樣輸入/輸出信號到采樣數(shù)據(jù)存儲工作。主要包括系統(tǒng)初始化、A/D采樣控制、未觸發(fā)前的FIFO循環(huán)寫、觸發(fā)后的雙FIFO乒乓存儲操作。首先系統(tǒng)上電后,初始化A/D進行數(shù)據(jù)采集,此過程采用負延遲的方式,即有效的觸發(fā)信號還沒有到來,輸入FIFO1進行循環(huán)采樣,由于FIFO容量有限,存儲的數(shù)據(jù)會不斷刷新,每一時刻所存儲到的數(shù)據(jù)都是此段時間內(nèi)最新采樣到的數(shù)據(jù)。一旦觸發(fā)信號到來,F(xiàn)IFO1和 FIFO2都有效,此時進行雙FIFO乒乓存儲操作。圖4為A/D采集與數(shù)據(jù)緩存流程圖。

觸發(fā)到來后,第一步將最初FIFO1中緩存的數(shù)據(jù)首先讀出寫入DDR2,同時將觸發(fā)后A/D輸出數(shù)據(jù)寫入 FIFO2中;第二步將第一步中FIFO2緩存的數(shù)據(jù)寫入 DDR2,于此同時將 A/D 輸出數(shù)據(jù)寫入FIFO1中;第三步將第二步中FIFO1緩存的數(shù)據(jù)寫入DDR2,于此同時將A/D觸發(fā)后輸出數(shù)據(jù)寫入 FIFO2 中,依此循環(huán),這樣通過兩個 FIFO 按節(jié)拍的讀寫,將數(shù)據(jù)流無間斷地送入DDR2中[9]。直到系統(tǒng)停止采樣信號到來時,此過程結(jié)束。圖5為乒乓緩存操作圖。

3.2 USB 3.0程序設(shè)計

采集后的數(shù)據(jù)通過 USB 3.0 接口傳輸至上位機進行處理分析,F(xiàn)X3器件有一個內(nèi)部DMA結(jié)構(gòu),用來將GPIF Ⅱ接口連接至系統(tǒng)內(nèi)部存儲器和其他串行外設(shè)。在FX3上運行的固件將該數(shù)據(jù)路徑連接至合適的數(shù)據(jù)源,或連接至數(shù)據(jù)接收器[10]。圖6為高速讀寫數(shù)據(jù)的DMA通道設(shè)計圖。

套接字是外設(shè)硬件模塊和FX3 RAM間的連接點,GPIFⅡ 一側(cè)的套接字相當于端點[11],GPIF 線程是位于GPIF Ⅱ模塊內(nèi)專用的數(shù)據(jù)路徑,用來將外部數(shù)據(jù)引腳同套接字連接起來。本設(shè)計使用由兩位地址線 A[1:0] 決定的四個GPIF線程中的兩個,采用套接字和GPIF線程的默認的對應(yīng)關(guān)系:套接字1與線程1相對應(yīng),套接字0與線程0相連。線程的切換是通過FPGA控制GPIF Ⅱ接口上的地址信號A[1:0] 來實現(xiàn)的,當A[1:0]=0時,轉(zhuǎn)到線程0,為1時則對應(yīng)線程1。

固件程序中設(shè)置DMA通道時,本設(shè)計采用手動DMA通道,相比自動DMA通道,手動DMA通道允許固件管理和控制數(shù)據(jù)流,從而確保數(shù)據(jù)的可靠傳輸。將兩組共32個緩沖器分配到特定的輸入或輸出DMA通道上,每個緩沖器的大小根據(jù)USB的速度而被定義:全速模式時為64 B,高速時則為512 B,超速時設(shè)為1 024 B。創(chuàng)建手動DMA通道時,首先設(shè)置DMA的大小,然后設(shè)置從設(shè)備DMA緩存計數(shù),接著配置DMA的生產(chǎn)者和消費者套接字,最后指定DMA通道類型。

3.3 FPGA與USB 3.0通信程序設(shè)計

此部分主要完成FPGA與GPIF Ⅱ接口進行通信的設(shè)計。由于本設(shè)計中 DDR2的輸出數(shù)據(jù)位寬為16 b,而GPIF Ⅱ接口采用32 b,故在FPGA中還設(shè)計了輸出緩存FIFO,用來匹配不同寬度的數(shù)據(jù)接口。

在 GPIF Ⅱ Designer中,將FLAGA配置為Current_thread_DMA_RDY,F(xiàn)LAGB 配置為Current_thread_

DMA_watermark,兩者都設(shè)為低電平有效,故當其為低電平時,它們指示滿/空或一部分滿/一部分空狀態(tài)。 本文外部FPGA通過從設(shè)備 FIFO 對 FX3 進行突發(fā)寫入傳輸,圖7為32 b數(shù)據(jù)總線寬度的突發(fā)寫入傳輸邏輯分析器截圖。在突發(fā)模式下,在整個突發(fā)寫入過程中保持激活狀態(tài)。在突發(fā)寫入模式下,令A(yù)[1:0]=0,GPIF Ⅱ狀態(tài)機控制切換到線程0,數(shù)據(jù)被接入作為生產(chǎn)者的套接字0,然后當寫使能信號SLWR有效時,來自外部的數(shù)據(jù)先被寫入位于系統(tǒng)內(nèi)存的DMA緩沖區(qū)的第一個緩沖器Buffer0,接著每當 PCLK 的上升沿到來時,都會將數(shù)據(jù)總線上的值寫入到FX3的Buffer0內(nèi),當Buffer0狀態(tài)滿后,F(xiàn)LAGA反饋信號將被拉低,用來表明其滿狀態(tài)。此時FX3 CPU 即會接收到一個由GPIF Ⅱ 套接字發(fā)送的中斷,來通知至此已填充了DMA 緩沖區(qū),F(xiàn)X3 的CPU可將此信息發(fā)給USB套接字。此過程后調(diào)用的回調(diào)函數(shù)清空DMA 緩沖區(qū),F(xiàn)LAGA狀態(tài)標志重新變?yōu)楦唠娖剑缓笙M端點將數(shù)據(jù)上傳給上位機,接著USB套接字發(fā)送一個中斷給FX3 CPU,來告知USB套接字已經(jīng)清空了DMA 緩沖區(qū),至此DMA通道即可轉(zhuǎn)到第二個緩沖器。外部FPGA主設(shè)備必須監(jiān)控FLAGA,以確定何時完成切換操作,以及何時可同下一個緩沖區(qū)進行數(shù)據(jù)訪問。

在FX3的固件程序的 cyfxslfifo.c 文件中,添加一個CyU3PgpifSocketConfigure() API 調(diào)用,以指定水印值,水印值決定何時激活局部標志FLAGB。圖7中,F(xiàn)LAGB在寫入最后數(shù)據(jù)字的同一個周期內(nèi)轉(zhuǎn)為低電平。

4 系統(tǒng)測試

在完成了系統(tǒng)的設(shè)計后對系統(tǒng)進行數(shù)據(jù)傳輸性能測試。首先通過信號發(fā)生器來代替?zhèn)鞲衅髋c信號調(diào)理電路輸入模擬鋸齒波信號給ADC,圖8為實驗室某上位機記錄儀通過USB 3.0接口接收到的鋸齒波數(shù)據(jù)。由圖8知波形與信號發(fā)生器的輸出一致,表明數(shù)據(jù)傳輸正確。

圖9為利用Cypress 公司streamer軟件進行測試系統(tǒng)的傳輸速度,本系統(tǒng)的測試速度達到了252 900 KB/s,即247.0 MB/s的超高速度,相比于先前使用的USB 2.0接口的速度,有了非常明顯的提高,并且整個傳輸過程沒有錯誤出現(xiàn)。

5 結(jié) 語

本文設(shè)計了基于USB 3.0同步從FIFO模式的高速數(shù)據(jù)傳輸系統(tǒng),采用FPGA作為整個系統(tǒng)主控芯片,借助其非常高效的并行處理能力,并與A/D轉(zhuǎn)換模塊、DDR2數(shù)據(jù)緩存模塊及USB 3.0通信模塊相結(jié)合,使得數(shù)據(jù)的采集、轉(zhuǎn)換、存儲和傳輸能夠協(xié)調(diào)進行,達到了數(shù)據(jù)采集后的的高速傳輸?shù)囊蟆=?jīng)過多次傳輸測試,表明該系統(tǒng)的傳輸速度可達247.0 MB/s,而且系統(tǒng)非常穩(wěn)定,不會出現(xiàn)數(shù)據(jù)丟失,能夠可靠完成數(shù)據(jù)的高速傳輸。

參考文獻

[1] 張文棟.存儲測試系統(tǒng)的設(shè)計理論及其應(yīng)用[M].北京:高等教育出版社,2002:34?40.

[2] 岳孝忠,裴東興,王健.基于USB 3.0接口高速數(shù)據(jù)采集系統(tǒng)的設(shè)計[J].電子器件,2015(1):140?143.

[3] 朱耀麟,馬慧銘.USB 3.0超高速多串口傳輸系統(tǒng)的設(shè)計[J].電子技術(shù)應(yīng)用,2013(9):129?131.

[4] Hewlett?Packard Company, Intel Corporation, Microsoft Corporation, et al. Universal serial bus 3.0 specification [R]. USA:Alan Berkema, 2011: 45?57.

[5] 蘆艷芳,郭林.USB 3.0兼容性與電源分配方案[J].電腦知識與技術(shù),2010(27):7649?7650.

[6] 馬青.高速數(shù)據(jù)采集信號調(diào)理電路的研究[D].哈爾濱:哈爾濱理工大學,2009.

[7] 柯艷,李杰,孔祥雷,等.基于USB 2.0的多路數(shù)據(jù)采集系統(tǒng)上位機軟件設(shè)計[J].測試技術(shù)學報,2010(4):351?356.

[8] Cypress Semiconductor. EZ?USB FX3 technical reference manual [R]. USA:San Jose, 2011: 125?170.

[9] 楊世錫,梁文軍,于保華.振動信號多通道同步整周期數(shù)據(jù)采集卡設(shè)計[J].振動、測試與診斷,2013,33(1):23?28.

[10] Cypress Semiconductor. FX3 programmers manual [R]. USA: San Jose, 2011:39?49.

[11] 楊少博,裴東興,岳孝忠.高速數(shù)據(jù)采集系統(tǒng)中USB 3.0數(shù)據(jù)傳輸接口設(shè)計[J].電子器件,2015(4):912?916.