FPGA與88E1111的千兆以太網接口設計

朱明輝,司斌,張從霞,張鵬

(中國空空導彈研究院,洛陽 471009)

FPGA與88E1111的千兆以太網接口設計

朱明輝,司斌,張從霞,張鵬

(中國空空導彈研究院,洛陽 471009)

為實現設備間數據的以太網傳輸,對TCP/IP協議進行深入了研究,設計了基于FPGA和PHY物理層芯片88E1111的千兆以太網數據傳輸系統。系統采用硬件描述語言實現以太網傳輸協議,并利用Xilinx提供的MAC以太網控制器 IP核完成幀校驗和封裝,物理層實現采用88E1111芯片。結合系統設計需求對TCP/IP以太網數據協議進行裁剪,僅保留UDP協議、IP協議和ARP地址解析協議。經測試,千兆以太網能夠穩定、高效地實現數據傳輸。

FPGA;千兆以太網;UDP;IP;ARP

引 言

隨著導彈測試設備向智能化、模塊化的方向發展,模塊之間的數據通信已成為一個重要課題。目前測試設備內各模塊之間數據傳輸主要采用并行總線和串行總線兩種方式[1],高數據傳輸常采用PCI、PXI和CPCI等并行總線,并行總線設計復雜并且不適合遠距離傳輸。串行總線RS485、RS232、CAN等雖然設計簡單、傳輸距離較遠,但數據速率一般不是很高。隨著以太網技術的發展,數據傳輸速率可以達到10 Mb/s、100 Mb/s、1 Gb/s、10 Gb/s,并且端到端的數據傳輸可達100 m,利用路由器或現有Internet網絡實現更遠距離傳輸,通過網口能夠方便地與計算機PC進行通信,所以研究嵌入式以太網數據傳輸的實現具有重要意義。

目前嵌入式以太網的實現方案眾多,根據以太網傳輸協議實現方式的不同大致可分為三種類型:第一種采用軟件代碼實現的以太網傳輸協議,如在ARM、DSP等微處理器上利用軟件代碼實現網絡協議[2-3],這種方式可以很方便地移植開源代碼的以太網協議棧,但受限于微處理的采用串行指令的運行方式導致數據處理能力、網絡傳輸速率不高;第二種采用內部集成以太網協議的ASIC實現[4],只需要處理器對專用芯片進行簡單控制,便可實現數據的以太網發送和接收,不再需要用戶編寫TCP/IP協議,降低了處理器的資源消耗,用戶設計難度,但設計不夠靈活且會增加電路設計的復雜度;第三種是在FPGA上采用硬件描述語言實現以太網協議[5-6],這種方式依靠FPGA豐富的邏輯資源和強大的數據處理能力,克服了微處理器處理能力差的缺點,并且使用硬件描述語言可以很方便地實現協議的升級和維護,彌補了ASIC設計不夠靈活的缺點。

本文采用FPGA和物理層芯片88E1111芯片實現嵌入式千兆以太網數據傳輸系統設計,根據需求對TCP/IP協議進行裁剪,降低了資源消耗及設計難度,經測試傳輸系統夠穩定、高效地實現數據傳輸。

1 千兆以太網傳輸系統總體設計

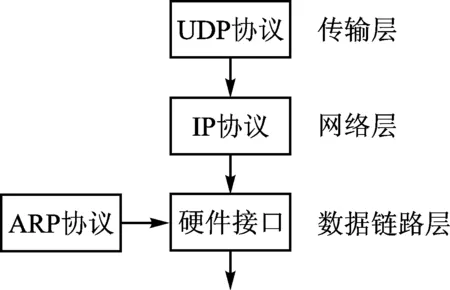

千兆以太網數據傳輸系統采用目前主流的TCP/IP協議,完整的TCP/IP協議是一個龐大的協議簇,完全實現不僅會消耗大量的FPGA資源,同時會增加設計及維護難度。作為嵌入式的使用應根據系統需求對其進行裁剪。考慮到系統高速數據傳輸、高實時性的要求,所以傳輸層僅保留具有較傳輸效率的非面向連接的UDP協議[9]。同時為了與上位機之間能夠實現點對點數據傳輸,在UDP幀發送前需要知道對方物理地址MAC,所以保留數據鏈路層的ARP地址解析協議。裁剪后的協議棧如圖1所示,傳輸層采用UDP協議,網絡層采用IP協議,數據鏈路層采用ARP協議和MAC協議。

圖1 裁剪后的TCP/IP協議棧結構

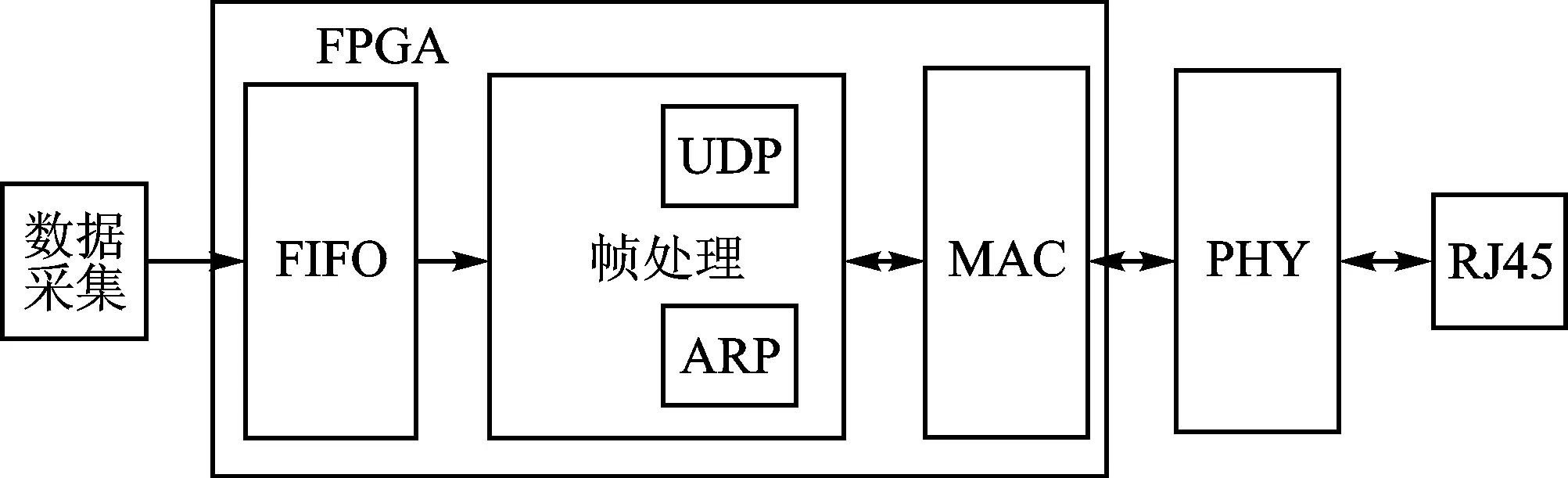

千兆以太網數據傳輸系統的總體結構如圖2所示,千兆以太網數據傳輸系統主要包括:數據采集模塊、數據緩存FIFO、協議處理模塊、MAC控制器IP核和物理層PHY模塊。

圖2 千兆以太網數據傳輸系統的總體結構

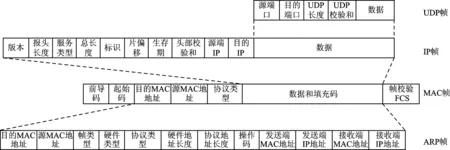

數據采集模塊根據FPGA指令完成數據的采集,并將采集的數據發送至FPGA的FIFO緩存模塊。FIFO主要實現采集數據的緩存,供幀處理模塊發送數據使用。幀處理模塊采用硬件描述語言Verilog HDL編寫,在發送數據時按照圖3所示的幀格式,對發送數據逐層加上幀頭以完成幀封裝,并將其發送至MAC控制器。幀接收是幀發送的逆過程,首先對MAC控制器接收幀類型判斷,然后按照不同的協議完成幀的解析并提取幀攜帶的有用信息。

圖3 UDP和ARP幀封裝格式

MAC控制器采用Xilinx官方提供的IP核,設定速率為1000 Mbps,物理層接口為GMII模式[10]。在幀發送時,MAC控制器為發送幀添加前導碼、起始碼、補碼和FCS校驗碼,然后將MAC幀通過GMII總線口發送至物理層芯片PHY。在幀接收時,MAC控制模塊通過GMII總線接口接收物理層PHY芯片發來的數據,對接收到的幀完成CRC校驗,將前導碼、起始碼、補碼和FCS校驗碼去除后送給上層的幀接收模塊。

物理層的實現采用Marvell公司的88E1111 PHY芯片,88E1111支持10M/100M/1000 Mbps三種速率,與MAC層接口有RGMII、SGMII、GMII等類型[11]。在千兆以太網數據傳輸系統設計時,通過CONFIG[3:0]引腳配置88E1111芯片接口類型為GMII模式。在幀發送時,88E1111通過GMII接口從MAC控制器接收幀數據,進行編碼后通過網絡變壓器發送至RJ45網口。在幀接收時,PHY芯片首先完成對接收數據的解碼,然后將接收到的數據通過GMII口發送至MAC控制器。

2 FPGA邏輯設計

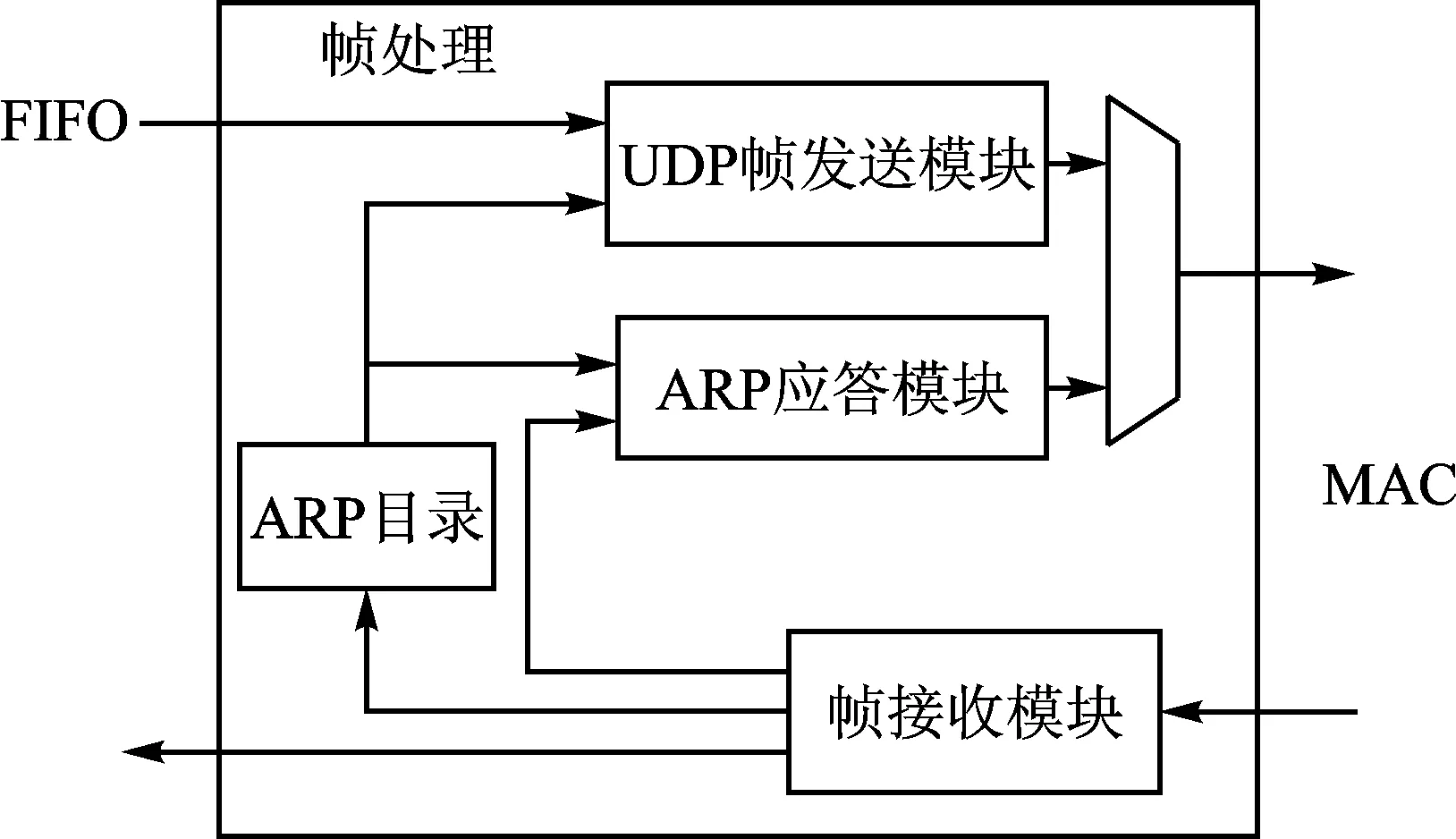

在FPGA邏輯設計中,以太網協議的實現是系統的核心部分,本部分重點介紹UDP幀的發送接收、ARP請求的接收和應答幀發送的邏輯設計。幀處理模塊的結構如圖4所示。

圖4 FPGA幀處理模塊

幀處理模塊主要包括UDP幀發送模塊、ARP應答模塊和幀接收模塊。當幀接收模塊收到MAC控制器發來的數據后,接收模塊根據不同的幀類型提取有用信息并做出相應處理。若收到的為ARP請求幀,則使能ARP應答幀發送模塊,將本地MAC地址告訴上位機。若收到包含數據發送命令的UDP幀,則將FIFO中的采集數據按照圖3幀格式逐層進行幀封裝并完成發送。

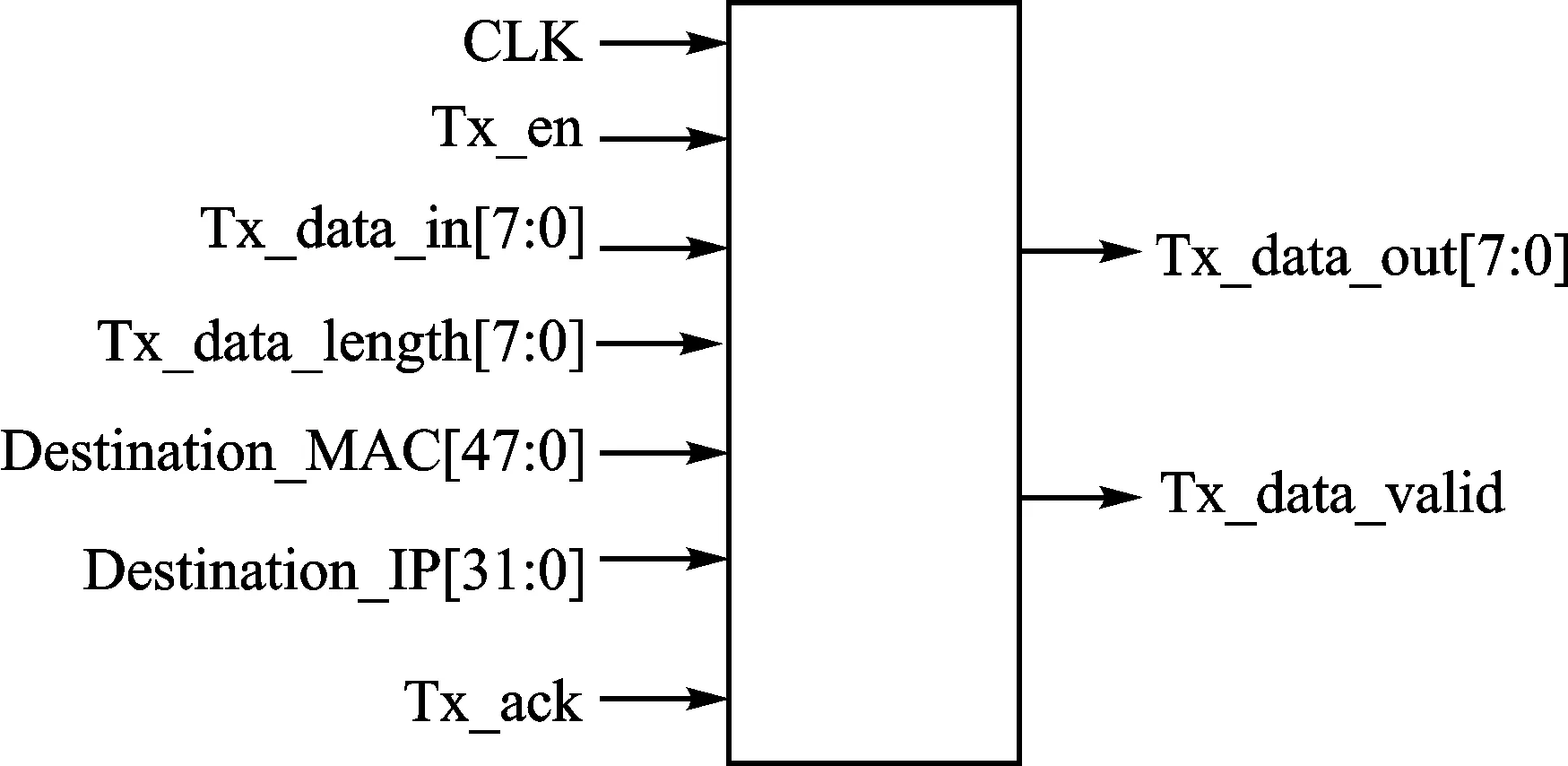

2.1 UDP幀發送模塊設計

UDP幀發送模塊主要完成對發送數據的UDP和IP封裝并發送至MAC控制器。UDP幀發送模塊如圖5所示,Tx_data_in[7:0]為來自FIFO的數據輸入口, Tx_data_length[15:0]為發送數據長度輸入口, Destination_MAC和Destination_IP為目的地址輸入口,Tx_ack為MAC控制器空閑標志位。Tx_data_out[7:0]為封裝完成的幀的輸出口。為了降低端口數量和設計復雜度、提高可維護度,對于每幀中都相同的數據如源MAC、源IP地址、協議、版本等通過參數parameter進行設定。

圖5 UDP幀發送模塊

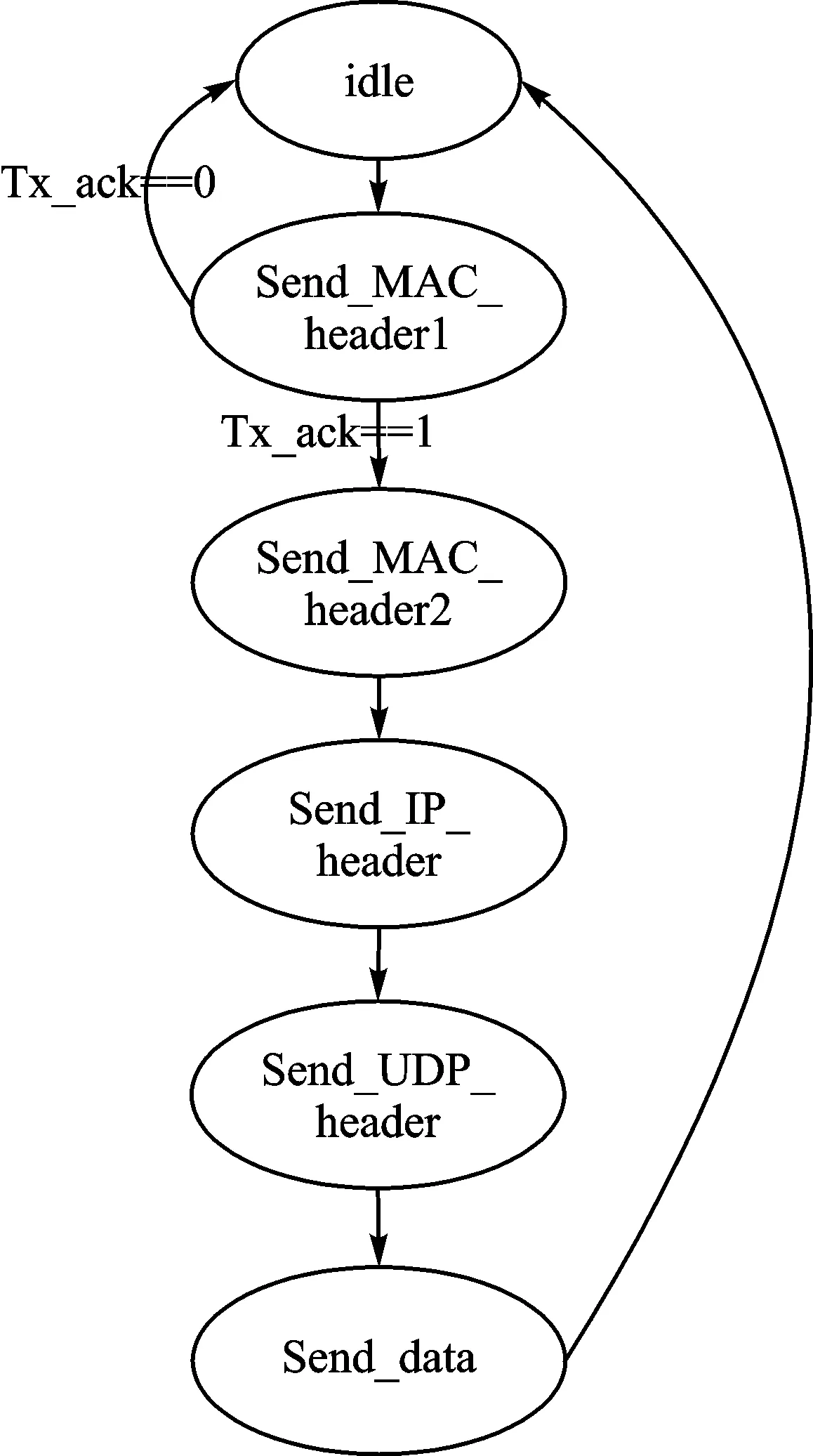

圖6 UDP幀發送狀態流程圖

UDP幀發送模塊的發送數據的狀態流程如圖6所示,當發送模塊的Tx_en輸入使能后,進入Send_MAC_header1狀態首先發送MAC幀頭的第一個字節,然后檢查來自MAC控制器的Tx_ack信號,若Tx_ack為0,說明MAC控制器忙,則返回idle。若Tx_ack為1,則依次完成MAC幀首部、IP幀首部、UDP首部發送。當完成所有幀首部發送后,從FIFO讀入要發送的數據,每讀入一個數據,cnt加1,當cnt等于發送數據長度(Tx_data_length-1)時,說明發送數據已封裝完成,則返回到idle。

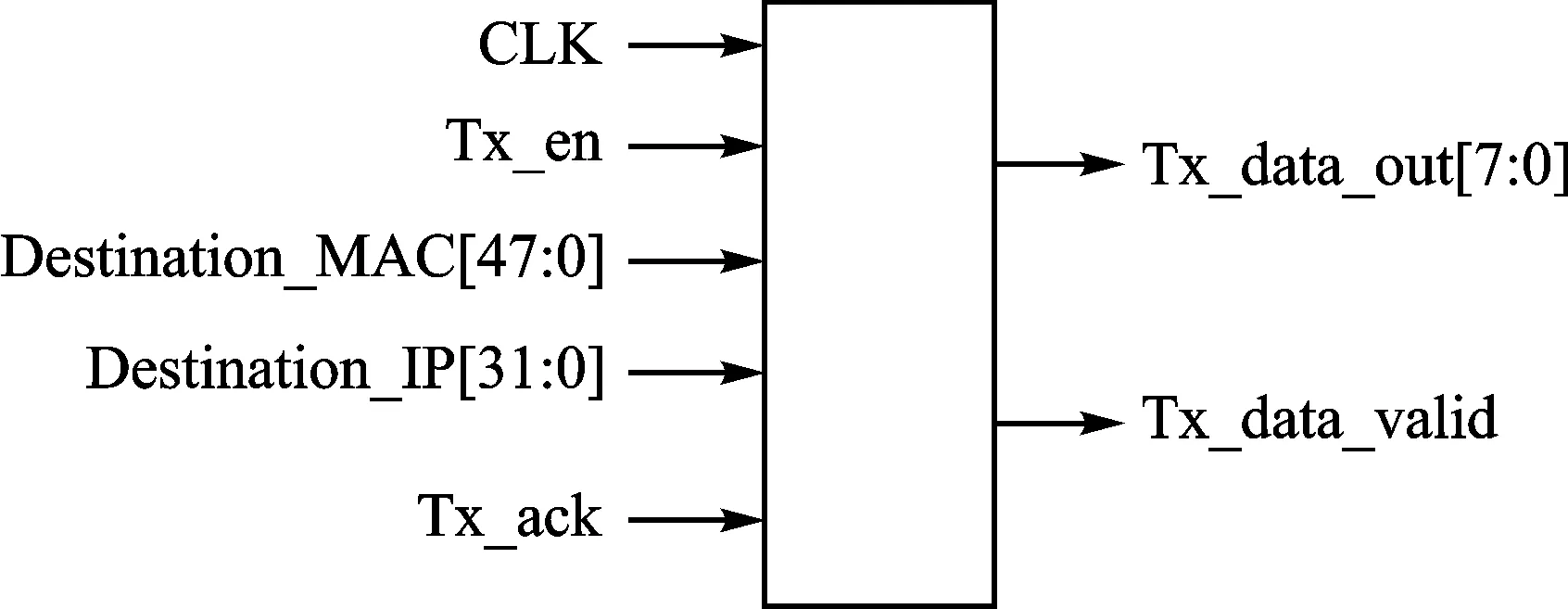

2.2 ARP應答發送模塊設計

在收到ARP請求幀后,ARP應答模塊完成應答幀封裝與發送。ARP發送模塊如圖7所示,可通過Destination_MAC和Destination_IP口從ARP目錄寄存器中獲取目的MAC和IP地址,每幀中都相同的數據通過參數parameter賦予ARP應答模塊。ARP應答幀的發送流程較為簡單,當Tx_en使能后,進入ARP應答幀發狀態,當第一個數據發送完,讀取MAC控制器回送的Tx_ack信號,若為1說明MAC控制器空閑,則按照ARP幀格式完成ARP應答幀發送,若為0,說明MAC控制器忙,則返回初始狀態。

圖7 ARP幀發送模塊

2.3 幀接收模塊

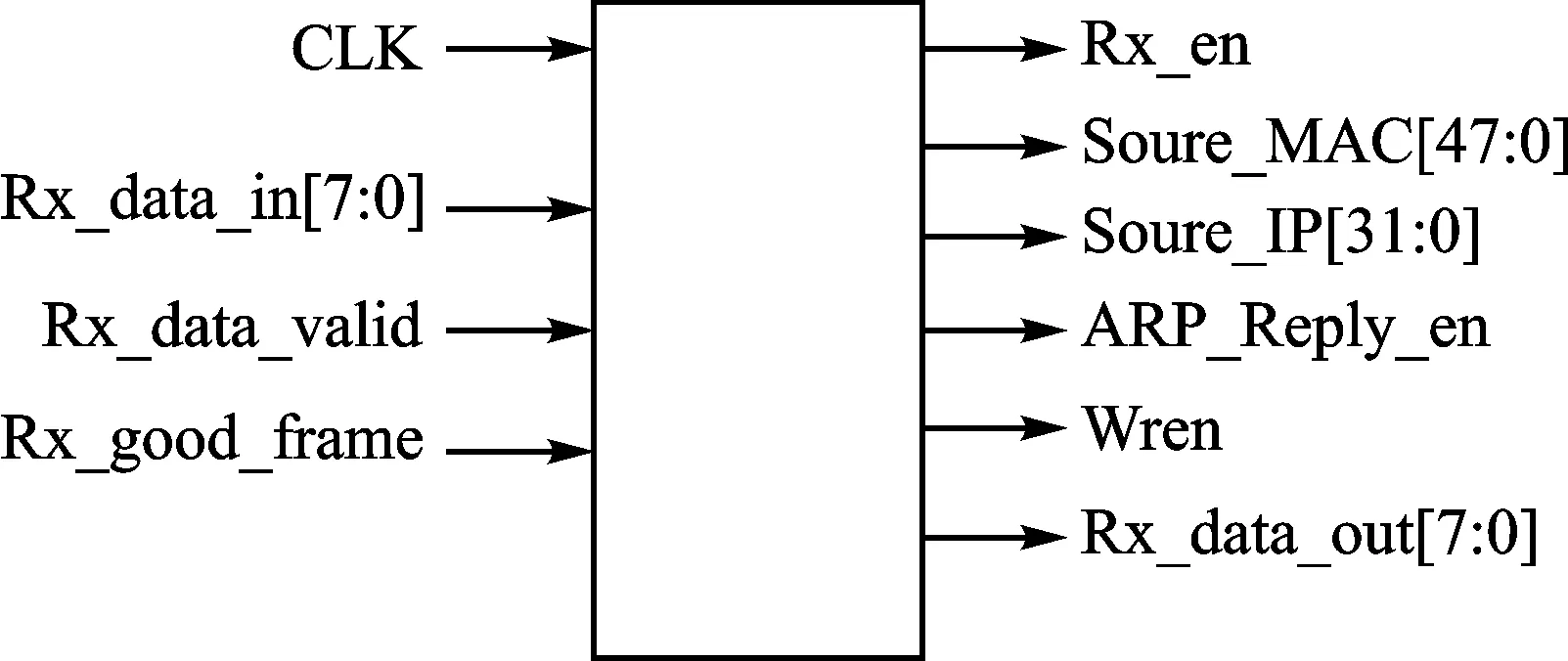

幀接收模塊實現對上位機發來的ARP請求幀和IP數據幀進行接收,并對不同類型幀做不同的處理。幀接收模塊接口如圖8所示, Rx_data_in為來自MAC控制器的數據輸入,Rx_data_valid為輸入數據有效標志位。接收模塊幀中的源MAC地址和源IP地址通過MAC和IP口送給ARP目錄模塊, ARP_Reply_en為ARP應答幀使能輸出端,Rx_data_out為UDP幀數據輸出端。

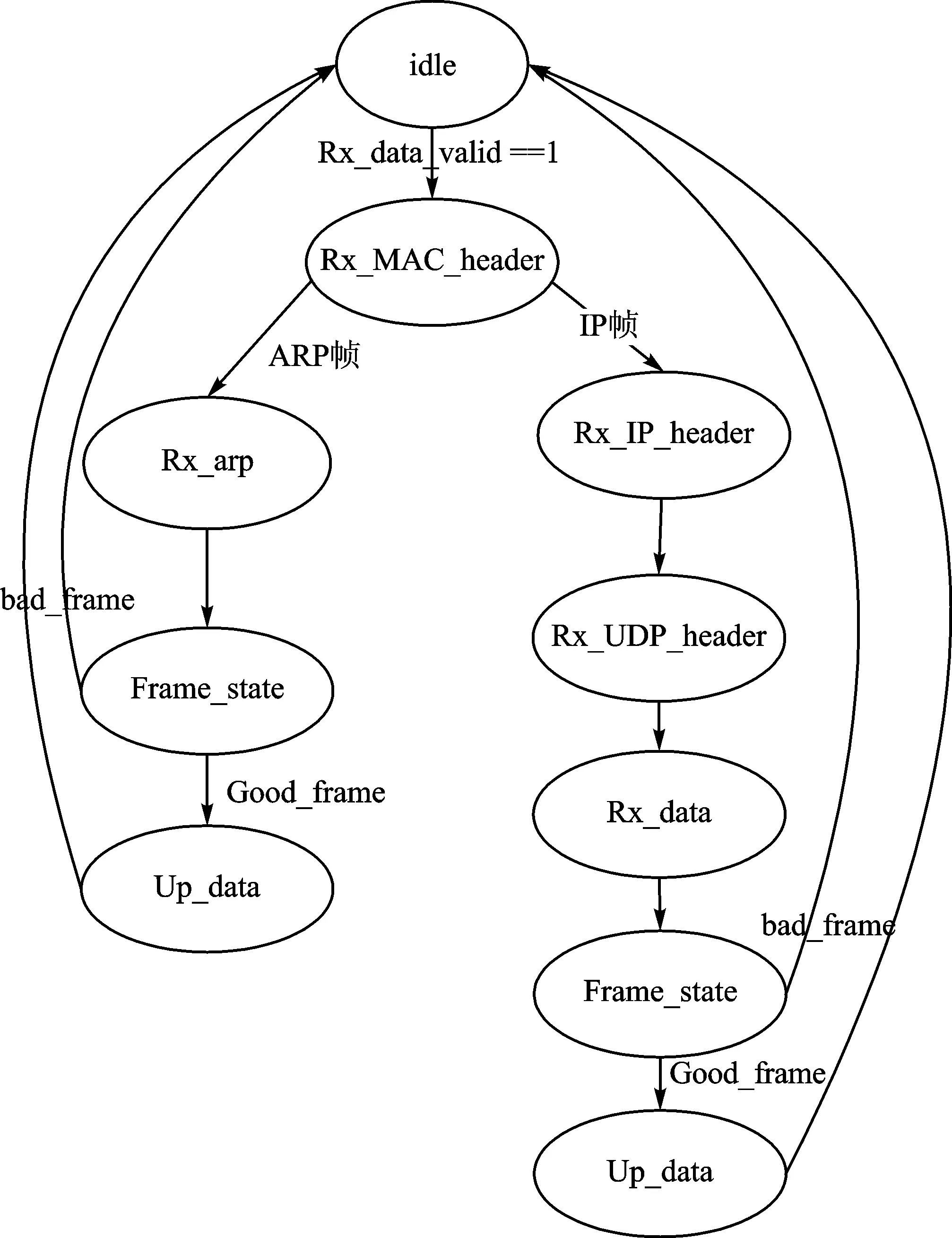

幀接收模塊的狀態流程如圖9所示,當檢測到Rx_data_valid 置高后,便開始數據接收。首先接收MAC幀頭并檢測協議類型,若為0x0806,說明為ARP幀,則進入Rx_arp幀接收狀態接收ARP幀剩余部分,在ARP幀接收完成后進入Frame_state狀態并通過Rx_good_frame判斷接收到的幀是否有效,若檢測到Rx_good_frame為1,表示接收到的ARP幀正確,則進入Up_data狀態,使能ARP_Reply_en輸出ARP幀中源MAC和IP地址,否則丟棄該幀并返回到idle狀態。若協議類型為0x0800,則按照IP幀格式進行幀接收,依次進入Rx_IP_header和Rx_UDP_header狀態完成IP和UDP幀頭接收,幀頭接收完成后進入數據接收狀態,將接收的數據存入模塊內的數據緩存區,在幀接收完后若檢測到Rx_good_frame為1,則輸出data_length個緩存數據,否則丟棄該幀數據并返回idle狀態。

圖8 幀接收模塊

圖9 幀接收模塊狀態流程

3 系統測試

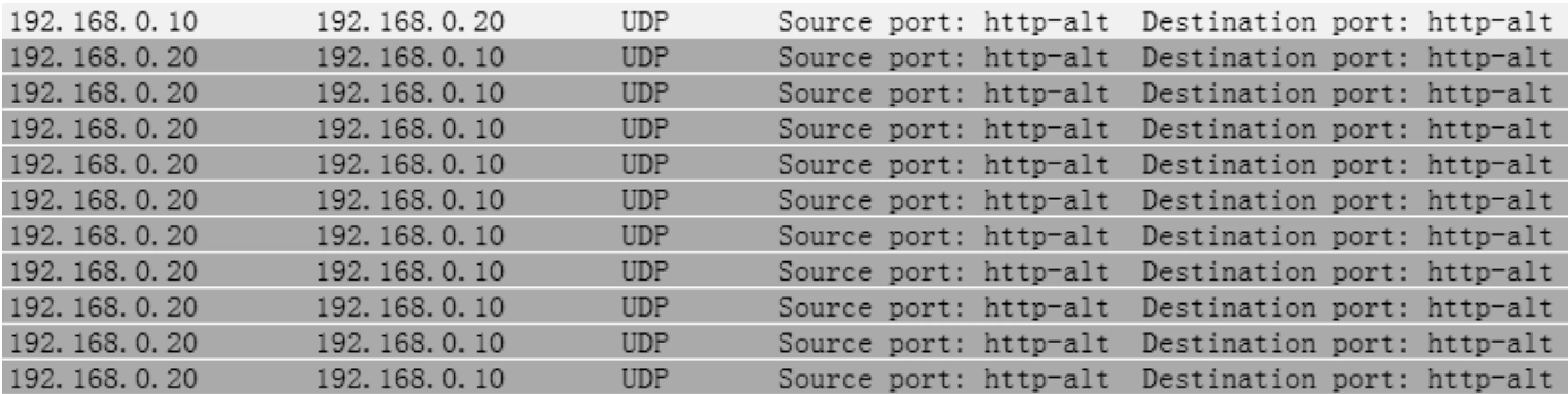

千兆以太網實現平臺選用ML605開發板,平臺包括XC6VLX240T型FPGA和PHY層芯片88E1111。為實現對系統測試,上位機裝有UDP幀收發軟件和Wireshark抓包軟件,實現數據幀的收發和抓包分析。設置以太網傳輸系統的IP地址為192.168.0.20,MAC地址為60:A4:4C:7B:E9:E8。設置上位機IP地址為192.168.0.10,MAC地址為DC:0E:A1:CD:60:65。

首先上位機向嵌入式以太網系統發送ARP請求來獲取系統的MAC地址,嵌入式以太網系統收到ARP地址請求后,發送ARP應答幀將本地MAC地址回送給上位機。上位機收到ARP應答幀后便發送包含數據發送命令的UDP幀,為測試嵌入式以太網數據發送性能,嵌入式以太網系統收到命令幀后開始重復向上位機發送固定幀長的數據幀。

Wireshark軟件抓包結果如圖10和圖11所示。圖10中,第1幀為上位機發送的ARP請求幀,包含的信息有上位機IP和MAC地址和要請求獲取嵌入式以太網設備的IP地址,第2幀為嵌入式以太網返回的ARP應答幀,將嵌入式以太網系統的MAC地址60:A4:4C:7B:E9:E8告知上位機。圖11中,第1幀為上位機發送給的包含數據發送命令的UDP幀,后續為嵌入式系統收到命令幀后,向上位機重復發送UDP數據幀,經測試,以太網系統能夠正常工作,傳輸數據穩定高效。

Design of Gigabit Ethernet Interface Based on FPGA and 88E1111

Zhu Minghui,Si Bin,Zhang Congxia,Zhang Peng

(China Airborne Missile Academy,Luoyang 471009,China)

In order to realize the data transmission between devices,the TCP/IP protocol has been studied,and a Gigabit Ethernet data transmission system based on FPGA and PHY physical layer chip 88E1111 is designed.The system uses the hardware description language to implement the Ethernet transmission protocol and uses the MAC Ethernet controller IP core to complete the frame verification and encapsulation.The physical layer is realized by using 88E1111 chip.According to the system design requirements,the TCP/IP Ethernet data protocol is cut out to only retain the UDP protocol,IP protocol and ARP address resolution protocol.The experiment results show that the Gigabit Ethernet system can achieve the data transmission stably and efficiently.

FPGA;Gigabit Ethernet;UDP;IP;ARP

圖10 ARP請求及應答幀抓包結果

圖11 UDP數據傳輸幀抓包結果

TP393

A