龍芯2F主板的PI仿真優化

凡兆龍++王凱++車博山++郭鑫宇

摘要:在現代高速電路中,越來越高的時鐘頻率給板級電源完整性的設計帶來了嚴峻的挑戰。本文探討了板級電源完整性設計的相關原理,針對一款自主設計的龍芯2F主板的電源網絡設計中存在電源波動較大,PCB空間不足的問題,采用ANSYS旗下的電路仿真工具SIwave對其進行了優化,改善了系統的穩定性,降低了成本,達到了預期的需求。

關鍵詞:ANSYS PI設計 仿真技術

中圖分類號:TP332 文獻標識碼:A 文章編號:1007-9416(2016)10-0078-01

隨著集成電路工作頻率的提高、電源完整性(Power Integrity,簡稱PI)問題漸漸成為高速電路設計的瓶頸之一,關系著整個設計的性能優劣甚至成敗[1]。工程上,由于系統電源平面并非絕對的導體,總是存在一定的阻抗,當瞬變電流流過該平面時,就會在路徑兩端產生一定的電壓波動。PI設計的目的就是在無法降低瞬態電流的情況下,盡可能地降低電源平面的目標阻抗,從而使流過該平面的電流產生的電壓波動減小,滿足系統要求。

1 PI設計的理論依據

理論上,電源的目標阻抗指的是能滿足負載的瞬態電流達到最大值,同時電源波動不超過最大允許范圍時,電源分布網絡(簡稱PDN)自身的阻抗[2],由式 (1)得到。

式中,表示的是電源電壓,反映負載芯片瞬態電流的最大值,這是一個和頻率有關的參數,芯片生產商通常不會提供I/f曲線,在實際計算目標阻抗時,通常取芯片所有門電路同時翻轉時的負載電流來近似,即

其中,是第n個IO腳的電流變化值。

傳統設計中,設計人員往往依據經驗來確定添加去耦電容的種類及數量,帶有一定的盲目性及不確定性,可能會因添加電容數量、種類不恰當,導致產品PI無法滿足要求或者PCB空間浪費。

2 PI設計的仿真優化

本文中待優化的是一款自主設計龍芯2F主板。龍芯2F是一款國產高性能64位CPU,IO工作電壓3.3V[3]。為了節約PCB空間,降低成本,本文以3.3V的IO工作電壓作為優化對象,介紹優化過程。

2.1 3.3V網絡目標阻抗的估計

查詢龍芯2F數據手冊可知,芯片的單個IO腳電流變化為8mA,IO電壓允許的最大變化范圍為0.7V,3.3V引腳數為20個,假定極限情況下,所有的IO同時發生狀態切換,則可以得到芯片IO最大工作電流160mA,根據式(1)可以得到龍芯2F3.3V IO電壓的目標阻抗為4.375Ω。

2.2 優化前預處理

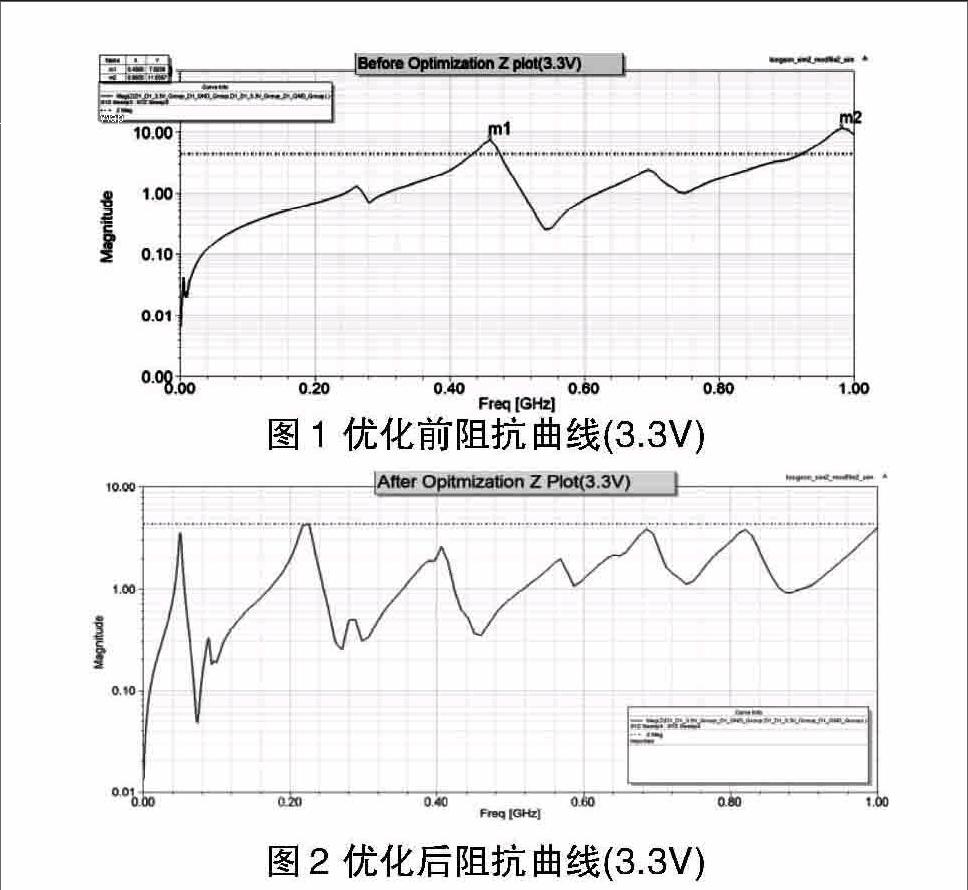

將待仿真的龍芯2F主板PCB文件導入SIwave 的工作區,設置仿真Port,截止頻率以及收斂精度等參數,運行仿真,得到優化前3.3V網絡的阻抗曲線。如圖1所示。

由上圖1可以看出,460MHz及982MHz兩處有反諧振尖峰超過了目標阻抗(4.375Ω)。下一步需要通過對去耦電容組合的優化,使阻抗曲線被“壓”到系統目標阻抗以下。

2.3 PDN的優化

運行SIwave工具,選擇需要優化的去耦電容,設置電容的價格、型號及封裝等屬性。運行仿真,最終軟件給出了一種最優方案,即僅需4個種類的,5只電容即可滿足優化的指標,比優化之前需要的5種15只電容在種類和數量上都大大減少,成本也大大降低。為了驗證優化效果,將策略1應用到PCB中,重新運行仿真,得到3.3V網絡優化后的阻抗曲線,如圖2所示。

由圖2可以看到優化后,3.3V網絡的阻抗分布曲線完全被控制在了目標阻抗4.375Ω以下,與預期相符合。

3 結語

本文在介紹了 PI設計原理的基礎上,利用SIwave對國產龍芯2F主板的電源網絡設計進行仿真分析,并給出了最佳優化方案。優化后的龍芯2F主板,能夠穩定可靠地運行,目前已經應用到實際項目中。綜上來看,ANSYS仿真工具的應用,縮短了開發周期,降低了設計的費用及失敗風險,具有一定的工程應用價值。

參考文獻

[1]于爭.信號完整性揭秘[M].北京:機械工業出版社,2014.

[2]葉白云,賈福楨.一種時頻域混合仿真的電源完整性分析方法[C].中國計算機學會第十二屆計算機工程與工藝學術年會.45-47.

[3]龍芯2F處理器數據手冊V1.0[S].中國科學院計算技術研究所,2008.

收稿日期:2016-09-16

作者簡介:凡兆龍(1988—),男,安徽淮北人,碩士,助理工程師,研究方向:嵌入式。