多核DSP和FPGA之間的高速SRIO通信

汪安民,韓道文,徐焱

(1.同方電子科技有限公司研究所,九江 332009;2.電子工程學(xué)院;3.哈爾濱工業(yè)大學(xué))

多核DSP和FPGA之間的高速SRIO通信

汪安民1,韓道文2,徐焱3

(1.同方電子科技有限公司研究所,九江 332009;2.電子工程學(xué)院;3.哈爾濱工業(yè)大學(xué))

在高速采樣系統(tǒng)中,大量數(shù)據(jù)需要實(shí)時(shí)傳輸?shù)教幚砥鳌S绕涫窍到y(tǒng)中存在多個(gè)處理器協(xié)同工作,就需要高速的總線來交換數(shù)據(jù)。SRIO總線由于存在連線少、傳輸速度高等優(yōu)點(diǎn),使用較為廣泛。本文介紹了多核DSP和FPGA之間使用SRIO進(jìn)行數(shù)據(jù)交換的軟硬件設(shè)計(jì)方法,在不同數(shù)據(jù)需求下,介紹了FPGA將數(shù)據(jù)直接傳輸?shù)紻SP的DDR3、片內(nèi)RAM或者多核的共享RAM中。本文研制了硬件系統(tǒng),給出了各種方式的軟件操作方法和實(shí)際硬件平臺(tái)驗(yàn)證,SRIO傳輸速率達(dá)到4 Gbps。

多核處理器;SRIO;共享RAM

引 言

大規(guī)模集成電路的高速發(fā)展,使得處理器的能力越來越強(qiáng),進(jìn)而處理的事件增多;大數(shù)據(jù)的應(yīng)用,使得高速寬帶采樣成為必然,高速采樣每秒采集到的信息量遠(yuǎn)遠(yuǎn)大于低速采樣。高速采集、高速存儲(chǔ)和高速處理成為發(fā)展的必然。這其中,高速傳輸通道是芯片間的數(shù)據(jù)橋梁,一般要求10 Gbps以上的處理速度,實(shí)時(shí)傳輸至少要達(dá)到幾Gbps。在設(shè)備之間,采用萬兆網(wǎng)、USB3.0、光纖通信等;在板間,采用PCIe、VPX等;而在芯片間,采用SRIO(也稱RapidIO)總線是常用方法。

多核處理器片內(nèi)集成多個(gè)處理器,目前得到大規(guī)模使用;同時(shí)多核處理器的強(qiáng)處理能力,也豐富了產(chǎn)品的功能。為了支撐功能使用,一般多核處理器都會(huì)配置大容量DDR2或DDR3,運(yùn)行程序和存儲(chǔ)數(shù)據(jù),還配置共享RAM空間用于多個(gè)核之間的通信,每個(gè)核還有自己的私有RAM。一旦其他芯片和多核處理器進(jìn)行數(shù)據(jù)交互,可能會(huì)和這3個(gè)RAM空間進(jìn)行高速通信。傳統(tǒng)的單處理器交換一定需要CPU參與,CPU讀取數(shù)據(jù),然后存儲(chǔ)到芯片的DDR、片內(nèi)RAM或者片外Flash空間。但這樣,每個(gè)數(shù)據(jù)交互都需要CPU參與,嚴(yán)重影響了運(yùn)行效益。而多核處理器,數(shù)據(jù)交互遠(yuǎn)比單核處理器頻繁,而且要求交互速率也非常高,這就需要數(shù)據(jù)總線直接進(jìn)行交互,而不用CPU參與[2]。

本文以8核DSP芯片TMS320C6678(以下簡(jiǎn)稱C6678)和xck7325t芯片為例,通過4線SRIO實(shí)現(xiàn)FPGA將數(shù)據(jù)直接傳輸?shù)紻SP的DDR3、共享片內(nèi)RAM的方法。筆者給出了軟硬件設(shè)計(jì)方法,研究了硬件平臺(tái),實(shí)際數(shù)據(jù)傳輸驗(yàn)證,該方法可以實(shí)現(xiàn)4 Gbps的高速傳輸。

1 多核DSP的RAM結(jié)構(gòu)

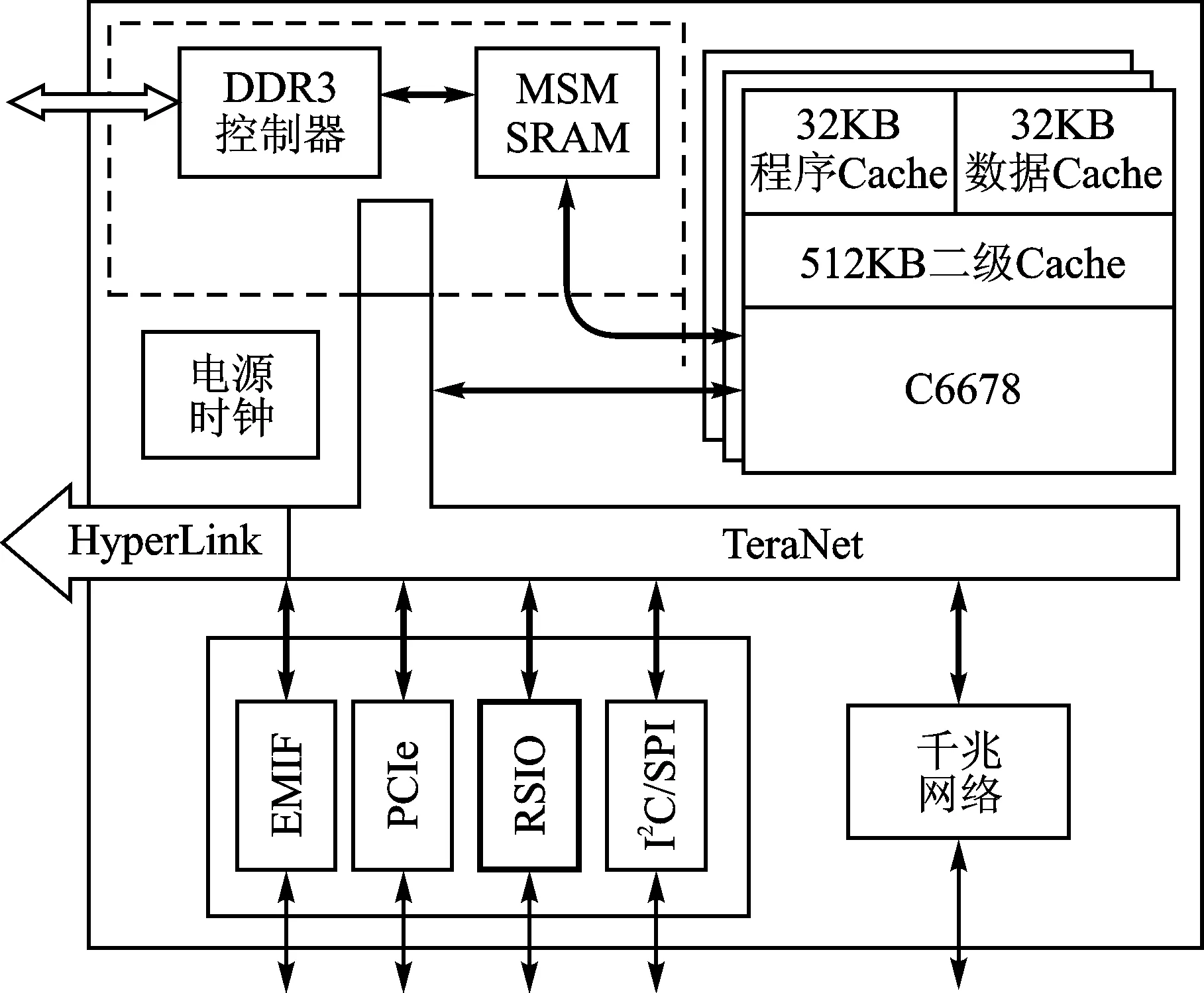

C6678是TI公司多核處理器中的一款8核浮點(diǎn)型DSP,最高工作頻率達(dá)到1.25 GHz,單個(gè)核具備40 GMAC定點(diǎn)計(jì)算或20 GFLOP浮點(diǎn)計(jì)算能力,單芯片具備320 GMAC或160 GFLOP的計(jì)算能力[3]。C6678的部分片內(nèi)結(jié)構(gòu)如圖1所示。

圖1 C6678內(nèi)部結(jié)構(gòu)圖

圖1主要列出了C6678和RAM相關(guān)的片內(nèi)模塊,其他部分未列出。從圖中可以看出,一個(gè)超高速的TeraNet(兆兆網(wǎng)絡(luò))總線將大部分模塊連接在一起,數(shù)據(jù)通過TeraNet總線進(jìn)行交互。核訪問共享RAM(圖中的MSM SRAM)的速度最快,它們之間不通過TeraNet,而是有專用的數(shù)據(jù)總線,不會(huì)和其他外設(shè)產(chǎn)生沖突,核訪問共享RAM的速率大概在50 Gbps。核訪問DDR3的速度僅次于共享RAM,因?yàn)镈DR3的數(shù)據(jù)需要通過共享RAM過渡,其讀寫訪問速度有所差別,讀速率至少可以達(dá)到10 Gbps,寫速率可以達(dá)到20 Gbps。核訪問其他片內(nèi)和片外設(shè)備都要經(jīng)過TeraNet,可能存在總線仲裁,但這些外設(shè)一般不會(huì)長(zhǎng)時(shí)間占據(jù)TeraNet總線。

本文關(guān)注的SRIO是直接掛在TeraNet總線上的,而C6678的DDR3控制器、共享RAM、512 KB的二級(jí)Cache都是連接在TeraNet總線上,所以,SRIO可以直接和這3個(gè)RAM進(jìn)行通信,但需要一定的時(shí)序控制,否則會(huì)造成RAM的互鎖,增大仲裁開銷,甚至程序死機(jī)。具體表現(xiàn)在:

① 和DDR3進(jìn)行通信。因?yàn)镈DR3一般會(huì)運(yùn)行主核程序,尤其是需要使用網(wǎng)絡(luò)接口,TI提供的NDK程序代碼很大,必須在DDR3中運(yùn)行。這樣程序運(yùn)行的DDR3地址,SRIO不能盲目進(jìn)行讀寫,尤其是寫操作,此外如果SRIO和程序需要同時(shí)讀某一地址,就會(huì)造成總線沖突。

② 和共享RAM進(jìn)行通信。共享RAM是用于多個(gè)核之間的數(shù)據(jù)交互,幾個(gè)核對(duì)共享RAM的某個(gè)地址進(jìn)行操作,一定需要一個(gè)控制權(quán)搶占,誰搶占到控制權(quán)誰就可以操作,其他核只能等待,這樣就避免了多個(gè)核同時(shí)訪問共享RAM的問題。如果SRIO對(duì)共享RAM進(jìn)行操作,一定需要將SRIO加入核之間的控制權(quán)搶占以及釋放。

③ 和每個(gè)核私有RAM進(jìn)行通信。理論上,SRIO可以和每個(gè)核的L1數(shù)據(jù)空間、L1程序空間、L2空間進(jìn)行通信。但一般程序會(huì)將L1的全部數(shù)據(jù)和程序空間、L2的部分空間定義為Cache,用于存儲(chǔ)程序運(yùn)行的中間結(jié)果,例如局部變量。程序在調(diào)試過程中的打印輸出等也需要較大的堆棧來處理,這些堆棧空間都在私有RAM中由SYS/BIOS自動(dòng)開辟。如果SRIO將數(shù)據(jù)寫入到這些空間,將很可能造成地址的同時(shí)讀寫,所以建議SRIO不對(duì)這些空間進(jìn)行操作。

2 SRIO的硬件連接

FPGA和DSP的SRIO硬件連接如圖2所示。SRIO總線由收發(fā)各4對(duì)差分線(一共16根線)組成。DSP的RIORXp0~3為4根收數(shù)據(jù)的正端,RIORXn0~3為一一對(duì)應(yīng)的4根收數(shù)據(jù)的負(fù)端,它們和FPGA相應(yīng)的8根發(fā)數(shù)據(jù)連接,形成一個(gè)FPGA發(fā)、DSP收的回路。另外8根線形成一個(gè)DSP發(fā)、FPGA收的回路。所以,在物理層,SRIO的收發(fā)是完全獨(dú)立的,可以做到收發(fā)全雙工。為了提高SRIO傳輸可靠性,在靠近收方的總線上,需要采用隔離電容,將信號(hào)直流隔掉,使得差分信號(hào)更加可靠。SRIO的時(shí)鐘由各自的處理器單獨(dú)設(shè)置,不要求DSP和FPGA共用SRIO時(shí)鐘。SRIO的傳輸時(shí)鐘是疊加在傳輸數(shù)據(jù)上的,由SRIO處理器從數(shù)據(jù)總線提取出時(shí)鐘信號(hào),用于數(shù)據(jù)位的對(duì)齊。這些處理工作,均由各自芯片的SRIO模塊完成,不需要用戶設(shè)置[4]。

圖2 硬件連接圖

圖2中,DSP外掛了5片DDR3,每片DDR3為16位數(shù)據(jù)寬度,4片組成64位數(shù)據(jù)寬度,直接連接到DSP。第5片連接到DSP的數(shù)據(jù)校驗(yàn)位,每個(gè)64位的數(shù)據(jù)通過BCH編碼生成一個(gè)8位的校驗(yàn)碼同時(shí)存放到第5片DDR3中,DSP讀取DDR3數(shù)據(jù)時(shí),也同時(shí)把這個(gè)校驗(yàn)碼讀出,進(jìn)行BCH譯碼。如果譯碼正確,則表示數(shù)據(jù)可靠,否則會(huì)嘗試重讀或多次失敗后丟棄數(shù)據(jù)。此外BCH碼具有一定的數(shù)據(jù)糾錯(cuò)能力,也可以提高DDR3數(shù)據(jù)的讀寫可靠性。經(jīng)過實(shí)際驗(yàn)證,由DSP直接讀速度達(dá)到10 Gbps,寫速度達(dá)到20 Gbps。

由于DSP有多個(gè)外設(shè),這些外設(shè)需要一個(gè)基準(zhǔn)時(shí)鐘,這樣就方便時(shí)序和同步控制,圖中采用CDCM62005對(duì)輸入的125 MHz時(shí)鐘進(jìn)行分頻,輸出多路CLK信號(hào),分別提供到SRIO、DDD3模塊,以及DSP的運(yùn)行主時(shí)鐘。實(shí)際上還可以提供給DSP的網(wǎng)絡(luò)模塊、PCIe等模塊。

3 軟件設(shè)計(jì)

軟件設(shè)計(jì)主要包括各個(gè)模塊的初始化、數(shù)據(jù)讀寫、中斷響應(yīng)和任務(wù)控制等。

3.1 DDR3的軟件設(shè)計(jì)

DDR3的軟件設(shè)計(jì)包括初始化、讀/寫數(shù)據(jù)和刷新控制等。由于DDR3是依靠電容的充放電狀態(tài)來存儲(chǔ)信息,就需要定時(shí)刷新來維持電容的狀態(tài)。定時(shí)刷新由處理器的片內(nèi)模塊自動(dòng)完成,用戶不需要參與。DDR3的初始化順序?yàn)椋?/p>

① 配置DDR3的PLL,通過設(shè)置PLL寄存器中的clkr、clkf、clkmod以及bwadj位來確定DDR3的工作時(shí)鐘。

② 延遲一段時(shí)間,等待PLL設(shè)置有效。

③ 清除RESET,使得PLL進(jìn)入工作狀態(tài),查詢PLL鎖定標(biāo)志。鎖定標(biāo)志有效,表示初始化過程結(jié)束。如果DDR3芯片及其周邊電路存在問題,PLL就會(huì)無法鎖定。這些問題可能包括:電源不穩(wěn)定、時(shí)鐘抖動(dòng)大以及硬件錯(cuò)誤等。

3.2 SRIO的軟件設(shè)計(jì)

SRIO的軟件設(shè)計(jì)包括初始化、數(shù)據(jù)讀寫和中斷響應(yīng)等。SRIO的軟件設(shè)計(jì)包括了FPGA和DSP兩個(gè)芯片,所以兩個(gè)芯片的大部分參數(shù)設(shè)置需要保持一致。此外,一旦SRIO的數(shù)據(jù)鏈路建立好后,一方不能自行單獨(dú)復(fù)位SRIO模塊,否則將出現(xiàn)雙方不能同步現(xiàn)象,SRIO數(shù)據(jù)不能正常通信。所以,一旦一方要求復(fù)位,必須通知對(duì)方。在程序中,建議在SRIO鏈路建立后,不進(jìn)行復(fù)位操作。SRIO的初始化順序?yàn)椋?/p>

① 配置SRIO的工作時(shí)鐘,SRIO需要從低速時(shí)鐘倍頻到高速時(shí)鐘,最低到1.25 Gbps,最高支持5 Gbps。一般電路板設(shè)計(jì)和制造后可以達(dá)到2.5 Gbps或者3.125 Gbps的時(shí)鐘速率。如果再采用4線制傳輸,傳輸數(shù)據(jù)速率可以輕松達(dá)到10 Gbps或者12.5 Gbps。

② 等到SRIO時(shí)鐘設(shè)置好后,按照先使能接收器,再使能發(fā)送器的順序復(fù)位自身的模塊,如果另外一方也設(shè)置好后,會(huì)看到連接寄存器的狀態(tài)位變化,表示雙方鏈路已經(jīng)建立;如果狀態(tài)位沒有變化,則說明存在硬件或者設(shè)置上的問題。

③ 設(shè)置數(shù)據(jù)收發(fā)中斷,可以以SRIO自身中斷,也可以以GPIO觸發(fā)另外中斷的方式。

3.3 SRIO傳輸數(shù)據(jù)到DDR3

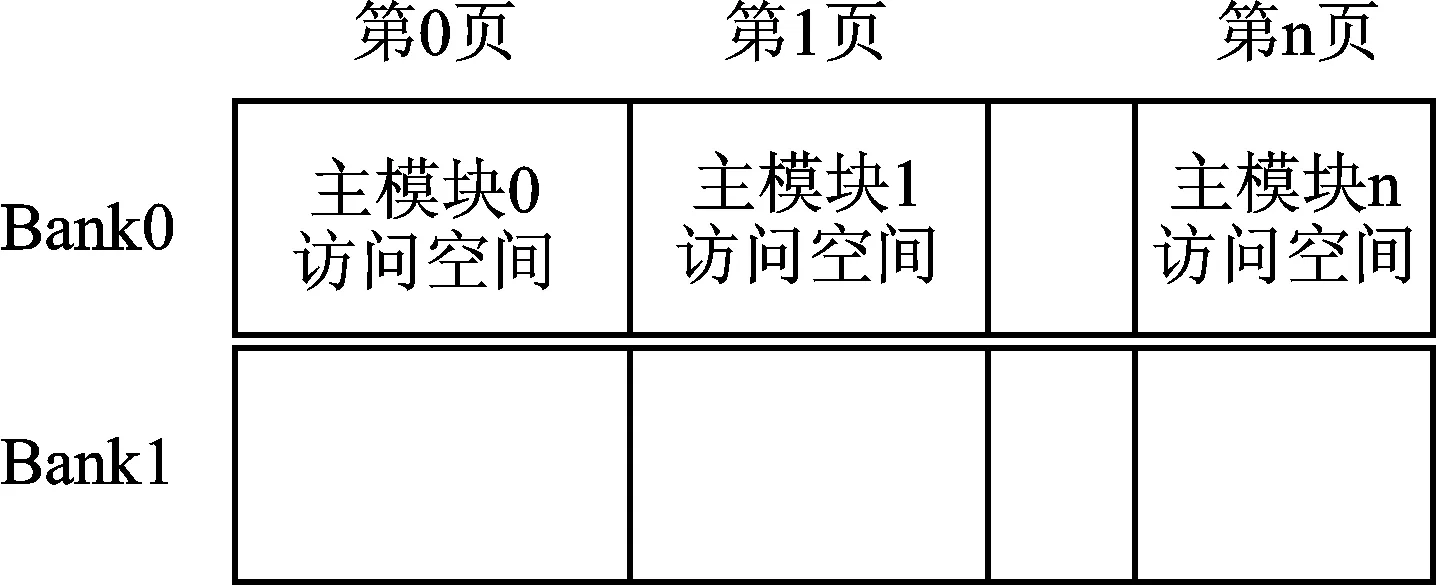

多核DSP的程序代碼一般在DDR3中運(yùn)行,一旦SRIO也對(duì)DDR3進(jìn)行操作,就存在多個(gè)主模塊共享DDR3的問題。DDR3控制器只有一組總線與DDR3連接,一旦出現(xiàn)多個(gè)主模塊同時(shí)訪問DDR3時(shí),必須要根據(jù)優(yōu)先級(jí)進(jìn)行總線仲裁。DDR3的訪問以頁(yè)為基礎(chǔ),一個(gè)主模塊訪問某個(gè)頁(yè)之前,必須要打開該頁(yè)。DDR3最高具有8個(gè)bank,每個(gè)bank可以打開一頁(yè),最多同時(shí)打開8頁(yè)。但如果想同時(shí)訪問一個(gè)bank中的2頁(yè)是不可能的,只有關(guān)閉掉其中一頁(yè),才能訪問另外一頁(yè),這就存在頁(yè)切換的問題。

圖3是多個(gè)主模塊訪問同一bank下的不同頁(yè),這是切換最頻繁的情況,每次訪問都要進(jìn)行頁(yè)切換,導(dǎo)致傳輸效率大大降低。如果SRIO將數(shù)據(jù)傳輸?shù)竭@些頁(yè),存在很大的風(fēng)險(xiǎn)。雖然DDR3控制器可以進(jìn)行總線仲裁,但對(duì)于SRIO的傳輸端FPGA,不清楚總線是否被占用,仍然傳輸數(shù)據(jù),將會(huì)導(dǎo)致數(shù)據(jù)丟失,所以不建議SRIO用這種情況訪問DDR3。

圖3 多個(gè)模塊訪問同一bank的頁(yè)

圖4是多個(gè)主模塊訪問不同bank不同頁(yè)的情況,這是最簡(jiǎn)單的情況,因?yàn)槊總€(gè)主模塊訪問的bank和頁(yè)均不同,所以不存在任何頁(yè)切換情況,總線傳輸很快。但圖中的空白頁(yè)將無法訪問,一旦訪問,將回到圖3所示的情況,導(dǎo)致大量DDR3空間不能使用,所以不建議SRIO用這種情況訪問DDR3。

圖4 多個(gè)模塊訪問不同bank的不同頁(yè)

圖5是圖4的簡(jiǎn)化訪問方式,這種方式只存在

High-speed Communication Between Multicore DSP and FGPA Based on SRIO

Wang Anmin1,Han Daowen2,Xu Yan3

(1.Research of Tongfang Science and Technology Ltd.,Jiujiang 332009,China;2.Electronic Engineering Institute 3.Harbin Institute of Techonlogy)

High speed data communication between the different processors is needed in the high sampling system.The SRIO bus is used widely because it’s high efficiency and low latency.In this paper,the design method of SRIO bus between FPGA and DSP is studied.The data translation is realized from FPGA to DDR3,shared RAM or private RAM of DSP.In this paper,the hardware system is developed,and the operation method of the software and the verification of the actual hardware platform are given.The result of data throughput is up to 4 Gbps by the SRIO bus in the real system.

multicore processor;SRIO;shared RAM

TP336

A