基于動芯基帶芯片的多核并行同步仿真平臺

周 鳴

(重慶郵電大學 通信與信息工程學院,重慶 400065)

基于動芯基帶芯片的多核并行同步仿真平臺

周 鳴

(重慶郵電大學 通信與信息工程學院,重慶 400065)

為了對物理層代碼進行驗證與分析,提出了一種基于動芯基帶芯片的多核仿真平臺。該平臺采用多線程技術,通過共享內存和信號量分別實現了多核間的通信和同步功能。實驗結果表明,該仿真平臺可以正確模擬多核間的并行運行情況,并驗證物理層代碼的正確性。該仿真平臺在動芯基帶芯片設計實現方面發揮了巨大作用。

物理層代碼;多線程;共享內存;信號量

引 言

隨著基帶芯片的結構以及處理過程越來越復雜,研發所需的時間越來越長,成本也越來越高。在芯片研發的過程中,設計者需要一個軟件仿真系統來對處理器的功能和物理層代碼進行驗證[1]。一方面,軟件仿真系統在芯片沒有制造出來之前,就可以讓物理層代碼在仿真平臺上運行調試,這樣應用程序設計和處理器結構設計可以同時進行,大大縮短了芯片開發周期;另一方面,芯片在設計驗證時經常需要改動,如果都使用樣本進行評估,所需要的時間和成本是無法估計的,而使用仿真平臺對處理器結構進行評估所需的時間和成本會大大降低。目前,模擬器已經成為處理器設計和制造過程中不可或缺的一部分[2]。

動芯基帶芯片是中科院計算機所研發的針對基帶數字信號處理的可重構和可擴展的基帶芯片。目前,動芯基帶芯片缺少一種方便實用的針對SoC的軟件仿真工具,在芯片設計之初很難對物理層算法進行評估及量化分析,使得這種基于工程師經驗的SoC設計方法難以在大規模SoC設計空間中找到一種滿足應用需求的最合理的點。此外,在軟基帶的設計方法中,片上多核應用程序的調試問題也非常突出。

目前,采取的解決方案是將多核應用程序分片在單核上執行并調試,然后將多核程序在RTL層進行仿真調試。但是該方案仿真速度慢,需要程序員了解硬件的并行執行邏輯,會使用硬件仿真工具,而且在RTL調試過程中,不能像高級語言調試那樣可以隨時查看變量,隨時設置斷點等,具有很大的限制,所以在多核芯片上,移植及仿真調試運行第三方的軟件程序非常困難。因此,急需一款基于動芯基帶芯片的多核仿真平臺來支持芯片的使用和推廣。當前,已經擁有一個良好的開發基礎:完整的動芯DSP開發工具,其中包括模擬器、編譯器、調試器和集成開發環境,這些條件完全可以支撐開發一款基于動芯基帶芯片的多核仿真平臺。

1 總體設計思想

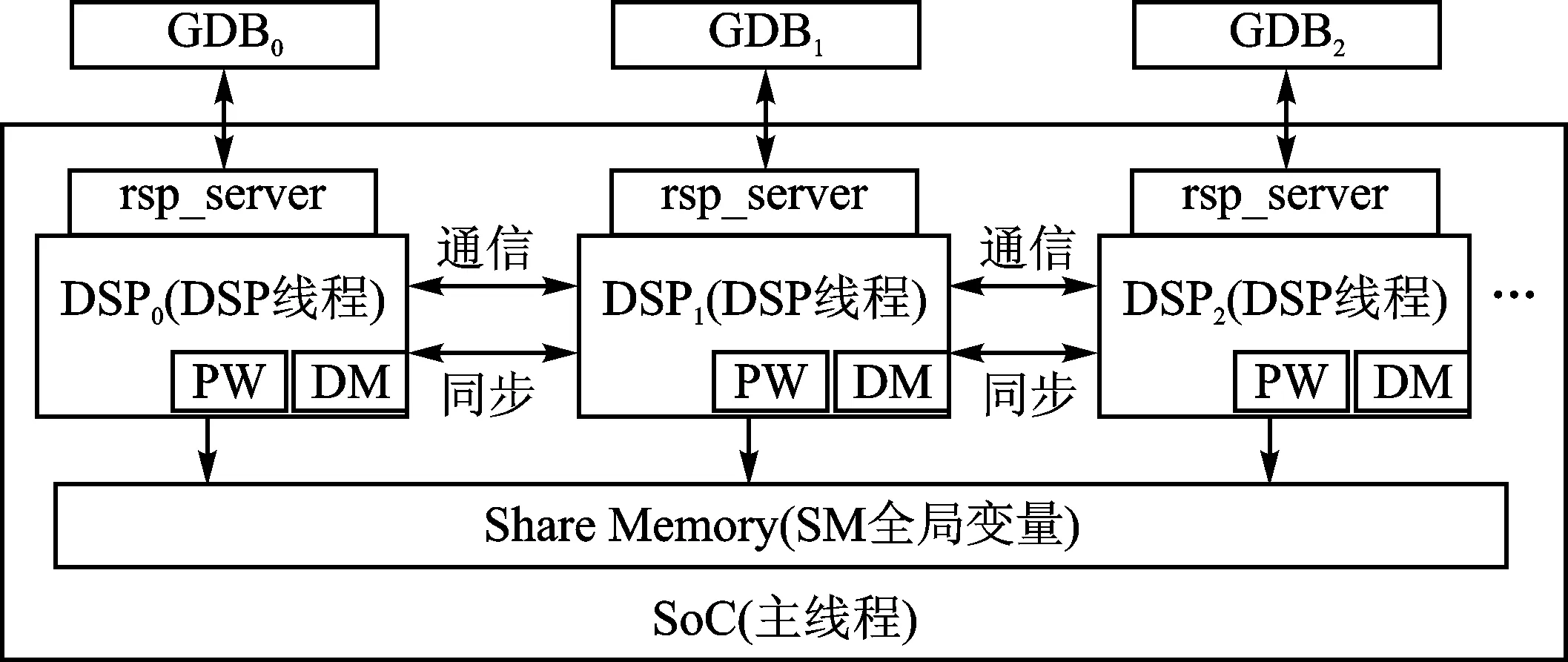

基于動芯基帶芯片的多核仿真平臺的核心是多線程技術[3]。使用多線程,可以對SoC上各硬件的并行情況進行較高程度的模擬。仿真平臺的結構如圖1所示。

圖1 仿真平臺結構圖

平臺主要由DSP模塊、共享內存模塊和調試器模塊組成。其中,共享內存模塊使用全局變量模擬,其余模塊使用線程模擬。在整個多核仿真平臺中,最重要的部分是DSP模塊,其基礎是動芯DSP指令集模擬器。動芯DSP指令集模擬器采用C語言開發,完全模擬了硬件功能實現,包括所有指令功能的實現、流水線結構、跳轉預測、多指令并行(VLIW)、數據的裝載與導出、變量的打印、與調試器的連接等諸多功能,除此之外,模擬器還肩負起了數據并行度探索、程序執行周期數統計等Profiling信息統計的責任。指令集模擬器只模擬硬件執行指令的行為,只是功能上的實現,并不涉及到信號線,只是模擬一條條指令執行后的寄存器、MEMORY的實時情況,所以在涉及此模擬器前不用去過多地關注硬件的布線等細節,應該更多地關注處理器的功能、結構、指令的執行、BYPASS、多通路等。由于多核仿真平臺實現不需要對DSP指令集模擬器內部結構進行修改,只是添加了一些用于通信同步的指令,所以為了方便多核模擬器的實現以及對DSP內部數據的保護,將整個DSP指令集模擬器都封裝到一個DSP類中。這樣通過將實例化的多個DSP對象傳進對應線程,就可以在完全繼承DSP指令集模擬器全部功能的基礎上實現多核DSP并行的目標。

從單核指令集模擬器到多核指令集模擬器,最重要的是解決多核間的通信以及同步問題。本文的思想是將多核間的問題轉換成多線程間的問題,將多線程間用于通信以及同步的函數以指令的形式添加到指令集模擬器中,同時在編譯器中也相應地加入這些指令,程序員就可以通過調用這些指令來解決多核間的通信同步問題。并行調試問題的解決方案是將每個DSP核都與一個GDB相連,并通過遠程調試的方法調試相應DSP核上的應用程序。

啟動多核仿真平臺之前,通過命令行參數對DSP核的個數、DSP內存、寄存器大小和各DSP核上物理層代碼進行配置,除了DSP核個數之外,其余都是通過讀取配置文件實現的。啟動之后,主線程會根據命令行的參數啟動各DSP核對應的線程,并將所需要的數據存入DSP線程的內存空間中,此時仿真平臺便可以運行物理層代碼。

2 多核關鍵技術及實現

2.1 核間通信

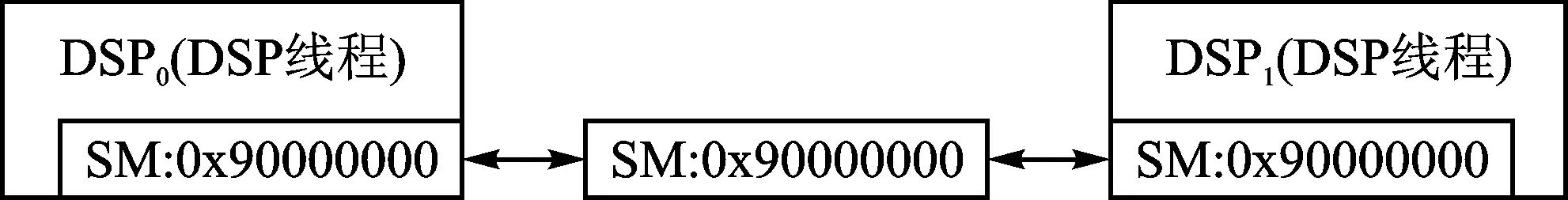

在多核仿真平臺中,每個DSP核都是通過一個線程來表示的,因此多核間的通信和同步問題就轉化成線程間的通信和同步問題。在線程中,它們之間的通信通過共享內存來實現,即在程序中新建一個全局變量的數組SM,這樣,各個線程就可以對這個數組讀寫數據,進而實現核間的數據交換。但是在SoC中,各個DSP只能通過指令向本地的局部地址中讀寫數據,不能直接向全局地址的共享內存中讀寫數據。為了解決此問題,在局部地址中分配一塊和共享內存同樣大小的內存空間,并保證兩塊內存空間中的數據具有一致性,為簡化實現過程,將局部地址和全局地址的起始地址均設為0x9000 0000,其結構如圖2所示。

圖2 共享內存結構圖

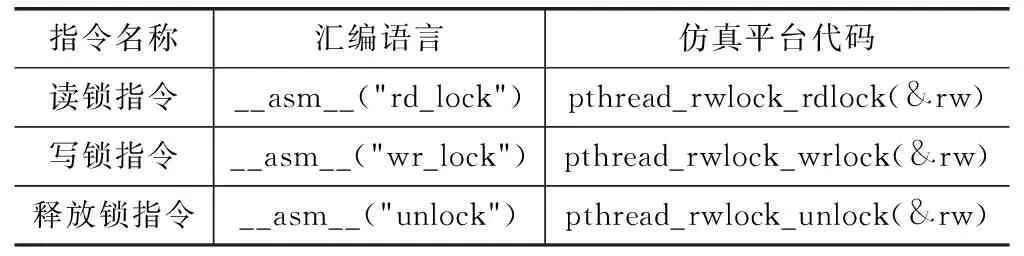

但是,這種簡單的通信方式會造成一個嚴重的后果:多個線程同時訪問全局變量SM,會造成數據混亂。為了解決這個問題,需要通過加鎖的方式對共享內存中的數據進行保護。在此基礎上考慮了兩種線程鎖:互斥鎖和讀寫鎖。相較于互斥鎖,讀寫鎖具有更好的適用性,可以有多個線程同時占用讀模式的讀寫鎖,但是只能有一個線程占用寫模式的讀寫鎖,具有很高的并行性,因此,選擇讀寫鎖來保護共享內存中的數據。將新增的讀寫指令添加到編譯器中,程序員即可調用匯編語言來實現多核間的讀寫功能,其使用方法與線程中的讀寫鎖使用方法一致,匯編語言和讀寫鎖函數對照如表1所列。

表1 讀寫指令對照表

2.2 核間同步

多核間同步可以理解為在物理層算法人員的調度下,各核可以按照指定的先后次序運行。因此需要設計同步指令,可以實現多核間的同步功能。同樣的,實現核間同步也可以轉換成線程間的同步問題。在線程同步中,主要有兩種方法可以考慮:條件變量和信號量。相比于條件變量,信號量有以下優點:信號的遞增與減少會被系統自動記住,系統內部有一個計數器實現信號量,不必擔心會丟失,而喚醒一個條件變量時,如果沒有相應的線程在等待該條件變量,這次喚醒將會丟失。因此,從SoC實際情況考慮,本文使用信號量來設計多核仿真平臺的同步指令。將新增的同步指令添加到編譯器中,程序員即可調用匯編語言來實現多核間的同步功能,使用方法與線程中的信號量使用方法一致,匯編語言和讀寫鎖函數對照如表2所列。其中,匯編語言的mode值可以根據程序員需要自由選擇,范圍是0~31,這樣,程序員就可以使用多個信號量來控制多核間的同步。

表2 同步指令對照表

2.3 調試模塊

圖4 并行同步調試驗證圖

本文采用兩種方法對調試模塊進行研究:一是在動芯DSP開發工具調試器的基礎上,通過將調試器與各個核進行通信,從而實現多核并行調試的目的,但是DSP模擬器采用GDB調試,在設計多核調試時受制于已有的框架,增加多核調試器設計的難度;二是針對整個多核仿真器重新開發調試器,這樣做不會受制于已有的平臺,但是工作量大,需要從頭做起。通過研究發現,動芯DSP的調試器從整體上來說也適用于多核仿真平臺調試器,其框架只具有很小的限制性。因此,只需要將調試器在模擬器這一端做少量的修改,即可將動芯DSP指令集模擬器的調試器移植到多核仿真平臺調試器。

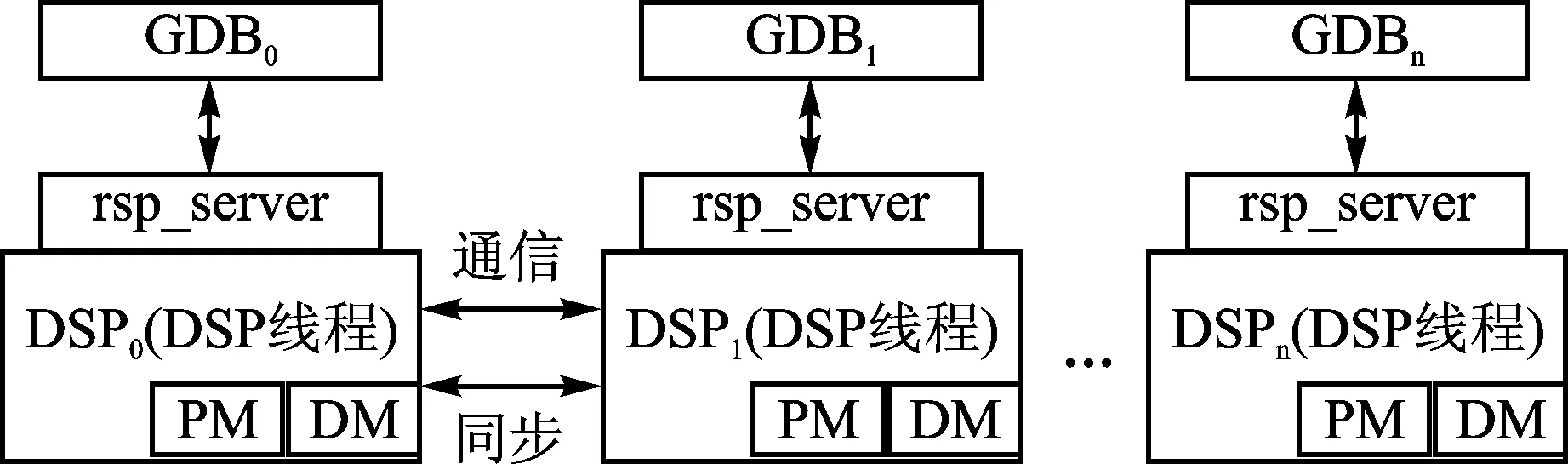

動芯DSP指令集模擬器調試器的方案是通過GDB對指令集模擬器上的應用程序進行遠程調試。Socket是模擬器與GDB的通信方式,其中,DSP模擬器作為Socket通信的服務端,GDB作為Socket的客戶端,RSP作為兩者通信協議。多核仿真平臺調試器設計結構如圖3所示,將DSP線程作為Socket通信的服務端,且每個DSP線程都有一個GDB客戶端與之相連,這樣就可以同時使用多個GDB并行調試多核仿真平臺,最終完成多核仿真平臺調試器的設計工作。

圖3 調試模塊結構圖

從單核調試器轉到多核調試器,從進程的角度觀察,就是從一個DSP模擬器進程和一個GDB進程之間的關系到一個多核模擬器進程與多個GDB進程之間的關系。其實現的方案是將DSP模擬器進程中公共RSP轉變為多核模擬器中各DSP線程私有的RSP。本文需要做的工作就是將RSP中用來存儲調試信息的數據在DSP類中重新聲明。這樣RSP的性質就從公共的變為線程私有的。完成以上工作就可以同時打開多個GDB調試器,對每個DSP核上運行的物理層代碼進行調試。

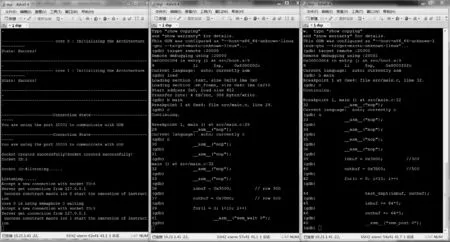

假設啟動兩個核的多核仿真平臺,此時需要打開3個終端,終端1用來啟動多核仿真平臺,終端2和終端3用來打開GDB對物理層應用程序進行調試,各終端命令行實現過程如下所示:

終端1:./dongxin -z 2 -j 20000 -k 20001。

終端2:Dongxin-gdb a.out;target remoter:20000;load。

終端3:Dongxin-gdb b.out;target remoter:20001;load。

其中,z后面的數字表示啟動的DSP核個數,j和k后面的數字分別為核1和核2與對應GDB連接的端口號,a.out和b.out分別表示在核1和核2上運行的應用程序的二進制代碼。

3 多核仿真平臺功能驗證

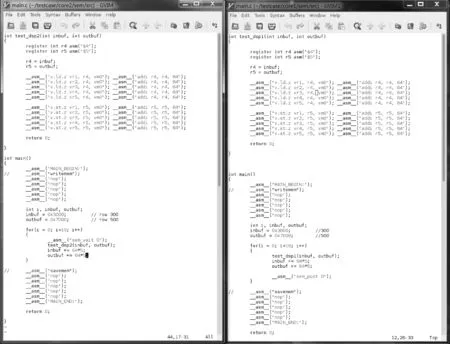

首先對多核仿真平臺的并行、多核同步、調試模塊三部分進行驗證。使用第2.3節中介紹的方法啟動兩個DSP核的多核仿真平臺,并對各個DSP核上的代碼進行調試,過程如圖4所示。

通過與圖5中的源代碼進行對比,可以看出第2個終端和第3個終端可以正確地對各個DSP上的應用程序進行并行調試,此過程驗證了多核仿真平臺并行和調試模塊的正確性。繼續執行源代碼,當終端2執行到__asm__("sem_wait 0")指令時,應用程序掛起,等到終端3程序執行完__asm__("sem_post 0")指令后,終端2中的應用程序又可以繼續執行,此過程驗證了多核仿真平臺多核同步的正確性。

圖5 應用程序源代碼

接下來,主要對多核間的通信進行驗證。同樣,先打開調試界面,然后對核1和核2上的應用程序進行調試,過程如圖6所示,當兩個核同時對共享內存數據進行讀操作時,兩個核上的程序可以并行執行;當核2在進行讀操作時,核1的寫操作不能執行,核1會掛起;當核1在進行寫操作時,核2的讀操作不能執行,核2會掛起。這個功能與多線程中的讀寫鎖功能一致,驗證了多核仿真平臺通信的正確性。

圖6 多核通信驗證圖

結 語

[1] 吳哲凱.可配置多核仿真器的研究與實現[D].南京:東南大學,2012.

[2] 林明亮.基于SimpleScalar的擁有存儲與總線擴展能力的異構多核仿真器[D].上海:上海交通大學,2007.

[3] 羅漢青,梁利平,葉甜春.一種多核指令集仿真器構建技術[J].計算機應用研究,2013,30(10):3035-3037.

[4] 李德明,全盛程,葉進.基于SoC的多核處理器并行仿真機制的研究[J].微電子學與計算機,2014,31(2):23-26.

[5] 付琳,胡錦,梁利平.指令集仿真器的關鍵技術[J].計算機應用,2015,35(5):1421-1425.

[6] 蘇雅麗.一種多核處理器時鐘精確并行仿真技術[J].赤峰學院學報:自然科學版,2015,31(3):12-13.

[7] 喻之斌,金海,鄒南海.計算機體系結構軟件模擬技術[J].軟件學報,2008,19(4):1051-1068.

[8] 高翔,張福新,等.基于龍芯CPU的多核全系統仿真器SimOS-Goodson[J].軟件學報,2007,18(4):1047-1055.

[9] 戴鵬,魏來,王明江,等.一種多核處理系統通信機制的仿真模型[J].微電子學與計算機,2012,29(6):1-6.

V.Kamakoti, SHAKTI Processors: An Open-Source Hardware Initiative[C]//29th International Conference on VLSI Design and 2016 15th International Conference on Embedded Systems (VLSID), Kolkata, India, 2016.

[5] PULPino User Manul[EB/OL].[2016-09].http://www.pulp-platform.org/documentation/.

[6] Michael Zimmer, David Broman, Chris Shaver,et al.FlexPRET: A Processor Platform for Mixed-Criticality Systems[C]//Proceedings of the 20th IEEE Real-Time and Embedded Technology and Application Symposium (RTAS), April, 2014.

[7] PEYRET Thomas, VENTROUX Nicolas, OLIVIER Thomas.HETEROGENEOUS MULTICORE BASED ON RISC-V PROCESSORS AND FD-SOI SILICON PLATFORM[C]//4th RISC-V Workshop Proceedings, 2016.

雷思磊(工程師),主要研究方向為處理器架構、嵌入式處理器應用等。

(責任編輯:楊迪娜 收稿日期:2016-09-12)

Multi-core Parallel Synchronous Simulation Platform Based on Dongxin Baseband Chip

Zhou Ming

(College of Communication and Information Engineering,Chongqing University of Posts and Communications,Chongqing 400065,China)

In order to check and analyze the physical layer code,a multi-core simulation platform based on Dongxin baseband chip is proposed.The platform uses the multithread technology to realize the function of communication and synchronization between cores by shared memory and semaphore.The experiment results show that the platform can correctly simulate the parallel operation between cores and verify the correctness of the physical layer code.This simulation platform plays a huge role on implementation of Dongxin baseband chip.

physical layer code;multithread;shared memory;semaphore

TP337

A

?士然

2016-11-18)