ARM+FPGA的雙模導航接收機硬件平臺設計

劉寧,馬洪濤,王曉君

(河北科技大學 信息科學與工程學院,石家莊 050000)

ARM+FPGA的雙模導航接收機硬件平臺設計

劉寧,馬洪濤,王曉君

(河北科技大學 信息科學與工程學院,石家莊 050000)

衛星導航系統能夠為廣大用戶提供全天時、全天候、高精度的導航、定位和授時服務。本文介紹一種基于ARM+FPGA架構的GPS/BDS雙模導航接收機的設計方法。該設計分為3部分:射頻部分電路設計、FPGA部分電路設計和ARM電路設計。其中,射頻部分主要完成GPS/L1頻點、BD2/B1以及B3頻點衛星信號的下變頻及采樣。FPGA部分做信號處理,ARM負責信息處理。經過測試,此設計是可行的,能夠達到導航接收機對于定位和授時精度的要求。

導航接收機;ARM;FPGA;信號

引 言

衛星導航系統現已發展為人類活動和促進社會發展的重要基礎設施。目前,世界上正在運行的有美國的GPS系統、俄羅斯的GLONASS系統、我國的北斗導航系統[1]。

雖然說,衛星導航系統能提供全球、全天候、連續和高精度的服務,但是,由于信號容易受到外界干擾以及由遮蔽引起的衛星信號中斷,從而使得導航接收機在某時、某地不能完成定位功能。從中國方面看,GPS和BD2間的相互融合成為發展趨勢,雙星座兼容機在定位的可靠性、準確性方面將大大提高。目前,國內已經出現很多雙模導航接收機,但大多數是DSP+FPGA架構的導航接收機,外圍接口比較單一,標準化和通用性做的不好,而且功耗較大[2]。而本課題研制的ARM+FPGA架構的導航接收機,在滿足性能的同時,還具有較低的成本和功耗,可以移植操作系統,支持現有DSP和FPGA接收機的程序移植,還具有強大的網絡功能,功能更強大,能夠應用于各個領域。因此在市場上該接收機將有更強的競爭力。

1 基于ARM+FPGA的雙模導航接收機硬件平臺設計方案

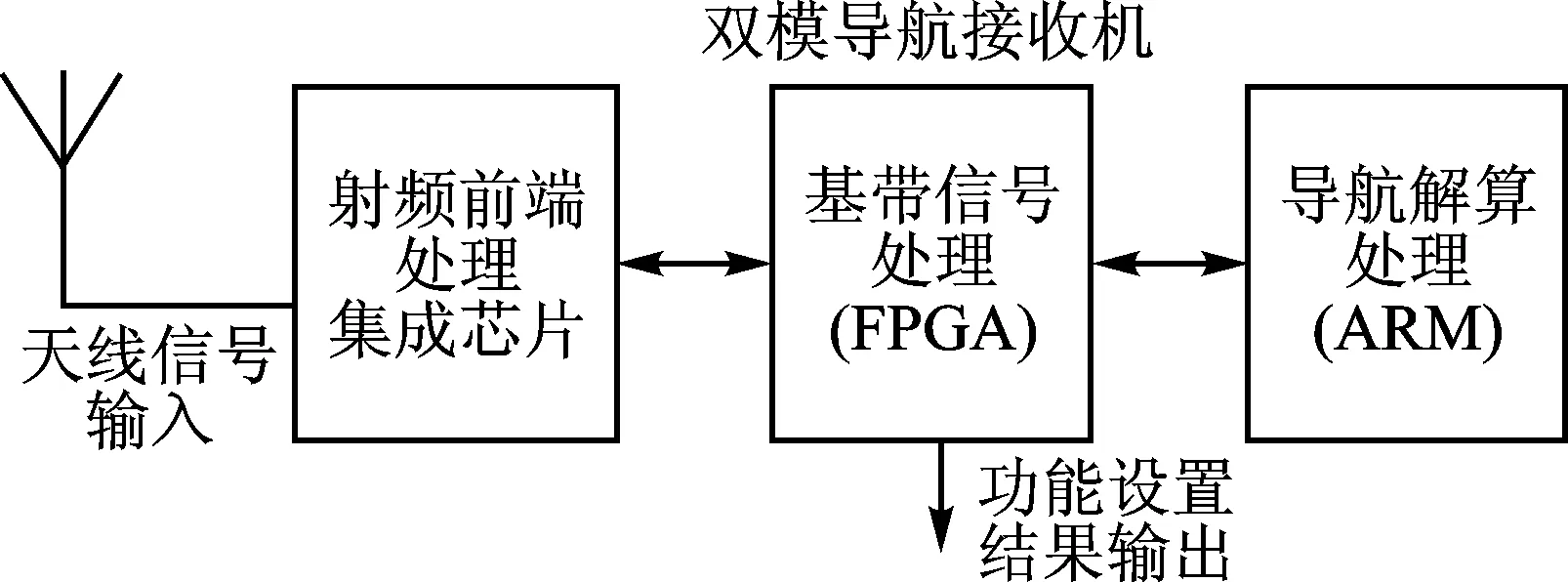

該導航接收機需要完成雙衛星系統3頻點的組合定位、導航和授時服務,基于這樣的特點,射頻前端采用集成度高、成本低、體積小且功耗低的專用集成芯片來對接收到的衛星信號進行下變頻、濾波、采樣、A/D變換輸出數字中頻信號[3]。在基帶信號處理部分來復制出與接收到的衛星信號相一致的載波和偽碼信號,需要完成大量并行的實時運算,需要多個信號通道,因此本設計中選用了FPGA來實現對衛星信號的捕獲跟蹤,并且從中獲得測量值以及導航電文[4]。在導航解算部分需要在短時間內處理大量的數據,進行各種復雜運算來解算出用戶的位置、速度和時間等信息,且還要兼顧功耗、成本以及功能擴展性[5]。經上述分析,該設計選用了ARM芯片來實現,最后將解算結果輸出到上位機。該導航接收機的總體結構圖如圖1所示。

圖1 雙模導航接收機總體結構框圖

2 單元電路設計

該接收機硬件電路主要包括射頻前端、基帶信號處理模塊、導航解算處理以及GPMC接口電路的設計。

2.1 射頻前端設計

此導航接收機需要接收雙衛星系統3頻點的衛星信號,為了適應它的多頻點要求,且把一路輸入的衛星中頻信號能量分成3路相等的能量輸出,選用了功分器芯片SCA-4-20+。從功分器出來的3路信號每一路信號都需要經過一個聲表面濾波器,利用不同頻帶濾波器的選頻特性,選用的濾波器為TA0967A和TA08,可以把BD2的B1/B3頻點和GPS的L1頻點的衛星信號過濾出來,分別輸出給3塊射頻芯片。

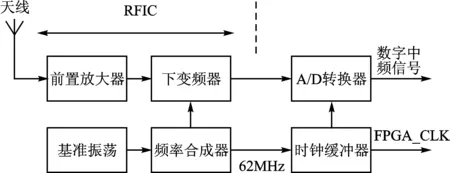

根據設計要求,選用的射頻信號處理芯片為SFM953DEQ,該芯片可以接收BD2的B1/B3、GPS/L1這3個頻點的衛星信號,并且可以按照不同衛星系統信號的特點,通過接口進行設置,設定不同的帶寬和晶振頻率,對這3個頻點的信號進行下變頻、濾波、中頻采樣處理。射頻前端的功能框圖如圖2所示。

圖2 射頻前端功能框圖

2.2 基帶信號處理模塊設計

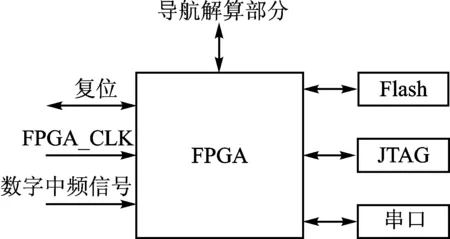

本設計中選用了Virtex-5系列的FPGA為基帶信號處理部分的主控芯片。這款芯片有豐富的I/O資源,還有6個PLL時鐘發生器的增強型時鐘管理模塊,核心頻率可以達到幾百兆,完全滿足各通信接口的時鐘要求。

基帶信號處理模塊主要包括FPGA、JTAG接口、Flash、復位接口以及時鐘電路等[6],其硬件結構框圖如圖3所示。FPGA選用的是Virtex-5系列的XC5VLX155_FFG1153,根據芯片型號和設計要求選用了Flash芯片,型號為XCF128XFTG64C,內部存儲空間有128 M B。該芯片不僅具備電子可擦除可編程的性能,還具有非常先進的寫保護機制。

圖3 基帶信號處理模塊硬件框圖

2.3 導航解算處理模塊設計

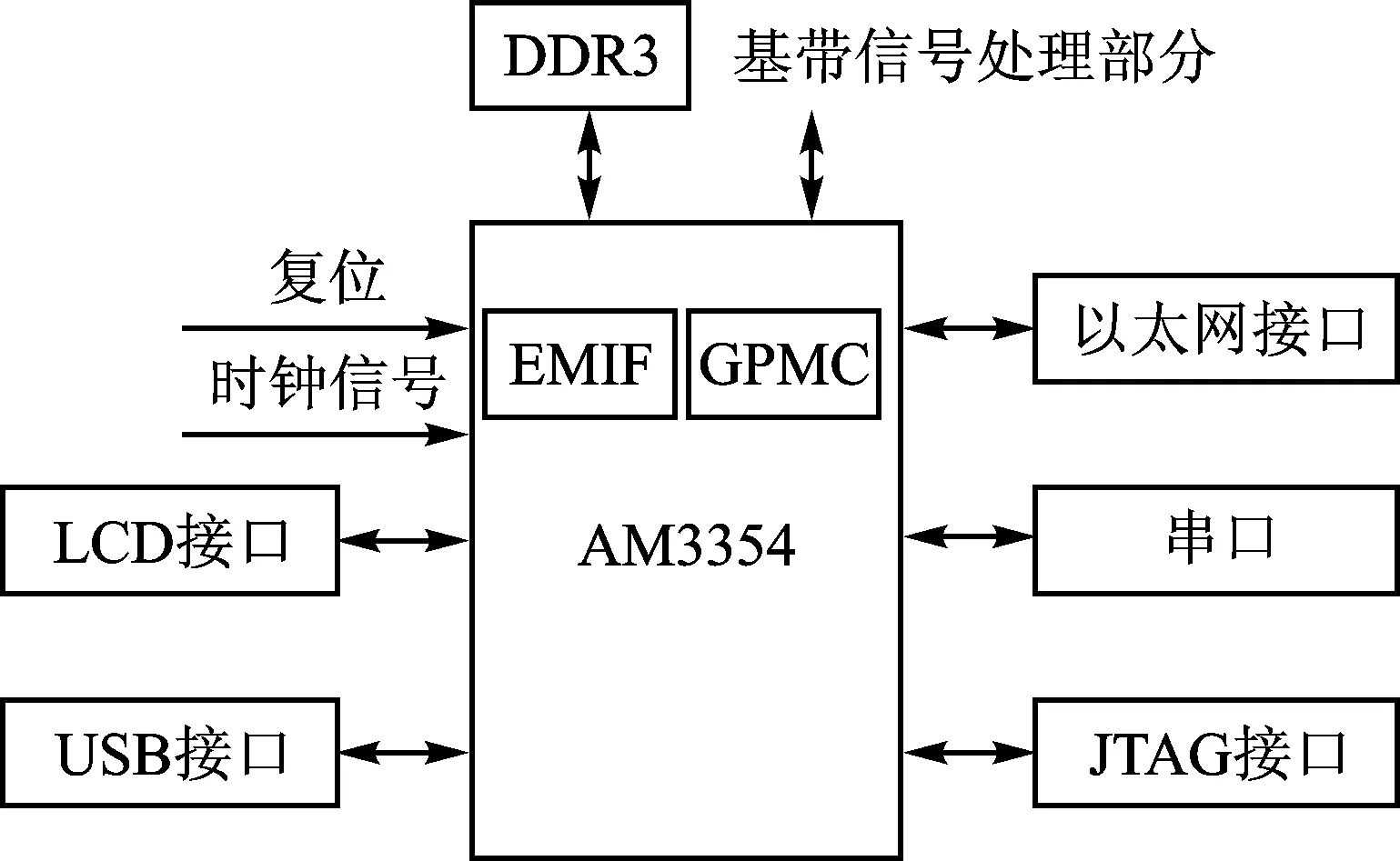

本設計中導航解算處理部分的主控芯片選用的是ARM A8系列的AM3354。它的主頻最高可以達到1 GHz,自身運算速度較快,精度較高,自帶通用存儲器控制器GPMC和外部存儲器接口EMIF,可與FPGA、SDRAM等實現無縫連接[7],該設計中使用了具有更高運行效能和更低電壓的存儲器DDR3,它還具有更高的外部數據傳輸率。該芯片還支持Linux, Android和高級操作系統HLOS,同時自身還帶有多達2個網口、串口、音頻串行端口、LCD控制器等,大大滿足了用戶對接收機的功能擴展。

導航解算處理模塊硬件電路主要包括時鐘電路、調試使用的JTAG接口、存儲DDR3接口、復位以及LCD顯示屏接口電路等。其硬件電路結構框圖如圖4所示。

圖4 導航解算處理模塊硬件框圖

2.4 GPMC接口電路設計

AM3354自帶的GPMC是一個內存控制器,可支持異步或同步8位、16位存儲器或者閃存設備,而存儲器或閃存設備的類型決定了GPMC的控制信號。本設計中利用FPGA來代替外部存儲器,模擬GPMC總線的讀寫時序,在讀時序中,FPGA采集的高速信號在寄存器中存儲完成后,給ARM發出中斷請求信號,ARM進行讀取操作,從而使CPU的效率大大提高,因此本設計利用GPMC總線作為FPGA與ARM的接口來完成高速數據的傳輸。

3 測試結果

本硬件平臺制作出來后,為驗證本設計的正確性,將平臺上電后進行測試,為了防止因電壓過高而燒毀芯片,在芯片焊接前先用萬用表對芯片電路所供電壓情況進行測試,然后焊接芯片寫測試程序對Flash、DDR、I/O、串口、總線接口等硬件電路進行測試。驗證結果顯示電壓正常,電路的各個部分工作正常,通信正常。

結 語

本文提出了一種雙模導航接收機的設計方案,并根據此方案設計了接收機的硬件平臺,編寫了硬件驅動程序,測試程序、把DSP+FPGA導航接收機程序移植到該平臺,完成了捕獲跟蹤以及定位解算[8]。經多次測試,該接收機工作穩定、精度較高、功耗較低,且通過串口與上位機軟件相結合,能明顯直觀地為用戶提供精確的位置和時間服務。本文設計的雙模導航接收機在實現定位、測速、授時的同時,還具有體積低、成本低,擴展性、通用性超強等特點、可被應用于導航相關的各個領域。

[1] 武虎子,南英,付瑩珍.國內外衛星導航技術發展綜述[J].現代防御技術,2008,36(5):46-51.

[2] 唐斌,劉富,張益青.GNSS接收機發展趨勢與研究思路分析[J].導航天地,2011(s1):82-84.

[3] 張北南.基于ARM的三模導航接收機基帶技術研究與實現[D].北京:北方工業大學,2014.

[4] 謝鋼. GPS 原理與接收機設計[M]. 北京:電子工業出版社,2009.

[5] 薛濤,趙偉,李榮冰,等.北斗導航接收機的硬件設計與實現[J].航天控制,2015,33(1):94-98.

[6] 劉競超,鄧中亮.基于ARM+FPGA北斗接收機設計[J].軟件,2012,33(12):38-40.

[7] 時東飛.基于FPGA及ARM核的GPS信號處理平臺的設計及實現[D].上海:上海交通大學,2012.

[8] Akopian D.Fast FFT based GPS Satellite Acquisition Methods[J].IEEE Proceedings on Radar,Sonar & Navigation,2005,152(4):277-286.

劉寧(在讀研究生)、王曉君(教授),主要研究方向為衛星應用技術;馬洪濤(副教授),主要研究方向智能化儀器儀表、電力電子技術。

Hardware Platform Design of Dual-mode Navigation Receiver Based on ARM+FPGA

Liu Ning,Ma Hongtao,Wang Xiaojun

(Hebei University of Science&Technology,Shijiazhuang,050000,China)

The satellite navigation system is able to provide the broad masses of users throughout the day,all-weather,high precision of the navigation,positioning and timing services.In the paper,a design scheme and implementation of GPS/BDS dual-mode navigation receiver based on ARM+FPGA is introduced.The design is divided into three parts,such as the radio frequency circuit design,FPGA and ARM circuit design.The satellite signal of GPS L1 and BD2 B1 and B3 frequency point is amplified,down-converted and sampled by the radio frequency circuit.The signal is processed by the FPGA and the information is processed by ARM.The experiment results show that the design is feasible,and it can meet the accuracy requirement of the navigation receiver for positioning and timing.

navigation receiver;ARM;FPGA;signal

TN965.5

A

迪娜

2016-11-14)