TMS320C6455在實時圖像處理系統中的應用

梁賀斌,馮水春,周 海,卞春江,王小燕,毛博年

(1.中國科學院國家空間科學中心 北京 100190;2.中國科學院大學 北京100190)

TMS320C6455在實時圖像處理系統中的應用

梁賀斌1,2,馮水春1,周 海1,卞春江1,王小燕1,毛博年1

(1.中國科學院國家空間科學中心 北京 100190;2.中國科學院大學 北京100190)

為了完成圖像目標點的檢測和確認,同時實現FPGA與DSP之間的通信數據高速傳輸,文中基于高速DSP芯片TMS320C6455提出了一種數字圖像處理系統設計方案。該系統硬件部分用來模擬圖像數據輸入輸出,軟件部分基于Code Composer Studio(CCS)平臺采用C語言編程實現。通過軟件設計和外部存儲器接口(EMIF)、增強型直接存儲器(EDMA)等底層配置的實現,完成了圖像實時處理過程,并實現了FPGA與DSP之間的高速通信。實驗結果表明,利用該芯片設計的圖像處理系統完全滿足設計要求,實時性較好,系統集成度高,該設計方案在數字圖像處理領域具有很大的應用價值。

TMS320C6455;數字圖像處理;數字信號處理器;外部存儲器接口;增強型直接存儲器

DSP技術的迅速發展使得DSP技術在通信、航天、軍事、自動控制等領域得到越來越廣泛的應用,而DSP芯片的誕生,對實現各種DSP的應用系統有著積極的推動作用,使得理論研究能夠在低成本的系統中得到應用,其中,DSP圖像處理系統便是其中的一種[1-5]。

DSP圖像處理系統設計包括硬件和軟件兩個方面,硬件設計需要考慮到運算的精度、系統的成本及體積、功耗等,并在此基礎上選擇合適的DSP芯片,進而設計芯片的外圍電路等;軟件設計主要在選擇的DSP芯片基礎上編寫相應的DSP程序,編程語言以C語言及匯編語言居多。針對德州儀器(Ti)公司的DSP芯片,一般采用CCS工具軟件進行開發,其中,CCSv5是一個集成了Eclipse軟件的開發環境,包括了編輯、編譯、軟件模擬和調試等所有需要的軟件[6]。

1 DSP系統總體設計

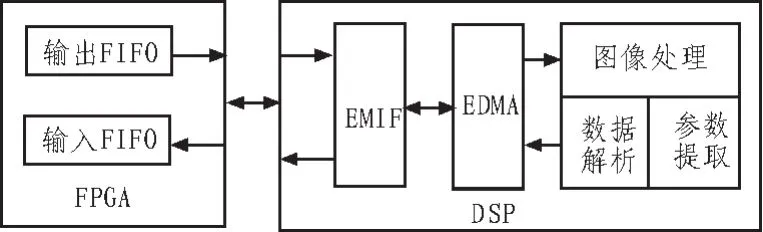

DSP系統由FPGA和DSP兩個部分組成,要實現FPGA與DSP之間高速數據傳輸,就不得不考慮EDMA方式,EDMA最大的優勢就是可以在不占用CPU資源的情況下完成映射存儲空間的數據搬移,這些數據搬移可以在片內存儲器、片內外設或者外部器件之間進行,且在CPU后臺實現[7-9]。

系統的總體設計如圖1所示,FPGA預處理模塊將經過預處理之后的數據由輸入FIFO通過DSP的存儲器接口傳給DSP,然后DSP通過EDMA方式將參數及數據保存到內部存儲器,并進行圖像處理,處理后的數據通過本地EMIF以EDMA方式將數據傳輸到FPGA的輸出FIFO中,進行后面的操作。

此外,DSP內部設計了數據解析協議,對數據解析及參數提取后,提供圖像處理需要的實際參數,將處理后的數據按照約定的格式經過DSP與FPGA間的接口傳遞給FPGA。

2 系統硬件設計

2.1 TMS320C6455簡介

TMS320C6455(以下簡稱C6455)是目前Ti DSP定點芯片的頂級產品之一,在圖像處理等方面具有較高的性能,且適用于高級語言編程[10]。C6455時鐘頻率為 1.2 GHz,16位定點處理能力為9600MMAC/s,而ADI的高端產品Tiger-SHARC定點處理能力為4800MMAC/s.此外,C6455很好的解決了芯片間數據傳輸問題,這使得多處理器平臺的搭建更加方便高效,可見,C6455在通信、圖像處理等領域將得到廣泛應用。文中在C6455芯片的基礎之上,深入研究并利用EMIF和GPIO等模塊實現了EDMA實時搬移圖像數據功能。

2.2 C6455的設計及功能實現

DSP的設計及實現,需要考慮時鐘頻率、通用輸入/輸出、DMA直接存儲器和中斷觸發等方面的問題。如圖1中DSP模塊所示,根據C6455的特點,主要從GPIO、EMIFA模塊、EDMA控制器以及中斷初始化等方面著手,完成DSP的設計及功能實現[11-15]。

圖1 DSP總體設計圖

2.2.1 GPIO配置及其初始化

GPIO,即通用輸入/輸出,根據指定的通用引腳功能配置為輸入/輸出。設置為輸出時,用戶可通過向內部寄存器寫數據來控制輸出引腳驅動的狀態;設置為輸入時,可以通過讀取內部寄存器的數據來檢測輸入狀態。而且,在不同的中斷和事件產生模式下,GPIO能夠產生CPU中斷和EDMA事件,GPIO框架如圖2所示。

圖2 GPIO框圖

C6455中共有16個通用輸入輸出管腳,每一個管腳都可以單獨進行配置成如下功能之一:通用輸入管腳 Input、通用輸出管腳 Output以及中斷和EDMA事件管腳。GPIO方向(GPDIR)寄存器控制GPIO管腳是輸入還是輸出,對應bit置0表示該管腳配置為輸出管腳;對應bit置1表示該管腳配置為輸入管腳。根據需要通過配置C6455的外設配置寄存器來使能GPIO模塊,可以調用CSL庫的API函數,這里利用CSL_FINST庫函數把C6455中的PERCFG0寄存器中GPIO對應位置1,ENABLE使能GPIO模塊,調用CSL_gpioInit函數對GPIO模塊進行初始化,并通過CSL_gpioOpen函數打開GPIO模塊,使能GPIO相應管腳作為中斷源,并配置PIN管腳的方向及中斷觸發方式,這里配置CSL_GPIO_PIN5管腳為中斷源,上升沿觸發,輸入有效,如果有其它需求,按照同樣的方法進行配置[11]。

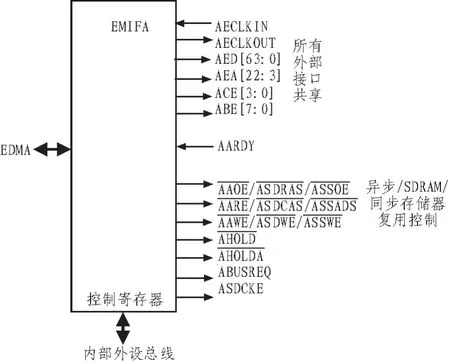

2.2.2 EMIFA模塊配置及其初始化

外部存儲器接口(EMIF)負責將DSP芯片與其它外部設備進行連接,它可以同時連接FLASH和SDRAM芯片,為DSP擴展外部程序和數據的存儲空間。圖3為TMS320C64X的EMIFA接口信號,SDCKE為ADRAM時鐘使能,只適用于EMIFA,其它信號同時適用于EMIFB。EMIF的時鐘ECLKOUT基于EMIF輸入時鐘ECLKIN在片內產生,外部ECLKIN時鐘可由FPGA提供。EMIF時鐘在器件復位時可以通過編程具體配置,即可以由外部時鐘、ECLKIN或者內部CPU時鐘驅動,不過FPGA直接提供的時鐘和頻率更容易更改。

此外,EMIFA接口可以支持8、16、32或64位系統接口,一般情況下存儲器等外部器件默認為字節側右對齊,支持大端和小端模式。其中,字節順序(Endianess)決定了存取的方式是小端還是大端模式。正確運行EMIF還需要根據同步還是異步存儲設置CE控制寄存器等,不同的外接存儲器接口通過內存映射到DSP存儲器空間,這里選擇同步工作模式。

圖3 EMIFA接口

通過EMIF接口,使得DSP可以和FPGA很方便地進行大數據量的數據傳輸。C6455的EMIFA可以訪問多種外部存儲器,如SRAM、ROM、FLASH等,也包括FPGA。與FPGA通信,需要使用的管腳要少很多,EMIFA共支持4個外部存儲器,比如可以把CE2分配給FPGA,CE3分配給SRAM,CE4分配給FLASH等,這里選擇把CE2、CE3分配給FPGA,CE4未分配。FPGA內部RAM數據的讀取,只需設定EDMA要讀取的數據的基地址是0xA0000000,以及讀取的數據的長度即可,因為FPGA內部時序邏輯可以產生地址,不必使用地址線。

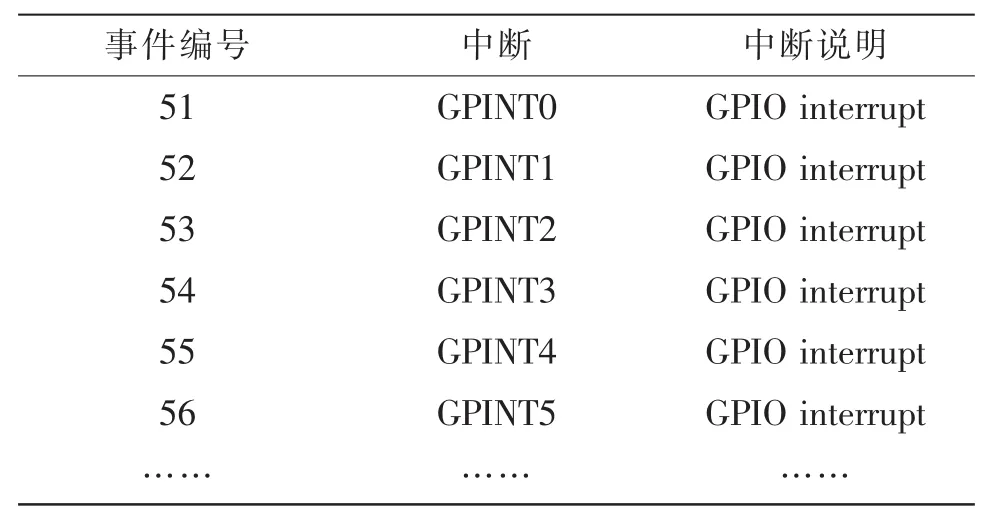

表1 CEn配置寄存器

CEn配置寄存器的結構如表1所示,與FPGA連 接 時 , 主 要 考 慮 R_ENABLE、W_LTNCY、R_LTNCY和SBSIZE 4個參數,不同的值表示不同的含義:R_ENABLE設置SRE/SADS管腳功能,這里賦值為1表示管腳功能為 SRE,即 Read Enable;W_LTNCY為寫延時周期,取值為0,表示0周期延時;W_LTNCY為讀延時周期,取值為3,表示讀延遲為3周期;SBSIZE為3,表示數據位寬為64為數據總線,即CE2CFG=0x8000010A,表示DSP開始讀FPGA的RAM,經過3個ECLKOUT周期后第一個數據會出現在數據總線上。下一步,可以利用CSL配置 EMIFA模塊,首先 CSL_FINST使能設備的EMIFA功能 ,利 用 CSL_EmifaMemType配 置CE2CFG寄存器的參數,并調用CSL_emifaInit函數將EMIFA模塊初始化,之后CSL_emifaOpen函數打開EMIFA模塊并利用CSL_emifaHwSetup函數將配置的參數設置到打開的EMIFA模塊中,配置結束。

2.2.3 EDMA控制器設置及初始化

EDMA,即增強型直接存儲器訪問,是C6455及其他C6000系列所特有的性能,執行所有二級高速緩存或內存控制器與外設之間的數據傳輸,圖4為EDMA事件的具體傳輸參數結構。

圖4 EDMA事件的傳輸參數結構

EDMA進行數據傳輸時可以通過同步和非同步兩種方式完成初始化,其中,非同步方式由CPU發起,傳輸數據時CPU將ESR事件設置寄存器相應事件位置1,觸發EDMA通道事件;同步方式則不同,事件觸發并被保存在ER事件寄存器中,CPU對相應的寄存器置1,ER保存的事件提交給相應的事件編碼器,調用參數,盡管該傳輸由事件觸發,但事件本身須先由CPU使能,EER事件寄存器負責該事件的使能控制,因此,如果對應于該事件的對應位沒有置1,則ER寄存器繼續保留該事件直到CPU對相應的寄存器置1,才能觸發EDMA進行傳輸。

對于由某個事件觸發的EDMA傳輸,數據單元計數值及幀計數值的更新方式取決于傳輸類型(1D或2D)和同步方式的設置,EDMA控制器將自動跟蹤數據單元計數值的變化,按照數據大小或數據單元/幀索引值對傳輸地址進行更新,源/目的地址的更新模式由實際的傳輸類型決定。

EDMA全部 16個通道共享一個中斷信號EDMA_INT,傳輸結束后,EDMA控制器負責向CPU發送通道數據傳輸結束的中斷,而且C6455允許多個EDMA通道擁有相同的傳輸結束代碼值,使CPU執行相同的中斷服務子程序,并在中斷服務程序中,清除相應的中斷標記。此外,事件鏈接EDMA通道功能可以使一個EDMA傳輸完成后鏈接到其他通道的傳輸,這里設置為NULL,表示鏈接到一個空的通道參數集,EDMA傳輸停止,其他傳輸的數據可以在EDMA初始化過程中利用CSL_Edma3ParamSetup以及其他CSL函數按照實際需求進行調整,源/目的地址可以在程序中用到時再進行賦值。

2.2.4 中斷初始化

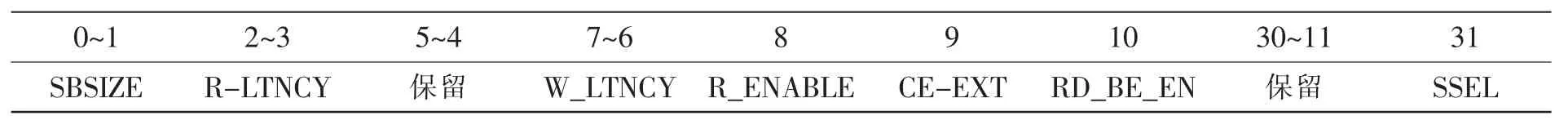

C6455的每個中斷都有對應的映射事件,且事件編碼是固定的,根據項目需求,要讓INT5映射到GPIO5,根據表2得知,GPINT5即GPIO 5中斷對應的事件編號為56,事件編號直接設置為0x38。

表2 中斷對應的映射事件

利用CSL實現C6455的中斷配置過程,調用CSL_intcInit函數初始化中斷模塊,使能不可屏蔽中斷NMI,并調用CSL_intcGlobalEnable函數全局中斷使能,利用 CSL_intcOpen函數打開中斷模塊將GPIO5中斷時間映射到系統中斷INT5,然后調用CSL_intcPlugEvent-Handler函數綁定中斷服務程序,最后使能該事件開始監聽,至此中斷機制配置完成,下一步進行中斷服務程序的編寫。

中斷服務程序的配置過程,包括兩個部分,第一部分是GPIO5等CPU觸發的外部中斷,當FPGA信號上升沿觸發有效時,CPU事件觸發并調用該中斷服務函數開始EDMA搬數;第二部分是DSP內部EDMA的中斷,根據上一節EDMA的原理,EDMA搬數完成后也會產生一個數據傳輸結束中斷,同時標志符將賦值為1,表明數據搬移完畢,然后CPU開始進行圖像處理。CPU圖像處理結束后,利用EDMA方式將得到的目標點坐標信息按數據解析格式返回給FPGA,DSP任務完成。

3 圖像處理系統的軟件設計

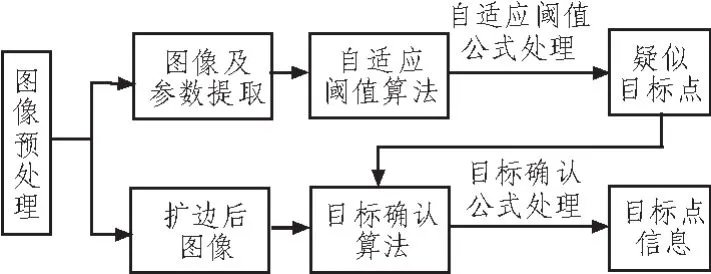

圖像處理是對EDMA導入C6455的內部數字圖像數據進行處理,通過圖像及參數提取、自適應閾值算法等,提取出目標信息,稱為疑似目標點。在此基礎之上,通過目標確認算法,即利用對比度關聯域值計算分割功能提取FPGA預處理的擴展圖像中疑似目標點的目標區域和背景區域,并按遙控參數要求計算鄰域相關對比度,完成目標確認過程。最后得出最終的目標坐標位置,將坐標位置信息返回FPGA。圖像處理算法流程如圖5所示。

圖5 圖像處理算法流程

3.1 背景圖像的提取與更新

DSP接收到的圖像為擴展后的全幅圖,而實際DSP進行圖像處理時的圖像為未擴邊的背景圖像,因此,需要從擴展圖像中先提取出實際的背景圖像。通過傳輸的圖像數據及參數,得到擴展的邊長,從而確定實際圖像在擴展圖像中的起始及終點坐標,以便進行圖像處理。

一幀圖像處理結束,得到目標點坐標信息,DSP按照數據解析協議將目標點打包后按照EDMA方式發送給FPGA,隨后對下一幀的圖像進行讀取和處理,直到所有幀的圖像都處理完畢。在DSP收到中斷時,EDMA將搬移經FPGA預處理的背景圖像數據,并覆蓋掉上次讀取的圖像數據,更新之后,進行本次的圖像處理過程。

3.2 目標點檢測和確認

通過對圖像數據進行分塊處理,按照水平掃描、垂直掃描方向的坐標變化直接對圖像數據進行重組,按行列方向找尋8*8小圖像坐標,能夠求取每個8*8小圖的閾值Ts,并根據Ts進行判斷,從而得到疑似目標點,此即為自適應閾值算法,具體計算如公式(1)所示:

其中μs、σs分別為塊圖像的均值和均方差,k為可調門限控制參數且由FPGA根據返回的目標點個數進行調控。

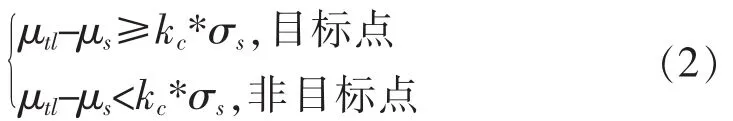

疑似目標點的確認過程,就是在自適應閾值算法的基礎之上,以疑似目標點為中心,以擴邊后的圖像為背景圖像,取小的目標區域和大的環狀背景區域進行處理,利用公式(2)完成確認過程:

其中,μtl、μs、σs分別表示目標區域均值、 背景區域均值 (環形)和環形背景區域均方差,kc參數為FPGA提供。通過相互比較,確認疑似目標點是否滿足條件。隨后,遍歷整個圖像數據,依次求出相應子圖像滿足條件的目標點,并將其坐標信息存儲下來。

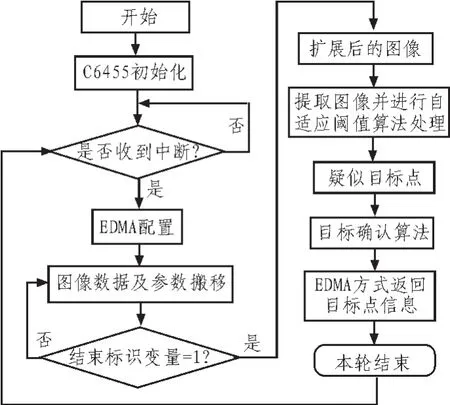

3.3 軟件設計

C6455實現圖像處理的軟件設計,是在FPGA對圖像進行擴邊和求殘差等預處理操作的前提下,按照上述的圖像處理算法進行軟件設計,實現圖像處理的具體軟件流程如圖6所示。

圖6 C6455實現圖像處理的軟件流程圖

C6455完成初始化,在收到中斷后通過EDMA方式將參數及數據保存到內部存儲器,當標識變量賦值為1時表示EDMA本次搬數過程結束,然后完成背景圖像更新和參數數據提取。下一步,通過自適應閾值算法處理背景圖像得到疑似目標點,然后利用目標確認算法完成確認,最后以EDMA方式將滿足條件的目標點按照約定的格式打包發送給FPGA,這樣便完成了本次圖像的目標點檢測和信息獲取。

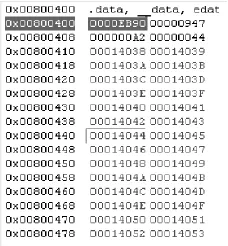

4 實現結果

搭建好DSP和FPGA硬件平臺,通過測試,發現DSP在讀取數據時仍存在數據丟包的現象。因此,需要進一步對底層配置進行完善,即對EDMA初始化和中斷初始化部分進行修改。通過不斷地調試和修改,最終程序編譯通過。如圖7所示,模擬圖像數據輸入之后,讀入的數據順利寫到DSP內存,紅色即為讀取的數值,實現了與FPGA間的基本通信。

在讀取數據后,DSP直接對讀入的圖像數據進行算法處理,并最終以EDMA方式將確定后的目標信息成功返回給了FPGA。

圖7 系統調試結果

5 結束語

文中以TMS320C6455芯片為核心,通過對C6455芯片的EMIF和EDMA等模塊部分的研究,參考相關的CSL驅動程序,實現了數字圖像目標點的檢測,且最高可完成DSP與FPGA之間64位高速數據通信。測試結果證明,該設計能夠有效地實現數字圖像目標點的有效檢測,實時性好,可以為其他的圖像實時處理等相關項目提供借鑒。

調試過程中,EDMA模塊的初始化實現是最關鍵的部分,也是實驗最具挑戰的部分。在滿足系統設計要求的前提下,其搬移數據存儲的大小端模式、確定搬數選用的通道、搬數的源地址及目的地址、傳輸數據的長度以及是否有DMA中斷響應等都是要考慮的問題。此外,在雙FPGA與雙C6455系統協作進行圖像處理過程中發現實際的數據吞吐速率距離理論速率有一定的差距。如何解決C6455與FPGA之間相互協作的高效性,如何進一步優化圖像數據讀取和處理的算法,以便更好地提高數據吞吐率,是下一步的研究方向。

[1]董言治,婁樹理,劉松濤.TMS320C6000系列DSP系列結構原理與應用教程[M].北京:清華大學出版社,2014.

[2]韋金辰,李剛,王臣業,等.TMS320C6000系列DSP原理與應用系統設計 [M].北京:機械工業出版社,2012.

[3]江思敏,劉暢.TMS320C6000系列DSP應用開發教程——DSP應用開發教程系列[M].北京:機械工業出版社,2005.

[4]鄭阿奇,孫承龍.DSP開發寶典[M].北京:電子工業出版社,2012.

[5]劉偉,王瑋,盧恒煒,等.DSP原理與應用系列設計[M].北京:電子工業出版社,2012

[6]德州儀器公司.牛金海,等編譯.Code Composer Studio(CCS)集成開發環境(IDE)入門指導書,2010.

[7]汪安民,張松燦,常春藤.TMS350C6000 DSP實用技術與開發案例[M].北京:人民郵電出版社[z],2008.

[8]李方慧.TMS320C6000系列DSPs原理與應用[M].2版.北京:電子工業出版社,2003.

[9]孫進平,王俊,李偉,等.DSP/FPGA嵌入式實時處理技術及應用[M].北京:北京航空航天大學出版社,2011.

[10]Texas Instruments.TMS320C6455 Fixed-Point Digital Signal Processor[EB/OL].www.ti.com.

[11]Texas Instruments.TMS320C6455 Chip Support Library API Reference Guide[EB/OL].www.ti.com.

[12]Texas Instruments.TMS320C645x DSP Software-Programmable Phase-Locked Loop (PLL)Controller User's Guide[EB/OL].www.ti.com.

[13]Texas Instruments.TMS320C6000 DSP External Memory Interface(EMIF)Reference Guide[EB/OL]. www.ti.com.

[14]Texas Instruments.TMS320C645x DSP Enhanced DMA(EDMA3)Controller User's Guide[EB/OL]. www.ti.com.

[15]Texas Instruments.TMS320C645x DSP General-Purpose Input or Output(GPIO)User's Guide[EB/ OL].www.ti.com.

Application of TMS320C6455 in real-time image processing

LIANG He-bin1,2,FENG Shui-chun1,ZHOU Hai1,BIAN Chun-jiang1,WANG Xiao-yan1,MAO Bo-nian1

(1.National Space Science Center,Chinese Academy Sciences,Beijing 100190,China;2.University of Chinese Academy Sciences,Beijing 100190,China)

To search for the goal points in the digital image and realize the high-speed data communication between FPGA and DSP,a system based on the high-speed DSP-TMS320C6455 was developed.The hardware part is to emulate the input or output data,and C was applied to complete the software part by Code Composer Studio(CCS).The image processing system was designed and realized by software design and configuring External Memory Interface(EMIF)、Enhanced DMA(EDMA)and so on,which finished the task of real-time image processing and high-speed communication.From the experimental results,the Image Processing System is reasonable and ideal so that it totally satisfy the needs,it is a real-time system and works efficiently.Above all,the design is useful and can be applied to many other parts of Digital Image Processing.

TMS320C6455;digital image processing;DSP;EMIF;EDMA

TN919

A

1674-6236(2017)09-0179-05

2016-03-15稿件編號:201603185

梁賀斌(1991—),男,河南駐馬店人,碩士。研究方向:電子信息工程、計算機應用技術。