ISCP-D2PSK調制在突發通信中的應用

李寅博

【摘要】 根據符號內連續相位二進制差分相移鍵控(ISCP-D2PSK)調制解調原理,設計了一種基于FPGA的數字實現電路,并加入了多種擴頻方式。調制端使用ROM存儲基帶信號,由選擇邏輯控制其輸出。解調端將收到的基帶信號作歸一化處理,并進行信號到達檢測,最后由一個可變換不同解擴系數的解擴解調單元處理得到解調數據。該電路設計實現方便、占用硬件資源較少,用FPGA實現后的測試結果驗證了設計的正確性,并將其應用在了某高速運動平臺間的突發通信中。

【關鍵詞】 ISCP-D2PSK 連續相位 擴頻 FPGA實現

一、引言

符號內連續相位二進制差分相移鍵控(ISCP-D2PSK)調制解調方法是在信號調制中,不同的比特信息由符號內相位變化的累積量表示,接收端則通過積累一個符號內的相位變化累積量來實現信號解調,和碼元符號的絕對相位無關。此調制方式的符號間相位為連續變化,使信號有良好的功率譜,信號為準恒包絡,解調時可以避免初相、多普勒頻移等引起的符號間相位變化對信號解調的影響[1]。

在某些高速運動平臺間的突發通信中,多普勒頻移大、通信幀短、速率要求高、硬件資源緊張,如果用相干解調的方式,導頻信號會占用較多的幀長,降低有效通信速率,且實現復雜。

本文則將ISCP-D2PSK調制解調方法應用在了某高速運動平臺間的突發通信中,用FPGA實現了其數字調制和解調,發揮了其優點,并加入了不同的擴頻方式。最后對其進行了解調性能測試,結果表明與理論基本一致。

二、ISCP-D2PSK調制解調基本原理

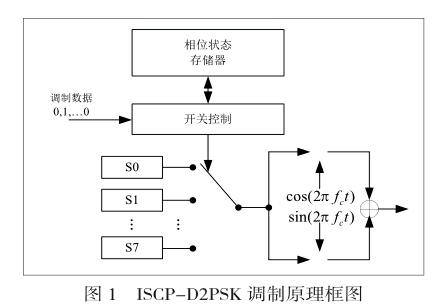

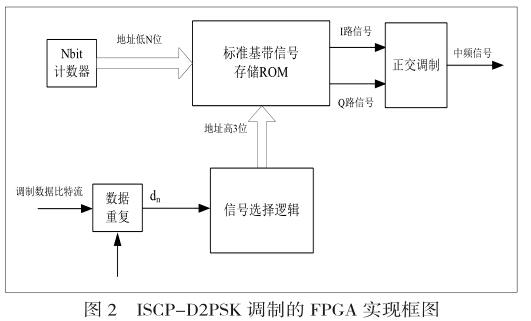

ISCP-D2PSK調制原理如圖1所示,基帶信號由信號選擇邏輯根據輸入比特符號和當前相位狀態在基帶信號集合中選擇一個基帶I、Q信號作為調制信號輸出,同時更新相位狀態存儲器中的狀態值。然后將I、Q信號進行正交調制得到中頻信號。

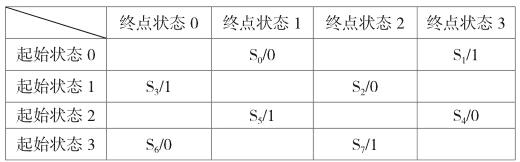

圖1輸入比特數據、基帶信號和狀態轉移的關系如表1所示,表中項目為“輸出基帶信號/輸入比特”。

表1 基帶信號選擇邏輯關系

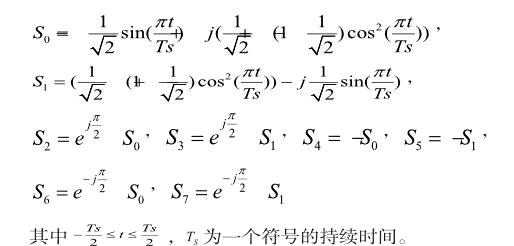

基帶信號集合中包含了8種復信號分別表示如下:

在解調時,對接收到的基帶信號,在一個符號持續時間內計算相位變化的累積量,并和標準相位變化累積量作比較,計算接收符號對應每一種可能發送比特的概率,選取概率最大的發送比特為當前接收信號的解碼信息輸出。

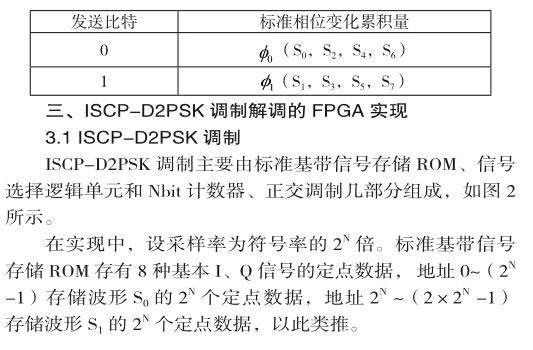

基帶信號集中的信號只有兩種不同的標準相位變化累積量,和不同的發送比特信息形成一一對應,其關系如表2所示,根據概率值即可選取出發送的比特信息。

表2 發送比特和相位變化累積量的對應關系

信號選擇邏輯根據輸入數據比特流按表1的關系生成基本I、Q信號選擇值i,i按符號率進行更新,并用其控制標準基帶信號存儲ROM的高3位地址。

Nbit計數器按采樣率進行自加,用其計數值控制標準基帶信號存儲ROM的低N位地址,即可將所選的一種基本I、Q信號的定點數據按順序輸出。最后將I、Q信號進行正交調制,輸出中頻信號。

本設計包括了多種擴頻方式,因此在前端對數據比特流進行了是否重復的處理。不擴頻將數據原樣調制,擴頻則將數據重復調制。

3.2 ISCP-D2PSK解調

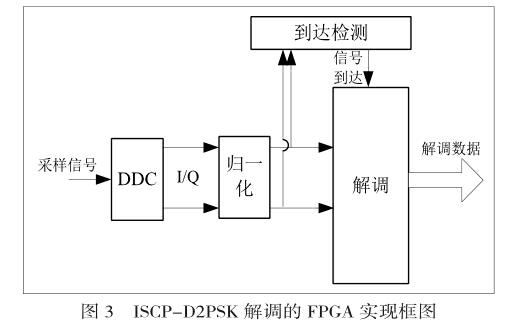

ISCP-D2PSK的解調器主要由數字下變頻(DDC)、歸一化、到達檢測、解調幾個單元組成,如圖3所示。

解調器首先將按符號率M倍采樣的數字信號通過DDC得到基帶I、Q數據,之后對I、Q數據進行歸一化處理。歸一化后的數據首先在到達檢測單元進行計算,當檢測到信號到來時,開始對數據進行ISCP-D2PSK解調。DDC按通用的數字下變頻實現方法設計[2],下面重點介紹其他幾個單元的實現。

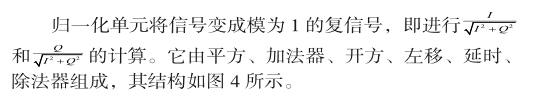

3.2.1歸一化單元

對采樣數據的歸一化處理是為了消除信號幅度受噪聲的影響,只保留噪聲對相位的干擾,同時也可以擴大解調的動態范圍。

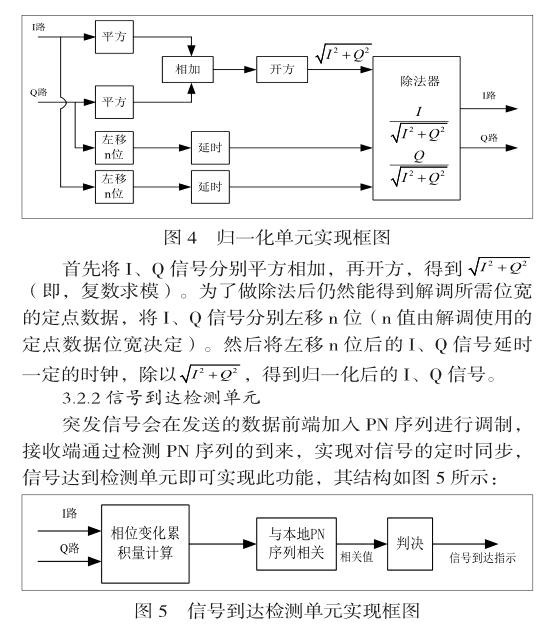

首先,將I、Q路信號進行數學運算,得到每個符號段的相位變化累積量,將結果與本地序列做相關,當沒有接收到正確信號時,相關值較小,當有信號到達時,相關值出現峰值。因此可以利用相關峰的變化來確定符號的開始,給出信號到達指示,開始信號解調。

3.2.3解調單元

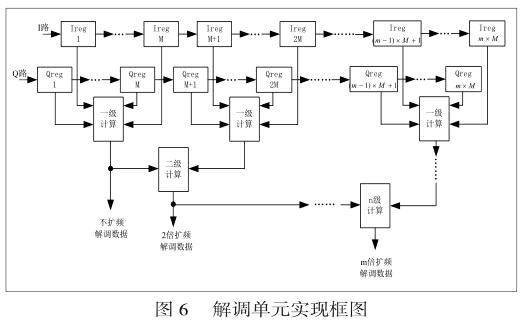

解調單元主要實現對數據的解擴解調,由擴頻系數控制不同的解擴解調,如圖6所示。

設采樣率為符號率的M倍,將I、Q路的采樣數據分別用m×M個移位寄存器存儲。按解調原理中描述的方法,對每個符號的采樣數據進行一級運算即可得到不擴頻的解調數據,對每兩個符號的采樣數據進行兩級運算即可得到2倍擴頻的解調數據,以此類推,對每m個符號的采樣數據進行n級運算即可得到m倍擴頻的解調數據(其中,2(n-1)=m)。

在實現中,將幾種擴頻系數的解調單元融合到一起,由擴頻系數控制取不同計算位置的數據,即可分別得到不同擴頻系數的解調數據。如此,節省了硬件資源,方便了多種解擴解調的自適應變換。

四、解調性能測試結果

按以上的方法在Xilinx的FPGA芯片上實現了ISCPD2PSK的調制解調算法,占用了較少的FPGA資源。

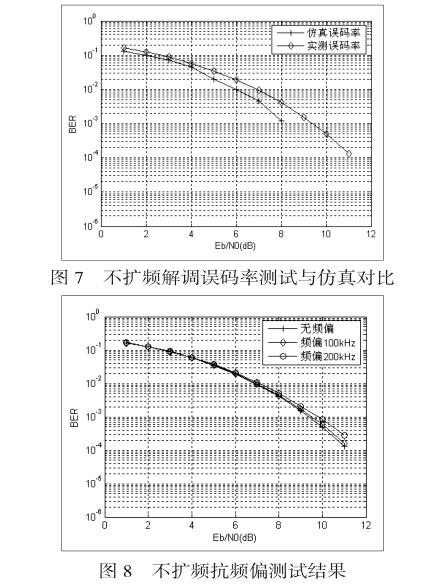

我們對實現后的解調性能進行了測試,圖7給出了不擴頻方式的解調誤碼率性能與仿真結果的對比。可以看出實測性能比仿真稍有下降,這是因為FPGA定點計算的損失和硬件底噪的影響。圖8給出了不擴頻方式的抗頻偏性能測試結果,可以看出頻偏在200kHz以內,對解調性能基本無影響。

五、結論

本文用FPGA實現了ISCP-D2PSK調制解調算法,并加入了多種擴頻方式。調制設計簡單,資源占用很少。解調設計時將不同擴頻系數的解擴解調在一個解調單元里實現,方便不同擴頻系數的自適應解擴解調變換,進一步節省了FPGA資源。測試結果驗證了FPGA設計的正確性,并將其應用在了某高速運動平臺間的突發通信中。

參 考 文 獻

[1] 張劍. 符號內連續相位差分相移鍵控調制方法[J]. 電訊技術,2010,50(8):63-66.

[2] 陳潔,林偉,黃世震. WCDMA 直放站數字下變頻的FPGA 實現[J]. 計算機與數字工程, 2011,259(5):153-156.

[3] 曹志剛,錢亞生. 現代通信原理[M]. 清華大學出版社,2000.

[4] 王金明. 數字系統設計與Verilog HDL[M]. 電子工業出版社, 2009