面向國產OS的PCI采集卡軟硬件設計與驗證

劉軍霞,楊先文

(1.河南省軍區自動化站,鄭州450003;2.信息工程大學,鄭州450004)

·微機應用·

面向國產OS的PCI采集卡軟硬件設計與驗證

劉軍霞1,楊先文2

(1.河南省軍區自動化站,鄭州450003;2.信息工程大學,鄭州450004)

為了滿足國產操作系統上數據采集的性能要求,在研究PCI采集卡原理的基礎上,提出一種基于FPGA和Linux的PCI采集卡軟硬件設計方案。硬件主要是對時鐘模塊、數據采集模塊、FIFO模塊和主控模塊等FPGA的控制邏輯進行設計,軟件主要包括應用程序和Linux驅動設計。驗證結果表明,軟硬件設計功能正確,并且與18 MHz時鐘頻率相比,高時鐘頻率采集性能提高了約15%至78%。當時鐘頻率為40 MHz時,采集速率不小于50.2 MByte/s,適用于數據采集速度要求較高的應用系統。

國產操作系統;Linux內核;PCI總線;采集卡;現場可編程門陣列;驅動

1 引言

數據采集系統廣泛應用于軍事、能源、航天等關鍵領域,如何將外界數據采集到計算機中,成為數據采集卡需要解決的問題。PCI(Peripheral Component Interconnect)是一種高性能局域總線標準,最大支持64位并行傳輸,工作時鐘可達66 MHz,傳輸峰值可達528 MByte/s,已成為眾多數據采集卡的接口方案[1-2]。

Linux作為一種支持多用戶、多任務、多線程和多CPU的開放式操作系統(operatingsystem,OS)內核,已被國產OS廣泛采納,出現了中標麒麟[3]等許多優秀產品。由于OS關系關鍵領域信息化的自主可控安全,因而推廣國產OS的意義重大。目前,針對PCI采集卡的驅動和應用程序設計大多針對Windows平臺[4-5],面向國產OS的軟件設計是亟待解決的問題。

為了適應國產OS數據采集系統要求,滿足關鍵應用領域對數據采集的現實需要,在研究PCI采集卡原理的基礎上,給出了PCI采集卡的軟硬件設計方案。驗證表明,面向國產OS平臺的軟硬件設計正確,采集性能滿足速率要求高的應用場合。

2 PC I采集卡原理

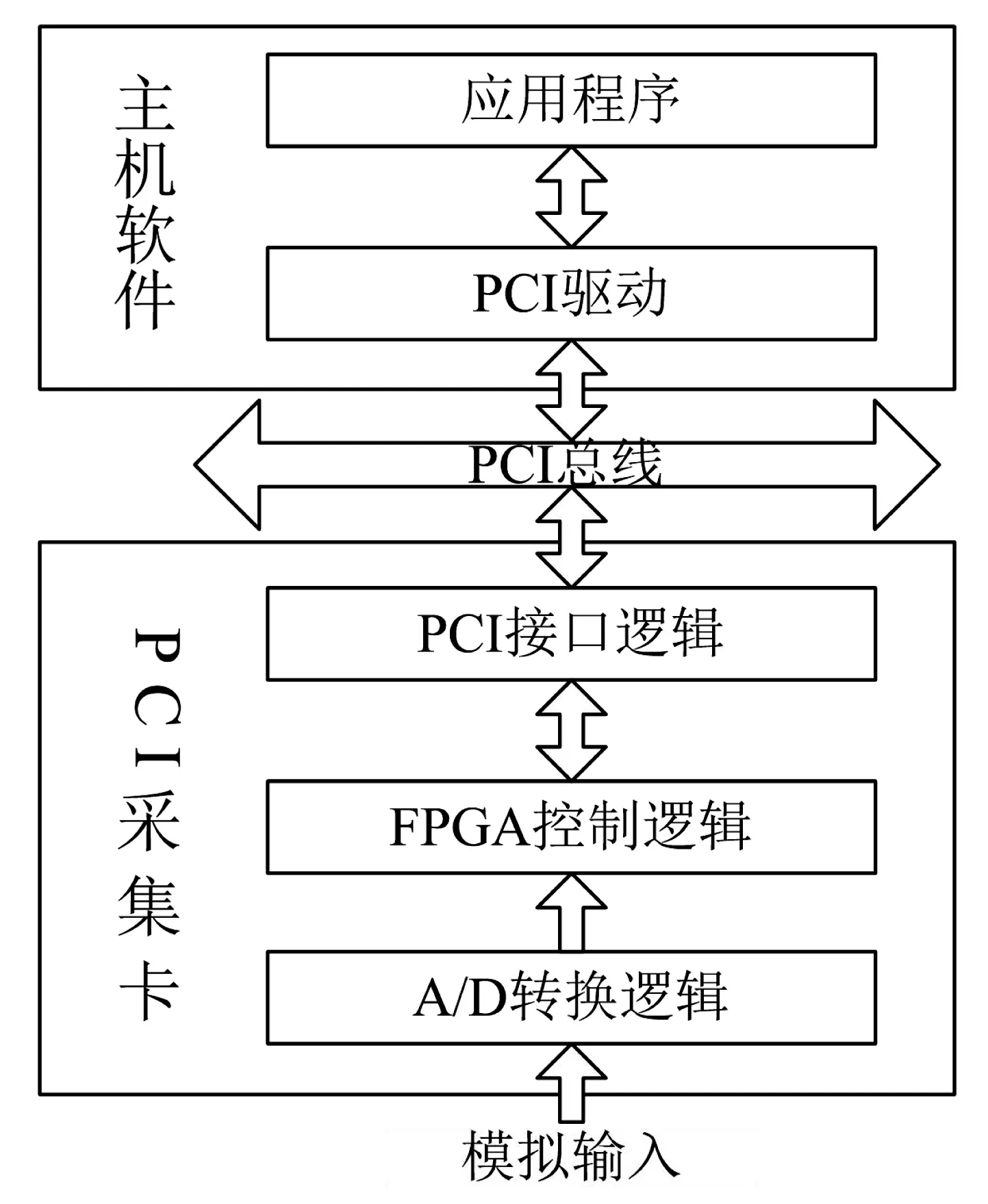

PCI采集卡軟硬件組成如圖1所示,主要包括PCI采集卡和主機軟件兩部分。PCI采集卡主要由A/D轉換邏輯、FPGA控制邏輯和PCI接口邏輯組成。基本工作原理:通過高速A/D轉換邏輯采集外部模擬信號,通過FPGA控制邏輯實現數據緩存,以及控制PCI接口邏輯執行DMA傳輸將緩存數據寫入主機內存中,便于主機對采集數據進一步處理分析。主機軟件主要包括應用程序和PCI驅動。

圖1 PCI采集卡軟硬件組成

在PCI采集卡中,A/D轉換和PCI接口邏輯一般采用專用芯片實現,例如PCI接口芯片采用PLX PCI9054,用戶只需根據其時序要求完成I/O交互即可。而FPGA芯片作為采集卡的可編程邏輯,承擔著對采集卡上所有時序和邏輯的控制任務,是PCI采集卡承前啟后的重要組成部分。因此,FPGA控制邏輯是PCI采集卡嵌入式硬件設計的主要內容。

3 FPG A硬件設計

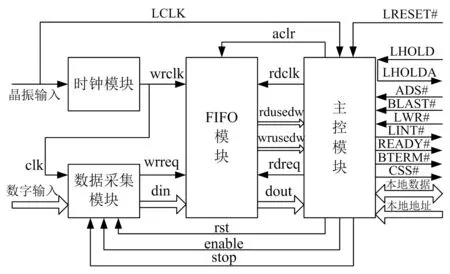

PCI采集卡的數據采集命令由主機發出,通過PCI9054的Target傳輸方式向FPGA控制邏輯傳送命令。當FPGA控制邏輯收到命令后,控制數據采集模塊實現對A/D數字信號的獲取,并將采集數據緩存至FPGA中例化的FIFO模塊中。當FIFO緩存容量滿足中斷觸發條件時,通過PCI9054向主機發送本地中斷請求,主機響應中斷后,通過PCI9054的DMA傳輸方式讀取FIFO數據至主機內存。FPGA控制邏輯的硬件設計原理如圖2所示。

3.1 時鐘模塊

圖2 FPGA控制邏輯設計原理

時鐘模塊主要向數據采集模塊提供采樣時鐘,并向FIFO模塊提供數據寫入時鐘wrclk。由于FIFO穩定工作時要求寫時序不大于讀時序,因此時鐘模塊一般是將晶振輸入分頻后作為數據采集模塊和FIFO寫入端的時鐘輸入。在FPGA中,大多集成有成熟的時鐘分頻裝置,例如:Altera的FPGA都帶有一個或多個PLL(Phase Locked Loop),可有效的對時鐘進行分頻、倍頻和延時等處理。Xilinx的FPGA中集成的DCM(Digital Clock Manager),可有效的對時鐘進行分頻、去skew和相移等處理。

3.2 數據采集模塊

數據采集模塊主要是采集數字輸入信號,產生FIFO的寫請求wrreq及寫數據din。若數字輸入位寬和寫數據din位寬 不相等(一般地, ),則需要計數??W??個時鐘周期產生的wrreq,同時?W?將?W?個時鐘周期內采集到的輸入信號級聯作?W?為寫數據din。在設計中,多周期內輸入信號的級聯采用移位寄存器方式實現。

此外,由于數字輸入所用時鐘和采樣時鐘clk分屬不同的時鐘域,在使用clk對數字輸入進行異步采樣時,若數字輸入不滿足采樣觸發器的建立時間(Tsu)和保持時間(Th),就可能產生亞穩態[6]。在設計中,采用對異步信號進行同步處理方式消除亞穩態,通過多級寄存器提取邊沿信號方式,保證采樣數據的穩定性。

3.3 FI FO模塊

為了實現數據采集和PCI9054本地傳輸的速度匹配,設計異步FIFO緩存采樣數據。具體地,采用FPGA內部塊存儲器例化FIFO模塊方式設計,在最大限度利用FPGA存儲資源的同時,可使得設計更加靈活高效。目前,Altera和Xilinx的FPGA都提供FIFO例化功能,根據需要設置FIFO深度及其接口,即可完成FIFO模塊設計。在本文中,我們基于Altera的EP1C12Q240C8型FPGA,設置FIFO深度為16 KB,FIFO接口包括aclr,wrclk,wrreq,din,wrusedw,rdclk,rdreq,dout,rdusedw。

3.4 主控模塊

主控模塊是FPGA控制邏輯最關鍵的設計,主要包括以下功能:

(1)控制數據采集模塊

當LRESET#有效時,通過rst復位數據采集模塊。當接收到數據采集命令時,解析該命令后置enable有效,使能數據采集模塊工作。設置FIFO為計數wrusedw的上限,當wrusedw達到上限時,置位stop有效關閉數據采集功能,待FIFO數據讀取至wrusedw低于上限時,置stop失效,開啟數據采集功能。

(2)控制FIFO讀取

當LRESET#有效時,通過aclr清除FIFO模塊工作狀態。設置FIFO為可讀計數rdusedw的下限,當rdusedw達到下限時置LINT#有效,向主機發送本地中斷請求。當接收到DMA傳輸命令時,解析該命令后置rdreq有效,通過DMA傳輸方式讀取FIFO數據到主機內存中。

(3)控制PCI9054本地總線

當LHOLD#有效時,下一個時鐘置位LHOLDA#有效,允許PCI9054使用本地總線。通過ADS#,BLAST#,LWR#,本地數據和本地地址接收主機命令,當接收到數據采集命令時,解析命令內容(由本地數據輸入)置enable有效或無效;當接收到DMA傳輸命令時,解析命令內容(由本地地址輸入)置rdreq和READY#有效或無效。根據FIFO緩存容量是否滿足中斷觸發條件置LINT#有效或無效。同時,為了本地總線正常工作,置CCS#無效,通知PCI9054不選擇配置寄存器;置BTERM#無效,通知PCI9054當前突發操作始終連貫完成。

4 Li nux軟件設計

4.1 應用程序設計

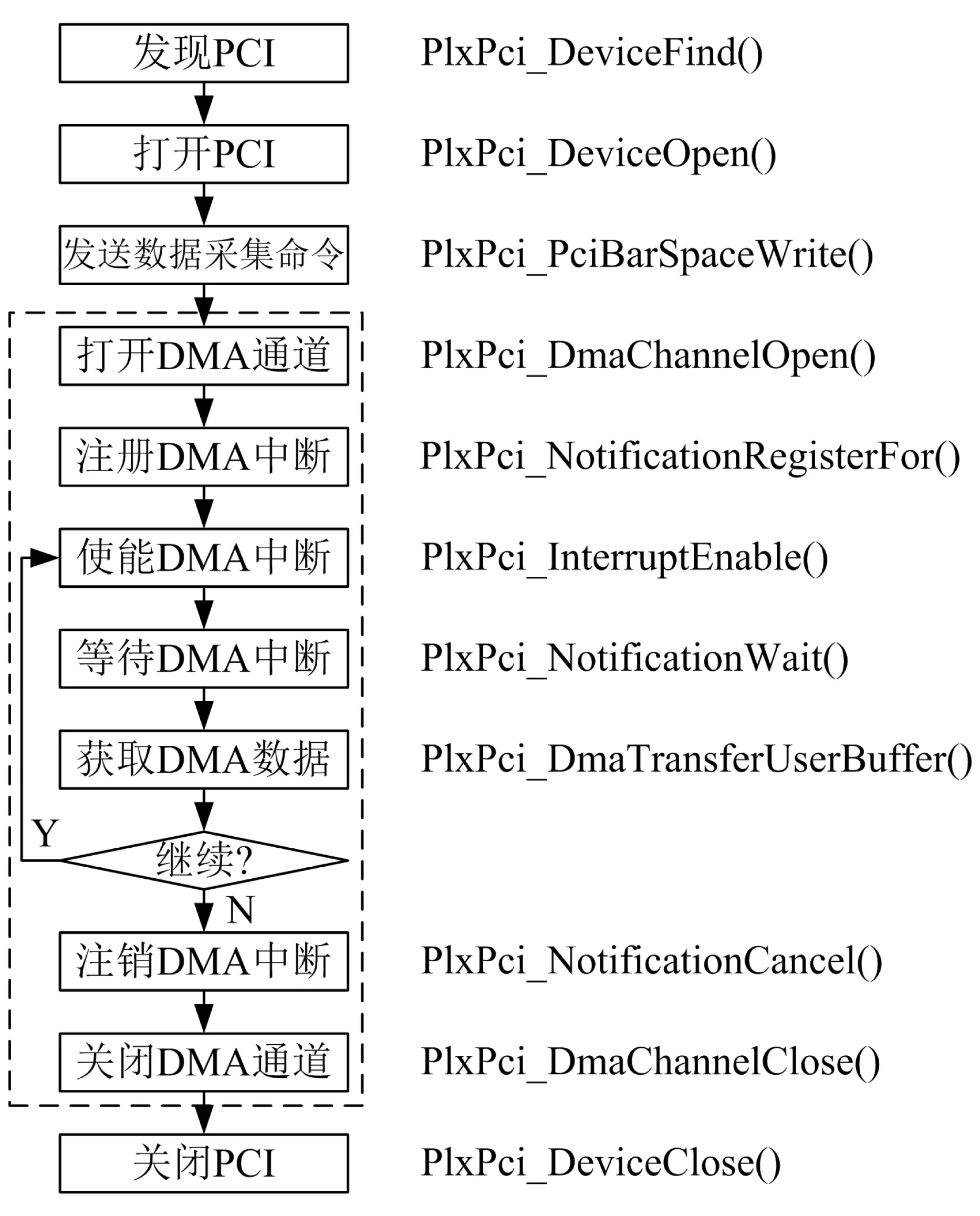

為了快速使用PCI芯片,PLX公司提供了成熟的軟件開發套件(Software Development Kit,SDK),包括一整套PCI9054的API訪問接口[7]。基于PLXAPI接口,本文所述的PCI采集卡應用程序流程及關聯API如圖3所示,主要包括5個環節:發現PCI、打開PCI、發送數據采集命令、DMA傳輸和關閉PCI。

在應用程序設計中,需要注意以下問題:

(1)發送數據采集命令是通過PlxPci_PciBar-Sp-aceWrite()向PCI本地指定地址寫入1個Bit-Size8數據實現的。BitSize8理論上可編碼256個系統命令,滿足大多數應用的命令編碼空間需求。

(2)使用PlxPci_DmaChannelOpen()打開DMA通道時,需使用PLX_DMA_PROP結構數據定義通道屬性,本文定義為:

PLX_DMA_PROP DmaProp;

memset(&DmaProp,0,sizeof(DmaProp));

DmaProp.ReadyInput=1;

DmaProp.Burst=1;

DmaProp.BurstInfinite=1;

DmaProp.SglMode=1;

DmaProp.DoneInterrupt=1;

DmaProp.ConstAddrLocal=1;

DmaProp.LocalBusWidth=2。

圖3 應用程序流程及關聯API

(3)使用 PlxPci_NotificationRegisterFor()注冊DMA中斷時,需使用PLX_INTERRUPT結構數據定義中斷屬性,本文定義為:

PLX_INTERRUPT PlxInt;

memset(&PlxInt,0,sizeof(PlxInt));

PlxInt.LocalToPci=(1<<DMAChannel);

其中,DMAChannel表示DMA通道,一般為0或1。

(4)使用PlxPci_DmaTransferUserBuffer()獲取DMA數據時,需使用PLX_DMA_PARAMS結構數據定義DMA參數,本文定義為:

PLX_DMA_PARAMS PlxParams;

memset(&PlxParams,0,sizeof(PlxParams));

PlxParams.UserVa=(PLX_UINT_PTR)pUserBuffer;

PlxParams.LocalAddr=LocalAddress;

PlxParams.ByteCount=sizeof(pUserBuffer);

PlxParams.Direction=PLX_DMA_LOC_TO_PCI。

其中,pUserBuffer為自定義內存指針,LocalAddress為自定義本地地址。LocalAddress應與FPGA控制邏輯中定義的DMA本地地址保持一致。

4.2 PC I驅動設計

在PLX SDK中,提供了PCI9054 Windows驅動程序。由于Linux系統具有差異性,只提供了Linux系統驅動開放解決方案,基于該方案,編譯中標麒麟操作系統驅動的步驟如下:

(1)uzip命令解壓PLX_SDK_Linux_*.zip,得到PlxSdk.tar,并拷貝到工作目錄下(建議為/usr/src/);

(2)tar命令解壓PlxSdk.tar,得到PlxSdk目錄;

(3)以編輯模式打開/etc/environment,按下語句設置系統環境變量:

export PLX_SDK_DIR=/usr/src/PlxSdk;(4)根據機器配置設置如下環境變量:export PLX_CPU_BIG_ENDIAN=1;export PLX_CPU_BITS=64。

(5)在Driver目錄下進行驅動編譯(使用builddriver或builddriverall命令),編譯后,Plx9054目錄中的Plx9054.ko就是PCI9054驅動。

驅動編譯完成后,在每次操作系統啟動時,使用Bin目錄下Plx_load(或Plx_unload)命令向驅動列表中加載(或卸載)驅動。加載成功后,PCI采集卡和應用程序才能正常交互,否則 PLX API將返回ApiNoActiveDriver錯誤。

5 實現與驗證

基于PCI DTK(V2.0)實驗板[8],在中標麒麟操作系統(V3.2.2)[3]下,對PCI采集卡的軟硬件設計進行了實現。FPGA控制邏輯基于Altera的EP1C12-Q240C8芯片實現,Linux應用軟件基于Qt環境[9]開發。為了檢驗設計的正確性及采集性能,采用兩個實驗進行驗證。

實驗1:采用FPGA實現方式,在數據采集模塊前端放置一個實驗數據產生邏輯,用來仿真A/D數字信號(此時A/D轉換邏輯不參與實驗)。在數據內容上,仿真數據可按某種規則產生(如使得相鄰兩個數據之差為1)。在Linux應用程序中增加數據檢查功能,通過檢查采集數據是否滿足數據產生規則,判斷設計是否正確。經過驗證,本文PCI采集卡軟硬件設計正確。

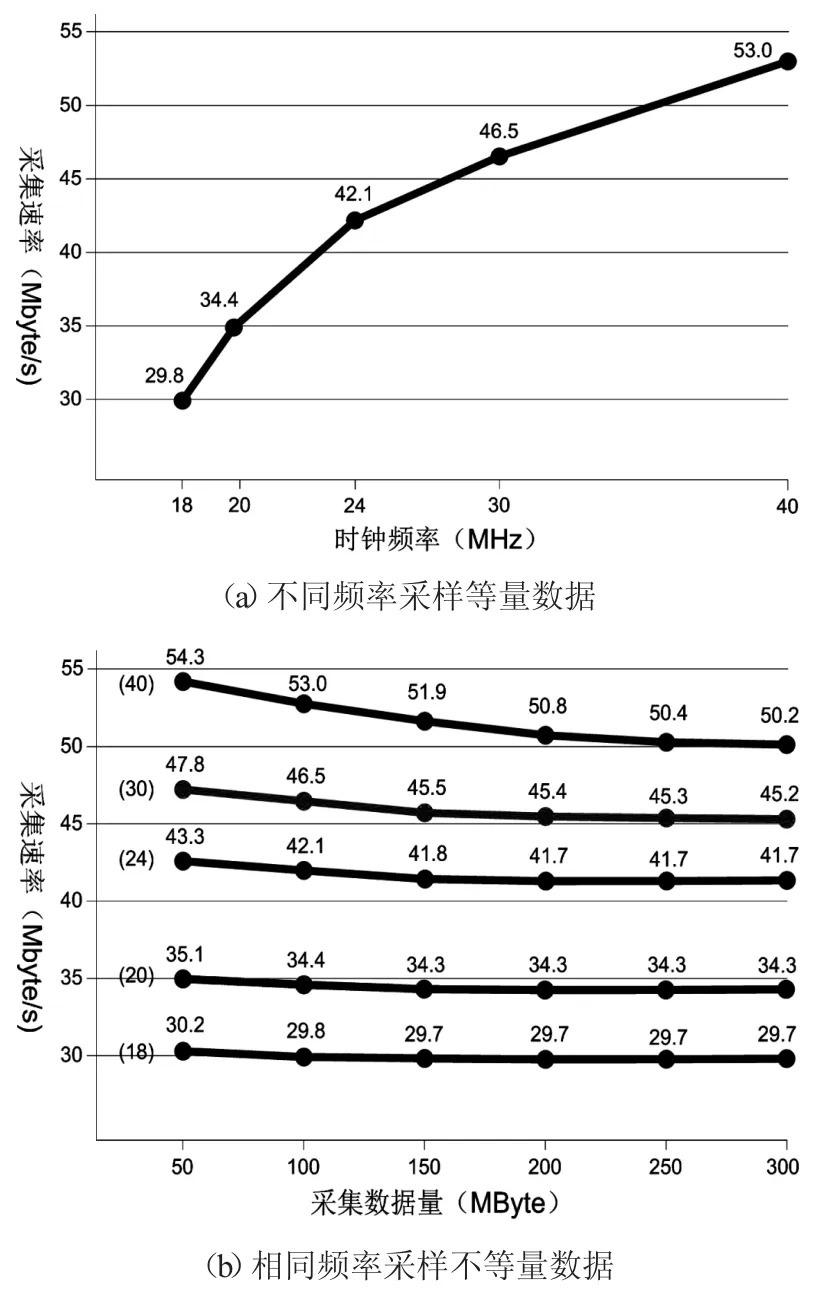

實驗2:采用多通道信號發生器產生隨機模擬信號,向PCI采集卡提供真實的模擬輸入(此時A/D轉換邏輯參與實驗)。為了檢驗PCI采集卡的效率,性能驗證包括兩部分:①以采集固定量的內存數據為目標,通過配置不同的FIFO寫入時鐘頻率(通過時鐘模塊分頻得到,也是數據采集模塊的采樣時鐘),比較應用程序多次運行的數據采集性能;②分別固定FIFO寫入時鐘頻率,以采集不同量的內存數據為目標,分別比較應用程序的數據采集性能。試驗結果如圖4所示。運行平臺為:中標麒麟64位操作系統(V3.2.2)、Intel酷睿I5處理器四核、主頻(3.2 GHz)、內存4 GByte。

圖4 PCI采集卡性能驗證

由圖4(a)可知,隨著FIFO寫入時鐘頻率的增大,PCI采集卡性能呈上升趨勢。相比于18MHz,20、24、30、40MHz效率分別提高了約15%、41%、56%、78%。由圖4(b)可知,從縱向角度看,可得出與圖4(a)類似的結論;從橫向角度看,對于每一時鐘頻率,隨著采集數據量的增多,PCI采集卡效率經歷下降階段后趨于平穩。當FIFO寫入時鐘頻率為40 MHz時,PCI采集卡性能不小于50.2 MByte/s,可滿足數據采集速度要求高的應用系統。

6 結束語

在軍事、能源、航天等關鍵領域,采用國產OS是保證信息安全的基礎。為滿足國產OS對數據采集的應用需要,提出了一種PCI采集卡的軟硬件設計方案,并檢驗了方案的正確性及實際性能,對實現PCI采集卡向國產OS的集成應用具有參考價值。

[1]王海明,胡金龍,吳麗華.基于PCI總線的高速數據采集卡設計[J].計算機測量與控制,2012,20(12):3393-3396. Wang Haiming,Hu Jinlong,Wu Lihua.Design of hignspeed data acquisition board based on PCI bus[J].Computer Measurement&Control,2012,20(12):3393-3396.

[2]馬濤,鄭鑫.基于PCI數據采集卡的高速多通道數據采集系統[J].電子技術應用,2015,41(2):75-77. Mao Tao,Zheng Xin.High speed multi-channel data acquisition systembased on PCI data acquisition card[J].Application ofElectronic Technique,2015,41(2):75-77.

[3]中標軟件.中標麒麟操作系統[EB/OL].[2016-01-18]http: //www.cs2c.com.cn/product/index.php?id=9 Standard Software.NeoKylin domestic operating system [EB/OL].[2016-01-18]http://www.cs2c.com.cn/product/index.php?id=9

[4]冉義兵,魏東,王義.實時圖像識別系統PCI驅動程序設計與開發[J].計算機工程與設計,2014,35(9):3337-3340. Ran Yibing,Wei Dong,WangYi.Design and development of PCI driver for real-time recognition systems[J].Computer EngineeringAnd Design,2014,35(9):3337-3340.

Design and Verification of Software and Hardware of PCI Acquisition Card for Domestic OS

Liu Junxia1,Yang Xianwen2

(1.Automatic Command Station,Henan Provincial Military Command,Zhengzhou 450003,China; 2.Information Engineering University,Zhengzhou 450004,China)

To meet the performance requirements of data acquisition in the domestic operating system,after researching the principle of PCI acquisition card,a design of software and hardware for PCI acquisition card based on FPGA and Linux is proposed.The hardware is mainly designed for FPGA control logic,including clock module,data acquisition module,FIFO module and main control module.The software mainly includes the design of application program and Linux driver.Validation results show that the design of hardware and software is correct,and the acquisition speeds of high clock frequency,compared with that of 18MHz clock frequency,are increased by about 15%to 78%, and the speed is not less than 50.2 MByte/s when the clock frequency is 40MHz,,which is suitable for the system with high requirements on the acquisition speed.

Domestic operating system;Linux core;PCI bus;Acquisition card;Field Programmable Gate Array(FPGA);Driver

10.3969/j.issn.1002-2279.2017.02.014

TP274.2

A

1002-2279-(2017)02-0059-05

劉軍霞(1973-),女,河南省滑縣人,高級工程師,主研方向:計算機網絡與信息安全。

2016-07-07