星務管理中的雙CPU冗余通信設計與實現(xiàn)

呂 聰,李華旺,常 亮

(1.中國科學院 上海微系統(tǒng)與信息技術研究所,上海 200050;2.上海微小衛(wèi)星工程中心 上海 201203)

星務管理中的雙CPU冗余通信設計與實現(xiàn)

呂 聰1,2,李華旺1,2,常 亮1,2

(1.中國科學院 上海微系統(tǒng)與信息技術研究所,上海 200050;2.上海微小衛(wèi)星工程中心 上海 201203)

基于Cortex-M3的Smart Fusion2芯片和APA600芯片結合雙CPU冗余技術設計實現(xiàn)了微納衛(wèi)星星務管理中的雙CPU冗余通信。采用雙CPU冗余技術來提高系統(tǒng)的可靠性。在信息交互設計中加入看門狗實現(xiàn)CPU狀態(tài)監(jiān)控,通過信息發(fā)送中握手通信機制的設置以及鏈路自復位的設置進一步提高系統(tǒng)的可靠性。詳細介紹了雙CPU冗余通信在星務管理系統(tǒng)中的實現(xiàn)并介紹了鏈路可靠性設計和雙CPU通信過程中的重要函數(shù)設計。利用可靠性高的串行通信方式設計雙CPU冗余通信即滿足微納衛(wèi)星對可靠性的高要求又降低了開發(fā)而且實現(xiàn)簡單這對于衛(wèi)星系統(tǒng)中的通信有較好的實用價值。

雙CPU;冗余通信;監(jiān)控;可靠性

隨著信息技術與小型化技術的飛速發(fā)展與應用,傳統(tǒng)的衛(wèi)星研制技術出現(xiàn)了革命性的飛躍。其中一個重要發(fā)展趨勢是衛(wèi)星小型化[1],小衛(wèi)星實現(xiàn)了低成本、小重量、小體積、高性能、短研究周期等特點[2]。衛(wèi)星越來越小,但對可靠性的要求越來越高。文中設計基于微納衛(wèi)星星務管理系統(tǒng),根據(jù)微納衛(wèi)星的高可靠性設計要求,以及一個單CPU的控制系統(tǒng)很難滿足現(xiàn)代控制系統(tǒng)的要求[3]的現(xiàn)狀,選用了雙CPU的冗余控制技術。由于雙CPU的冗余控制是一種提高系統(tǒng)可靠性的有效手段[4],設計為了適合衛(wèi)星可靠性要求選用雙CPU冗余通信。雙冗余技術就是在系統(tǒng)中增加備用模塊,一旦工作模塊發(fā)生故障時,控制系統(tǒng)可以快速切換到備用模塊,從而保證了系統(tǒng)的正常工作[5]。其中如何通過雙CPU通信保證系統(tǒng)的可靠性是本文的一個研究重點。

1 芯片選型

1.1 Smart Fusion2芯片介紹

主CPU選擇Microsemi公司Smart Fusion2SoC FPGA芯片(以下簡稱SF2),該芯片設計用于滿足高安全性、高可靠性和低功耗的基本需求。采用了基于非易失性快閃技術的設計保護功能,易于保護機密和高價值的設計,防止篡改、克隆、過度建造、反向工程和偽造。SF2芯片采用Flash工藝實現(xiàn),無需額外的配置存儲器以及刷新電路。同時SF2芯片上電即行,沒有上電加載時間,提高了衛(wèi)星啟動時間。SF2在單一芯片上集成了固有可靠性的快閃FPGA架構、一個 166(MHz)ARM CortexTM-M3 處理器、先進的安全處理加速器、DSP模塊、SRAM、eNVM和業(yè)界所需的高性能通訊接口。SF2器件具備所需的差異化特性,能夠確保在非常低的功耗下安全、可靠地運行。

1.2 APA600芯片介紹

從CPU選擇的是APA600芯片,APA600芯片是抗輻射的宇航等級的芯片。其相對于SF2有更高的可靠性但是它在功耗響應速度等方面卻沒有Smart Fusion2出色,所以選擇用高可靠性低性能的APA600來監(jiān)測高性能但可靠性相對差一點的SF2以使得整個系統(tǒng)的設計更加可靠并實現(xiàn)提高系統(tǒng)性能的目標。

2 雙CPU冗余通信設計

2.1 雙CPU冗余通信方式選擇

雙CPU間的通信方式有并行通信方式和串行通信方式。串行通信傳送按位順序進行,傳輸線少,成本低但傳送速度慢。但隨著當前通信行業(yè)的迅猛發(fā)展,串行通信技術日趨成熟,傳輸速率越來越快,可以進行長距離數(shù)據(jù)傳輸并保證信號傳輸質(zhì)量,加之其線路設計簡單,能很好地滿足保護裝置的通信要求,因此已經(jīng)越來越多的應用于雙CPU間的通信[6]。而異步串行通信也由于接線少、傳輸距離遠、可靠性高、成本低等特征在數(shù)據(jù)采集和控制系統(tǒng)中得到了廣泛的應用[7-8]。

考慮到數(shù)據(jù)量不是特別大,采用串行通信方式,并采用三線制和UART作為傳輸鏈路。其中UART發(fā)送信息是將需要發(fā)送的并行數(shù)據(jù)轉化為適合在信道中傳輸?shù)拇袛?shù)據(jù)串行輸出,接收時接收串行數(shù)據(jù),并將其轉化為并行數(shù)據(jù)[9-10]。SF2通過三線制向APA600發(fā)送控制指令,APA600接收到控制指令后通過三線制向SF2返回應答信息并且通過UART向SF2返回數(shù)據(jù)信號,SF2定時通過UART向APA600發(fā)送喂狗信號。為了避免UART和SF2的接收和發(fā)送數(shù)據(jù)時使CPU處于等待狀態(tài),接受和發(fā)送均采用中斷模式[11]。其基本的通信連接如圖1所示:

圖1 雙CPU通信連接圖

2.2 雙CPU冗余通信控制實現(xiàn)

這里的雙CPU控制區(qū)別于傳統(tǒng)的“熱備份”冗余控制,傳統(tǒng)的“熱備份”冗余就是兩個模塊同時在線工作,一個主模塊,一個從模塊,主模塊按照系統(tǒng)要求正常工作,從模塊處于熱備份狀態(tài),實時監(jiān)控主模塊工作狀態(tài),一旦檢測到主模塊出現(xiàn)故障,從模塊便可自動接管主模塊工作,系統(tǒng)可不受停機損失[12]。

星務系統(tǒng)的兩種工作模式分別為安全工作模式和正常工作模式,本設計選擇兩塊CPU,主CPU在正常模式下工作,從CPU在兩種模式下都有其任務。從CPU主要功能有兩個其一是正常工作模式下監(jiān)測可靠性低但性能好的主CPU并協(xié)助主CPU進行工作;另一個功能是在主CPU故障后擔任起整個系統(tǒng)的工作保證星務系統(tǒng)在安全模式下仍能完成衛(wèi)星基本的功能。

從CPU的APA600對SF2的監(jiān)控通過兩種途徑來實現(xiàn)。APA600作為從CPU要與主CPU的協(xié)同工作來滿足星務的需求,SF2向APA600發(fā)送控制指令,APA600向SF2返回應答信息并根據(jù)控制指令向SF2發(fā)送請求的數(shù)據(jù),通過該過程APA600實現(xiàn)對SF2的監(jiān)控;另一種監(jiān)控方式是通過設置看門狗實現(xiàn)監(jiān)控,SF2定時向APA600發(fā)送喂狗信號,若APA600在設定的時間內(nèi)沒有收到喂狗信號就會復位SF2,如果連續(xù)復位超過約定次數(shù)就斷定SF2不能正常工作,將SF2斷電,系統(tǒng)進入安全模式實現(xiàn)正常模式向安全模式的切換。

2.3 UART通信方式的可靠性設計

其中UART通信有兩種基本拓撲結構星型和總線型。由于需要點到點的通信在此選擇了星型拓撲結構全雙工處理方式。星型結構全雙工處理方式由于采用獨占線路只對單個節(jié)點實施全雙工對輪詢處理的效率并沒有影響。不過在這種方式下在主節(jié)點未發(fā)出命令的任何時間從節(jié)點可以主動向從節(jié)點傳送數(shù)據(jù)有利于處理比較緊急的通信任務所以這處理方式適用于從節(jié)需要主動上傳數(shù)據(jù)的場合[13-14]。

為提高數(shù)據(jù)傳輸?shù)目煽啃裕谲浖O計時,運用握手通信機制、CRC校驗碼等編程設計[15],并加入UART自復位設計。雙CPU通信過程中接受不到信息會有兩種原因,其一是發(fā)送端發(fā)生錯誤沒能將信息發(fā)出來,其二就是接收端發(fā)生錯誤未能將信息讀出來。針對第一種原因在UART鏈路設計中加入反饋復位信號設計,若對方?jīng)]收到信息將反饋一個信號給到UART發(fā)送端將UART進行復位,復位之后重新發(fā)送數(shù)據(jù)。針對第二種原因即發(fā)送端復位之后接收端仍不能接受到數(shù)據(jù)的情況下就需要檢查接受端自身的問題。首先接收端進行自復位,然后給發(fā)送端一個重發(fā)數(shù)據(jù)的信號,重新來接收數(shù)據(jù)。

3 軟件實現(xiàn)

3.1 SF2的看門狗設計

看門狗設計實現(xiàn)星務系統(tǒng)安全模式與正常模式的切換。SF2需要每一個任務周期 (500 ms)通過UART向APA600發(fā)送喂狗信號,給到APA600中,若APA600連續(xù)4 s未接到喂狗信號APA600將整個SF2復位。實現(xiàn)高可靠性的APA600對SF2的監(jiān)控功能。基于μCOS-II系統(tǒng)的SF2芯片的喂狗信號我們通過系統(tǒng)任務的時間間隔進行發(fā)送以確保喂狗信號的定時發(fā)出。

若SF2累計復位3次,則掉電SF2,系統(tǒng)進入安全模式。看門狗及復位管理的流程如圖2所示。

圖2 看門狗及復位管理流程圖

3.2 雙CPU冗余通信時序設計

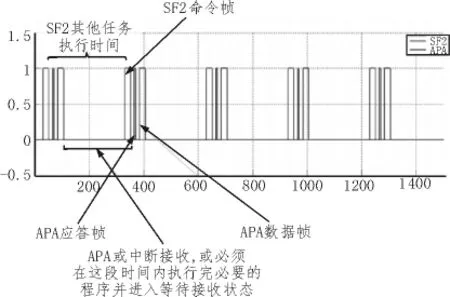

SF2向APA600發(fā)送控制指令并等待APA600的應答,應答分為兩類對于請求數(shù)據(jù)的指令APA600會將數(shù)據(jù)通過UART返給SF2,但是對于另一些控制指令并不需要返回數(shù)據(jù)信息,這時候要想確保APA600收到了SF2的指令就必須設置應答機制。雙機通信的時序設計如圖3所示。

圖3 雙CPU通信時序圖

3.3 雙CPU冗余通信的重要函數(shù)設計

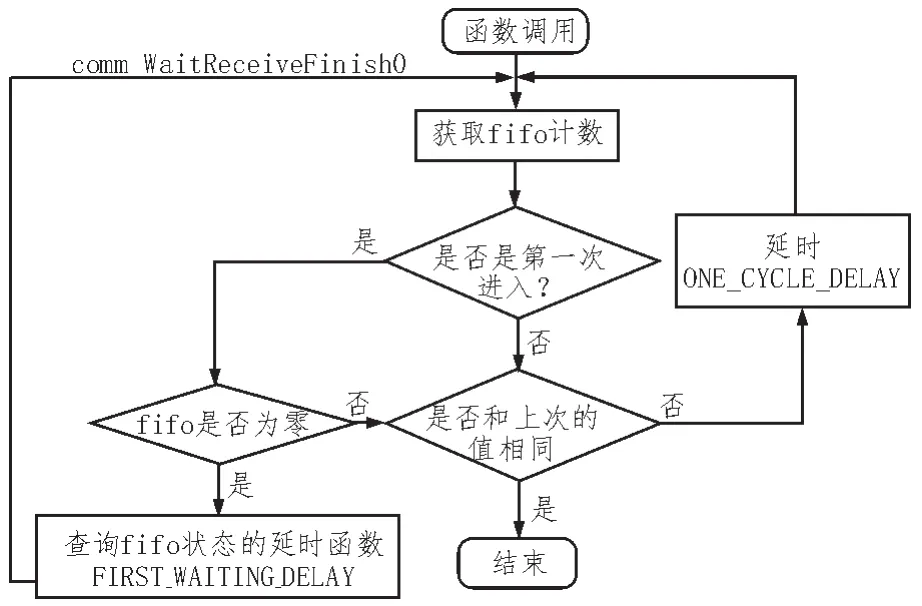

1)等待接受函數(shù)(commWaitReceiveFinish())設計

在雙機通信中很重要的一個工作是接受數(shù)據(jù),接收數(shù)據(jù)之前首先需要知道緩存中存在的數(shù)據(jù)以保證能完整的讀取數(shù)據(jù)。該等待接受函數(shù)的功能是等待接受緩存中完全收滿一幀數(shù)據(jù)之后返回接收到的數(shù)據(jù)個數(shù),使我們在接受數(shù)據(jù)之前可以確認緩存區(qū)的數(shù)據(jù)量,保證接受時可以收到完整的數(shù)據(jù)。函數(shù)實現(xiàn)流程如圖4所示。

圖4 等待接受函數(shù)流程圖

其中ONE_CYCLE_DELAY是每次等待的時間,這個延時要求必須大于下位機發(fā)送一個字節(jié)數(shù)據(jù)的時間(1/(波特率/8)秒)。為減少 CPU延時處理的占用,該時間小于下位機發(fā)送兩字節(jié)數(shù)據(jù)的時間,且該延時在SF2上必須小于APA600接收應答后開始到發(fā)送數(shù)據(jù)幀的時間(如圖5所示)。

圖5 幀間傳輸間隔設計

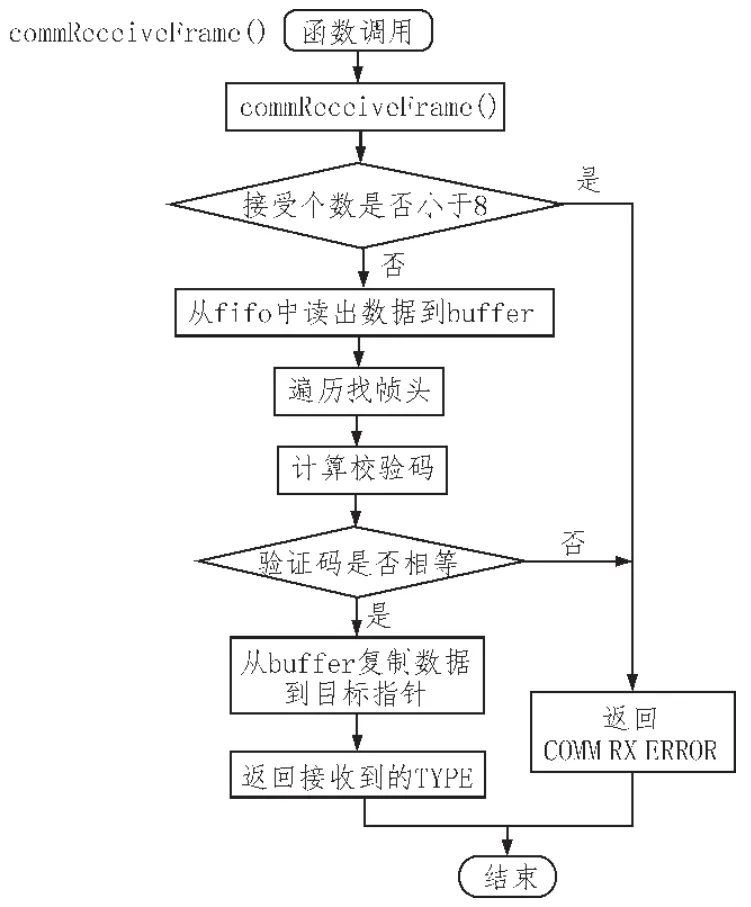

2)接受函數(shù)(commReceiveFrame())設計

接收函數(shù)的主要功能就是解析數(shù)據(jù)幀讀取數(shù)據(jù)并返回幀標識。實現(xiàn)雙CPU通信要保證雙CPU兩邊任務的同步性,任務同步的主要思想是網(wǎng)絡通信中的應答模式所以我們這里接收函數(shù)中要實現(xiàn)有應答的接受函數(shù)。接收函數(shù)的實現(xiàn)流程如圖6所示。

圖6 接受函數(shù)流程圖

3)發(fā)送函數(shù)(commSendWithACK())設計

發(fā)送函數(shù)設計圖如圖7所示。發(fā)送函數(shù)在發(fā)送數(shù)據(jù)后,等待接收應答幀。如果接收到正確解析的應答,函數(shù)直接返回 TRUE,接收到解析錯誤應答,則重發(fā);如果應答不成功,將進行數(shù)據(jù)重發(fā)直到重發(fā)計數(shù)大于設定值(SEND_ERROR_RETRY),重發(fā)次數(shù)大于設定值仍未成功時函數(shù)返回FALSE。其中重發(fā)數(shù)據(jù)的時間間隔根據(jù)下位機處理時間來設定。沒有接收到數(shù)據(jù),重發(fā)直到重發(fā)計數(shù)大于SEND_NOACK_RETRY時返回 FALSE。 重發(fā)時間間隔為 FIRST_WAITING_DELAY。

圖7 發(fā)送函數(shù)流程圖

4 結束語

文中的雙CPU冗余通信設計基于CortexTM-M3的Smart Fusion2芯片和宇航等級芯片APA600,通過UART以及三線制方式來實現(xiàn)兩個CPU之間的信息交互。APA600通過看門狗的喂狗信號的接受以及SF2控制指令的正常發(fā)送實現(xiàn)對SF2的監(jiān)控以及兩個CPU的協(xié)同工作。高性能芯片APA600的監(jiān)控以及對于UART自復位設計整體提高了整個系統(tǒng)的可靠性,保證了星務系統(tǒng)的任務的可靠執(zhí)行,使得系統(tǒng)性能更加符合微小衛(wèi)星對高可靠性的要求。

[1]林來興.現(xiàn)代小衛(wèi)星與納衛(wèi)星技術發(fā)展(2)[J].國際太空,2002(9):27.

[2]余金培,楊根慶,梁旭文.現(xiàn)代小衛(wèi)星技術與應用[M].上海科學普及出版社,2004(3):4-5.

[3]夏云非,黃凌.雙CPU通信接口設計[J].電子世界,2014(5):162.

[4]衡軍山,甄成剛.基于軟件的雙CPU冗余控制研究[J].微計算機信息,2005,21(7-1):59.

[5]衡軍山.基于雙CPU的冗余控制研究與實現(xiàn)[J].集成與液壓,2008,7(36):7.

[6]王躍,李博通,李斌,等.電力系統(tǒng)微機保護裝置中雙CPU通信方案及優(yōu)劣分析[J].電氣應用2009,28(5):34.

[7]鄭爭兵.一種基于FPGA的UART電路設計[J].國外電子測量技術,2010,29(7):85.

[8]楊瀾,戚秀真.UART微控制器設計方法及其FPGA實現(xiàn)[J].電子科技,2016,29(6):72.

[9]劉寶軍,王中訓,婁陽,等.基于FPGA的UART設計與實現(xiàn)[J].中國集成電路,2016(6):40.

[10]楊揚,葉芃,李力.基于FPGA的UART設計與實現(xiàn)[J].電子測量技術,2011,34(17):81.

[11]鄔芝權,靳桅.基于雙緩沖器的UART無線模塊設計[J].現(xiàn)代電子技術,2015,38(5):6.

[12]廖慧敏.PLC控制器的雙CPU冗余控制實現(xiàn)[J].湖北電力,2005,12(29):6.

[13]嚴利明,胡立坤,王慶超.基于UART的主從通信方式的主節(jié)點時序分析[J].電測與儀表,2006,43(487):51-53.

[14]胡立坤,王慶超.基于UART的可靠通信與性能分析[J].計算機工程,2006,32(10):15.

[15]董兵,許曉斐.RS-485總線系統(tǒng)通信可靠性設計與應用 [J].廣東輕工職業(yè)技術學院學報.2009,8(3):2.

The design and implementation of redundancy communication of dual-CPU in house-keeping system

LV Cong1,2,LI Hua-wang1,2,CHANG Liang1,2

(1.Shanghai Institute of Micro-system and Information Technology,Chinese Academy of Science,Shanghai 200050,China;2.Shanghai Engineering Center for Micro-satellite,Shanghai 201203,China)

The design and the implementation of dual-CPU redundant communication in house-keeping system of microsat based on Smart Fusion2 and APA600.Using the technology of Dual-CPU redundant to improve system reliability.Added Watchdog to monitor CPU's status in the design of information interaction.Though setting information of handshake communication mechanism and link self-reset to further improve the reliability of the system.Describe the implemented of dual-CPU redundant communication in house-keeping system and the desigh of link reliability and important functions in dual-CPU communication.Using serial communication mode not only meet the high reliability demand for micro-nano satellite but also reduces the development costs.It is also simple to achieve and has a good practical value in satellite communication system.

Dual-CPU; redundancy communication; monitor; reliability

TN915.04

:A

:1674-6236(2017)14-0092-04

2016-07-19稿件編號:201607140

市科委揚帆計劃(SHKW14YF01)

呂 聰(1990—),女,山東濱州人,碩士研究生。研究方向:星載計算機。