一種改進(jìn)型逐點(diǎn)比較圓弧插補(bǔ)算法的FPGA實(shí)現(xiàn)

韓賽飛+施佺+劉炎華+黃新明+孫玲

摘 要: 逐點(diǎn)比較圓弧插補(bǔ)作為一種常見(jiàn)的插補(bǔ)算法在數(shù)控系統(tǒng)中廣泛應(yīng)用。為了進(jìn)一步提高傳統(tǒng)插補(bǔ)算法的速度,通過(guò)分析逐點(diǎn)比較法的特點(diǎn)簡(jiǎn)化了給進(jìn)判別邏輯,提出一種改進(jìn)的逐點(diǎn)比較圓弧插補(bǔ)算法實(shí)現(xiàn)方案。充分利用Verilog HDL語(yǔ)言特點(diǎn),通過(guò)設(shè)計(jì)全局變量并使用FPGA豐富的內(nèi)部邏輯資源實(shí)現(xiàn)了算法精度的可調(diào)。算法的FPGA硬件驗(yàn)證結(jié)果表明該實(shí)現(xiàn)方案具有運(yùn)算速度快、插補(bǔ)精度可調(diào)和邏輯資源占用少的優(yōu)點(diǎn)。

關(guān)鍵詞: 圓弧插補(bǔ); Verilog 硬件描述語(yǔ)言; FPGA; 逐點(diǎn)比較法

中圖分類號(hào): TN492?34 文獻(xiàn)標(biāo)識(shí)碼: A 文章編號(hào): 1004?373X(2017)19?0153?03

Implementation of an improved circular interpolation algorithm

with point?by?point comparison based on FPGA

HAN Saifei, SHI Quan, LIU Yanhua, HUANG Xinming, SUN Ling

(School of Electronic Information, Nantong University, Nantong 226019, China)

Abstract: As one of the common interpolation algorithms, the circular interpolation algorithm with point?by?point comparison is widely used in numerical control systems. In order to improve the speed of the traditional interpolation algorithm, the characteristics of point?by?point comparison method is analyzed to simplify the feed discrimination logic, and an improved implementation scheme of circular interpolation algorithm with point?by?point comparison is proposed. With the use of feature of Verilog HDL, the global variable is designed and the rich internal logic resources of FPGA are used to realize the precision adjustment of the algorithm. The results of FPGA hardware verification show that the proposed scheme has the advantages of fast computation speed, adjustable interpolation precision and little logic resource occupation.

Keywords: circular interpolation; Verilog HDL; FPGA; point?by?point comparison method

0 引 言

數(shù)控技術(shù)是工業(yè)制造的基礎(chǔ),數(shù)控機(jī)床在進(jìn)行各種工件的輪廓加工時(shí),一般都要用到插補(bǔ)算法[1]。插補(bǔ)算法根據(jù)起點(diǎn)、終點(diǎn)和半徑等初始條件,實(shí)時(shí)計(jì)算工件加工過(guò)程中刀具移動(dòng)的軌跡及其坐標(biāo)值。數(shù)控插補(bǔ)算法主要有硬件和軟件兩種實(shí)現(xiàn)方法,其中,傳統(tǒng)的硬件插補(bǔ)電路是由小規(guī)模數(shù)字電路模塊搭建而成,不僅存在電路復(fù)雜、元器件多、體積和功耗大、可靠性低的不足,而且其加工速度和精度很難得到進(jìn)一步提高[2?3]。而軟件插補(bǔ)則受到計(jì)算機(jī)軟件運(yùn)算速度限制,插補(bǔ)的速度、精度等性能指標(biāo)也很難滿足高速控制要求[4?5]。隨著“中國(guó)制造2025”實(shí)現(xiàn)制造強(qiáng)國(guó)戰(zhàn)略目標(biāo)的提出,數(shù)控技術(shù)必將迎來(lái)新的發(fā)展機(jī)遇和挑戰(zhàn),高速、高精度的插補(bǔ)算法實(shí)現(xiàn)技術(shù)則是核心之一。

目前,插補(bǔ)算法主要有逐點(diǎn)比較法[6]、數(shù)字積分法[7]和數(shù)字比較法[8],其中,逐點(diǎn)比較法因?yàn)槠淇刂凭雀摺⑺惴ê?jiǎn)單成為在兩軸插補(bǔ)系統(tǒng)中最常用的算法。借助FPGA芯片集成度高、工作速度快、邏輯單元功能強(qiáng)大,并具有靈活性高和可反復(fù)編程的特點(diǎn)[9],本文針對(duì)現(xiàn)有逐點(diǎn)比較插補(bǔ)算法硬件實(shí)現(xiàn)的不足,提出一種改進(jìn)的基于FPGA的算法實(shí)現(xiàn)方案。采用可綜合的Verilog HDL語(yǔ)言完成了算法的硬件電路設(shè)計(jì),給出了仿真驗(yàn)證與結(jié)果分析。

1 傳統(tǒng)逐點(diǎn)比較圓弧插補(bǔ)算法

傳統(tǒng)的逐點(diǎn)比較插補(bǔ)算法流程分為偏差判別、坐標(biāo)給進(jìn)、偏差計(jì)算和終點(diǎn)判別4步。

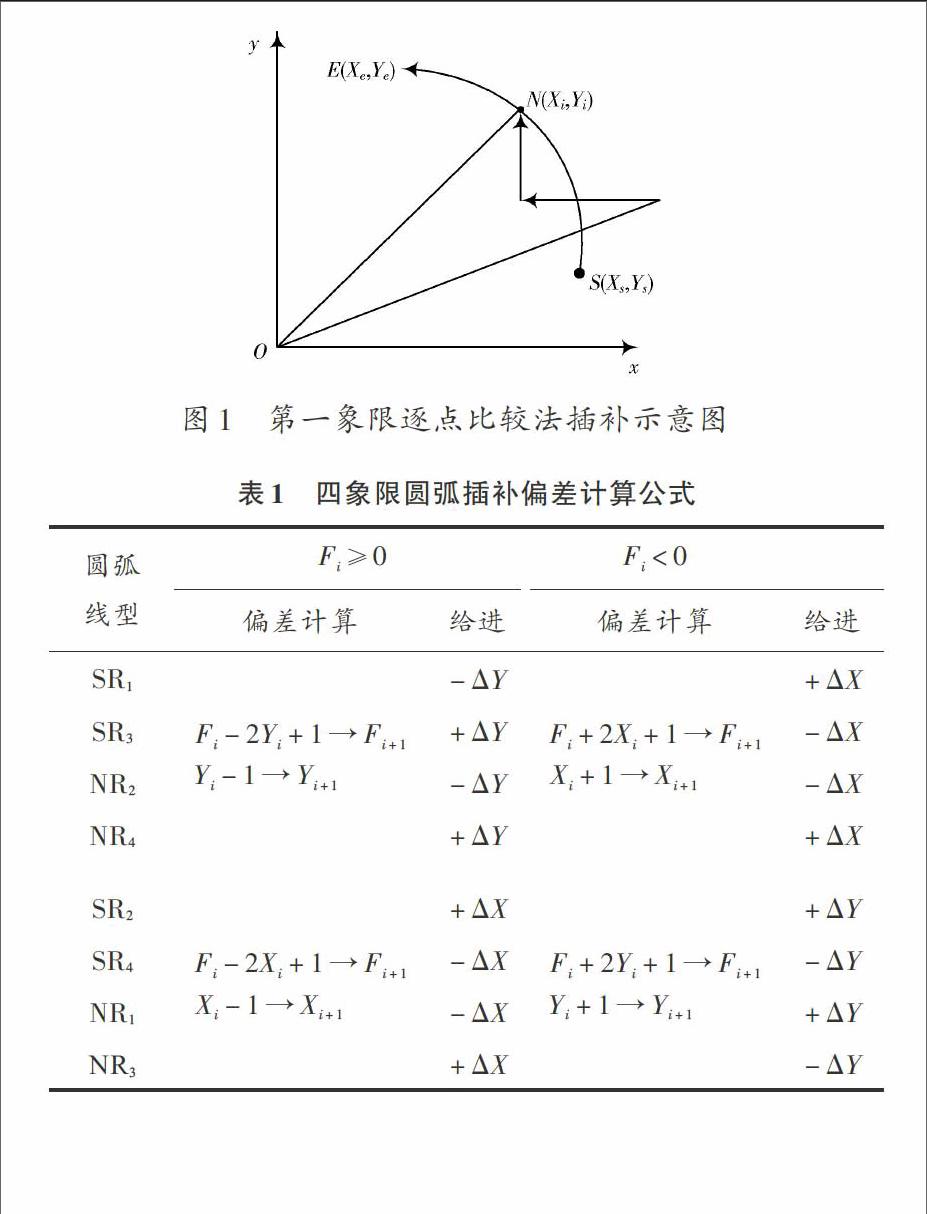

以圖1所示的第一象限內(nèi)一段逆圓弧為例,設(shè)其起點(diǎn)[S]的坐標(biāo)為[Xs,Ys,]終點(diǎn)[E]的坐標(biāo)為[E(Xe,Ye),][N(Xi,Yi)]為插補(bǔ)路徑上的動(dòng)點(diǎn),圓心為原點(diǎn)[O(0,0),]半徑為[R。]

為了表達(dá)動(dòng)點(diǎn)[N]與理想圓弧之間的位置關(guān)系,引入偏差函數(shù)[Fi=X2i+Y2i-R2,]根據(jù)[Fi]的正負(fù)情況來(lái)判斷動(dòng)點(diǎn)是在圓內(nèi)還是圓外,因此有如下插補(bǔ)規(guī)則:

(1) 當(dāng)[Fi>0]時(shí),動(dòng)點(diǎn)在圓外,給進(jìn)為[-ΔX。]

(2) 當(dāng)[Fi=0]時(shí),動(dòng)點(diǎn)恰好在圓上,給進(jìn)為[-ΔY。]

(3) 當(dāng)[Fi<0]時(shí),動(dòng)點(diǎn)在圓內(nèi),給進(jìn)為[+ΔY。]

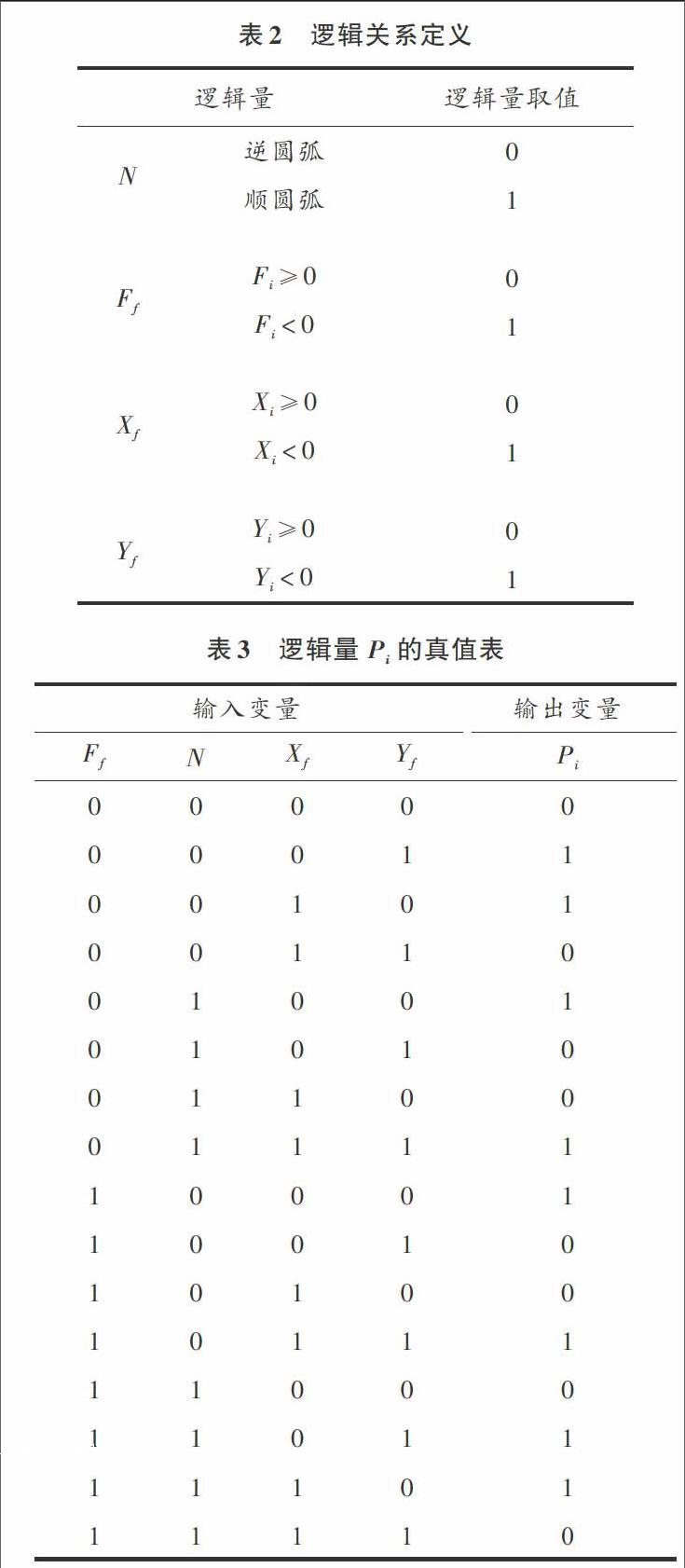

上述插補(bǔ)規(guī)則只局限于第一象限的逆圓,表1歸納總結(jié)了實(shí)際插補(bǔ)中可能出現(xiàn)的其他象限和順圓情況下的插補(bǔ)規(guī)則[10],其中,[SRi]([i=]1,2,3,4)代表第[i]象限的順圓弧,[NRi]([i]=1,2,3,4)代表第[i]象限的逆圓弧。

2 改進(jìn)型逐點(diǎn)比較圓弧插補(bǔ)算法設(shè)計(jì)與實(shí)現(xiàn)

由表1可見(jiàn),插補(bǔ)過(guò)程中首先需要判斷偏差的正負(fù),然后在確定的偏差情況下判斷下一步給進(jìn)[ΔX]或[ΔY]的多少。實(shí)現(xiàn)這一判別的直接方法就是通過(guò)多個(gè)條件語(yǔ)句依次進(jìn)行,其不足是判別速度慢,也不利于算法實(shí)現(xiàn)中精度的提高。為此,本文提出一種簡(jiǎn)化給進(jìn)判別條件的方法。

2.1 改進(jìn)的算法設(shè)計(jì)

通過(guò)分析表1,本文將偏差判別函數(shù)分為大于等于“0”和小于“0”兩種狀態(tài),并引入二進(jìn)制邏輯,將表1中的所有情況定義為表2所示的邏輯關(guān)系。本設(shè)計(jì)還引入了一個(gè)新的邏輯變量[Pi,]規(guī)定[Pi=0]時(shí),給進(jìn)[X;][Pi=1]時(shí),給進(jìn)[Y。]根據(jù)上述分析條件,可歸納出如表3所示的[Pi]真值表。

由式(1)首先可以確定給進(jìn)方向是[x]軸還是[y]軸,但無(wú)法判斷給進(jìn)的方向是正方向還是負(fù)方向,因此,需要再引入另外兩個(gè)邏輯量[Fx]和[Fy,]并設(shè)定:當(dāng)需要給進(jìn)[x]的正方向時(shí),[Fx=0;]給進(jìn)[x]的負(fù)方向時(shí),[Fx=1;]同理,當(dāng)給進(jìn)[y]的正方向時(shí),[Fy=0;]給進(jìn)[y]的負(fù)方向時(shí),[Fy=1。]綜合表1和表3可以得到[Fx]和[Fy]的邏輯表達(dá)式為:

[Fx=NYf] (2)

[Fy=NXf] (3)

通過(guò)式(1)~式(3)可以分別計(jì)算出[Pi,F(xiàn)x]和[Fy,]從而可以確定動(dòng)點(diǎn)下一步給進(jìn)方向。

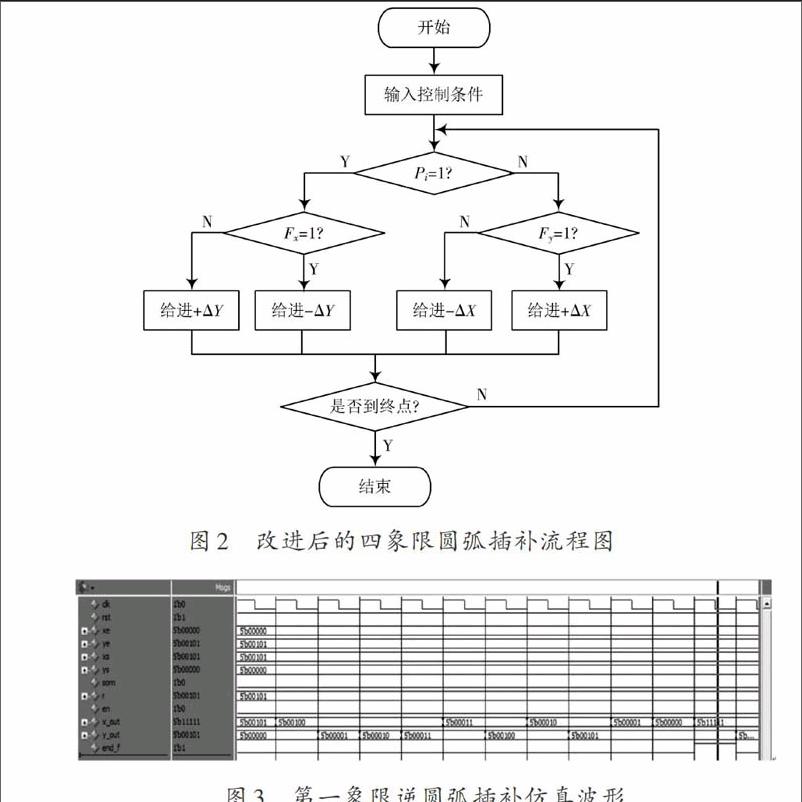

逐點(diǎn)比較法中,常通過(guò)比較動(dòng)點(diǎn)和終點(diǎn)的坐標(biāo)數(shù)值是否相等來(lái)判斷插補(bǔ)過(guò)程是否完成。然而,當(dāng)插補(bǔ)一個(gè)整圓時(shí),起點(diǎn)的坐標(biāo)和終點(diǎn)坐標(biāo)相等。這種情況下,上述判別方法不再適用。因此,本文在程序設(shè)計(jì)中引入了一個(gè)標(biāo)志寄存器[Q,]如果起點(diǎn)不等于終點(diǎn),寄存器[Q]置0,插補(bǔ)程序正常執(zhí)行;如果起點(diǎn)等于終點(diǎn),寄存器[Q]置1,先停止一拍,在下一個(gè)觸發(fā)脈沖到來(lái)時(shí),寄存器[Q]置0,然后即可進(jìn)行插補(bǔ)。本設(shè)計(jì)實(shí)現(xiàn)的改進(jìn)型圓弧插補(bǔ)算法流程如圖2所示。

2.2 改進(jìn)的算法實(shí)現(xiàn)

根據(jù)改進(jìn)后的逐點(diǎn)比較插補(bǔ)算法,在Quartus Ⅱ13.0和ModelSim 10.4軟件平臺(tái)下,本文完成了插補(bǔ)電路的可綜合Verilog HDL語(yǔ)言設(shè)計(jì),并進(jìn)行了仿真驗(yàn)證。選用CycloneIV E系列EP4CE6E22C6器件的條件下,仿真得到的第一象限逆圓弧插補(bǔ)波形如圖3所示。圖中,輸入的二進(jìn)制起點(diǎn)橫坐標(biāo)[Xs]為00101,起點(diǎn)縱坐標(biāo)[Ys]為00000;輸入的二進(jìn)制終點(diǎn)坐標(biāo)[Xe,Ye]為(00000,00101)。en為使能信號(hào),當(dāng)[en=0]時(shí),輸入端有效。Sorn為路徑方向信號(hào),當(dāng)Sorn=0時(shí),進(jìn)行逆圓弧插補(bǔ);Sorn=1時(shí),進(jìn)行順圓弧插補(bǔ)。x_out與y_out為輸出的動(dòng)點(diǎn)坐標(biāo);end_ f=1標(biāo)志插補(bǔ)過(guò)程結(jié)束信號(hào)。

改進(jìn)后的算法靈活性好,可以通過(guò)擴(kuò)大輸入起點(diǎn)、終點(diǎn)坐標(biāo)以及半徑的倍數(shù)來(lái)獲得更多的步進(jìn)點(diǎn)數(shù),從而提高插補(bǔ)的精度。圖4所示為步進(jìn)點(diǎn)數(shù)為100的[14]圓弧的插補(bǔ)軌跡,從圖4曲線可見(jiàn),刀具的運(yùn)動(dòng)軌跡與理想圓弧的擬合程度較好。圖5為起點(diǎn)坐標(biāo)和終點(diǎn)坐標(biāo)均為(50,0)的整圓插補(bǔ)軌跡。由于改進(jìn)了終點(diǎn)判別條件機(jī)制,本文方案可以完成一個(gè)整圓的插補(bǔ)過(guò)程。

可見(jiàn),本文改進(jìn)后的圓弧插補(bǔ)算法在相同條件下占用的硬件資源較少,這是因?yàn)楸疚脑O(shè)計(jì)的算法省去了大量的條件判斷語(yǔ)句,使得程序風(fēng)格簡(jiǎn)潔,不僅節(jié)省了邏輯資源,也大大提高了算法的速度和效率。

3 結(jié) 語(yǔ)

本文提出一種基于符號(hào)條件位判別的改進(jìn)型逐點(diǎn)比較圓弧插補(bǔ)算法,并進(jìn)行了FPGA仿真驗(yàn)證。驗(yàn)證結(jié)果表明,仿真波形與理論分析一致。與傳統(tǒng)的算法實(shí)現(xiàn)相比,本文方案具有插補(bǔ)速度快,占用資源少,插補(bǔ)精度高,輸出脈沖穩(wěn)定,硬件實(shí)現(xiàn)功耗低的特點(diǎn),并解決了傳統(tǒng)插補(bǔ)算法在起點(diǎn)與終點(diǎn)相同的情況下終點(diǎn)判別失效的問(wèn)題,可應(yīng)用于數(shù)控機(jī)床系統(tǒng)。

注:本文通訊作者為施佺。

參考文獻(xiàn)

[1] 肖力.FPGA測(cè)試控制系統(tǒng)[D].北京:北方工業(yè)大學(xué),2012.

[2] HAN Xingguo, WANG Binwu, WANG Weiqing. The research of open CNC system circular interpolation track based on kinetics and kinematics [C]// Proceedings of the Fifth IEEE Conference on Measuring Technology and Mechatronics Automation. Hongkong, China: IEEE, 2013: 1216?1218.

[3] 楊敬威.基于FPGA的數(shù)控硬件插補(bǔ)系統(tǒng)的研究與實(shí)現(xiàn)[D].西安:西安工業(yè)大學(xué),2013.

[4] 張偉,王黎.基于FPGA的數(shù)字積分法插補(bǔ)控制器設(shè)計(jì)與實(shí)現(xiàn)[J].現(xiàn)代電子技術(shù),2011,34(22):150?153.

[5] 王漢霆.基于FPGA的運(yùn)動(dòng)插補(bǔ)控制芯片的研究與設(shè)計(jì)[D].武漢:華中科技大學(xué),2009.

[6] 李莉,馮志永.數(shù)控系統(tǒng)中圓弧插補(bǔ)算法的改進(jìn)和實(shí)現(xiàn)[J].控制與檢測(cè),2009(7):61?62.

[7] 李存志,邢建國(guó).比較積分法直線、圓弧插補(bǔ)方法的改進(jìn)[J].機(jī)械設(shè)計(jì)與制造,2015(9):185?188.

[8] 陳宏臣.基于FPGA技術(shù)的數(shù)控插補(bǔ)器算法改進(jìn)研究[D].成都:西南交通大學(xué),2010.

[9] 王誠(chéng).Altera FPGA/CPLD設(shè)計(jì)基礎(chǔ)篇[M].北京:人民郵電出版社,2011.

[10] 席港港.傳統(tǒng)逐點(diǎn)比較法直線插補(bǔ)方法的改進(jìn)[J].山東理工大學(xué)學(xué)報(bào),2012,26(1):67?69.