多通道絕緣耐壓測試系統下位機及硬件設計*

許中原,周 驊,穆 杰

(1. 貴州大學 大數據與信息工程學院,貴州 貴陽 550025; 2. 開封文化藝術職業學院,河南 開封 475000)

多通道絕緣耐壓測試系統下位機及硬件設計*

許中原1,周 驊1,穆 杰2

(1. 貴州大學 大數據與信息工程學院,貴州 貴陽 550025; 2. 開封文化藝術職業學院,河南 開封 475000)

為了滿足對新型多接口器件的檢測需求,針對目前耐壓絕緣測試儀普遍通道少、自動化程度不高的問題,設計了一款多通道的耐壓絕緣測試系統。主要實現了高壓多通道可靠切換方式、測試數據自動化錄入和高效人機界面。通過實踐表明,該系統操作簡單,能夠對被測物高效檢測,快速反饋、數據自動化錄入,提高了測試效率,完成了系統所要求的各項指標和功能。

多通道;耐壓絕緣測試;智能化;下位機

0 引言

根據電子設備的安規測試要求,各種電氣設備、接口、連接器等電氣產品,在出廠之前必須進行規定電壓下的絕緣耐壓強度試驗,以考核產品的絕緣水平,衡量過電壓的能力,反映產品的電氣安全性能[1-2]。目前市場上的這類設備單通道居多,測試效率低,不支持模塊化的元件治具,需要人工參與較多,測試設備的記錄和分析功能有待提高[3]。針對以上問題和不足,本文設計了一款集多通道、自動化、數據處理的耐壓絕緣測試系統,有效解決目前設備對新型多測試點元器件測試只能分時檢測的問題。

1 系統整體架構設計

系統從靈活性考慮,主要分為上位機和下位機部分,上位機與下位機通過USB通信[4]。上位機采用PC平臺,包含人機界面和數據庫;下位機使用STM32處理器,主要包含多通道掃描模塊、MCU控制模塊、高壓電源模塊。其中多通道掃描模塊主要是實現多通道的掃描和切換,高壓電源模塊主要是產生高壓電源,MCU控制模塊主要是實現上位機命令解析和配置命令下發[5]。系統整體設計架構如圖1所示,本文主要介紹硬件電路設計部分和下位機程序設計部分。

圖1 系統整體架構

2 系統硬件電路及下位機設計

硬件電路部分和下位機部分是整個系統設計的關鍵部分。根據實際檢測上的需求,系統設計實現集交直流耐壓、絕緣電阻測試為一體的多通道絕緣耐壓一體式測試儀,能夠實現不低于3 kVAC/10 mA、4 kV/5 mA耐壓測試,通過通道掃描的方式對外提供16個絕緣耐壓測試通道[6]。

2.1硬件系統設計

硬件電路部分主要由高壓多通道掃描模塊、多通道驅動模塊、高壓電源模塊、STM32控制模塊、USB轉串口模塊(與上位機通信)、RS232通信模塊、故障存儲模塊等組成,其中RS232主要實現與高壓電源模塊的通信,故障存儲模塊采用EEPROM[7]。多通道耐壓絕緣測試系統主要硬件設計框圖如圖2所示。在電路設計時,要預留足夠的安全余量,實現高壓環境下隔離設計和相互干擾的控制。MCU采用的是STM32F103VET6,它具有80個GPIO口、兩個I2C、5個USART以及512 KB Flash、64 KB的RAM存儲資源。主要實現與上位機通信、通道控制、測試數據反饋、故障存儲等功能。

圖2 硬件結構框圖

下位機是上位機命令解析、數據處理、外圍模塊控制的中心。在下位機程序設計時,使用了uCOS實時操作系統,它具有實時多任務內核以及搶占式多任務的處理能力。下位機程序設計部分主要包含:上下位機交互通信、高壓測試條件配置、多通道掃描模塊的控制、以及故障存儲和故障查詢等。其中上下位機通信部分主要實現上位機命令解析和配置命令下發、配置命令包含測試條件命令和通道控制命令等。其測試原理主要是根據測試控制算法,上位機首先向STM32發送配置命令,MCU對配置命令進行解析,解析出的命令分別對高壓電源模塊和多通道掃描模塊進行配置,配置好后啟動測試;測試結束后,下位機將測試結果反饋給上位機,上位機收到測試結果后,系統停止測試,并將測試結果保存至數據庫,避免重復測試,方便用戶查詢。

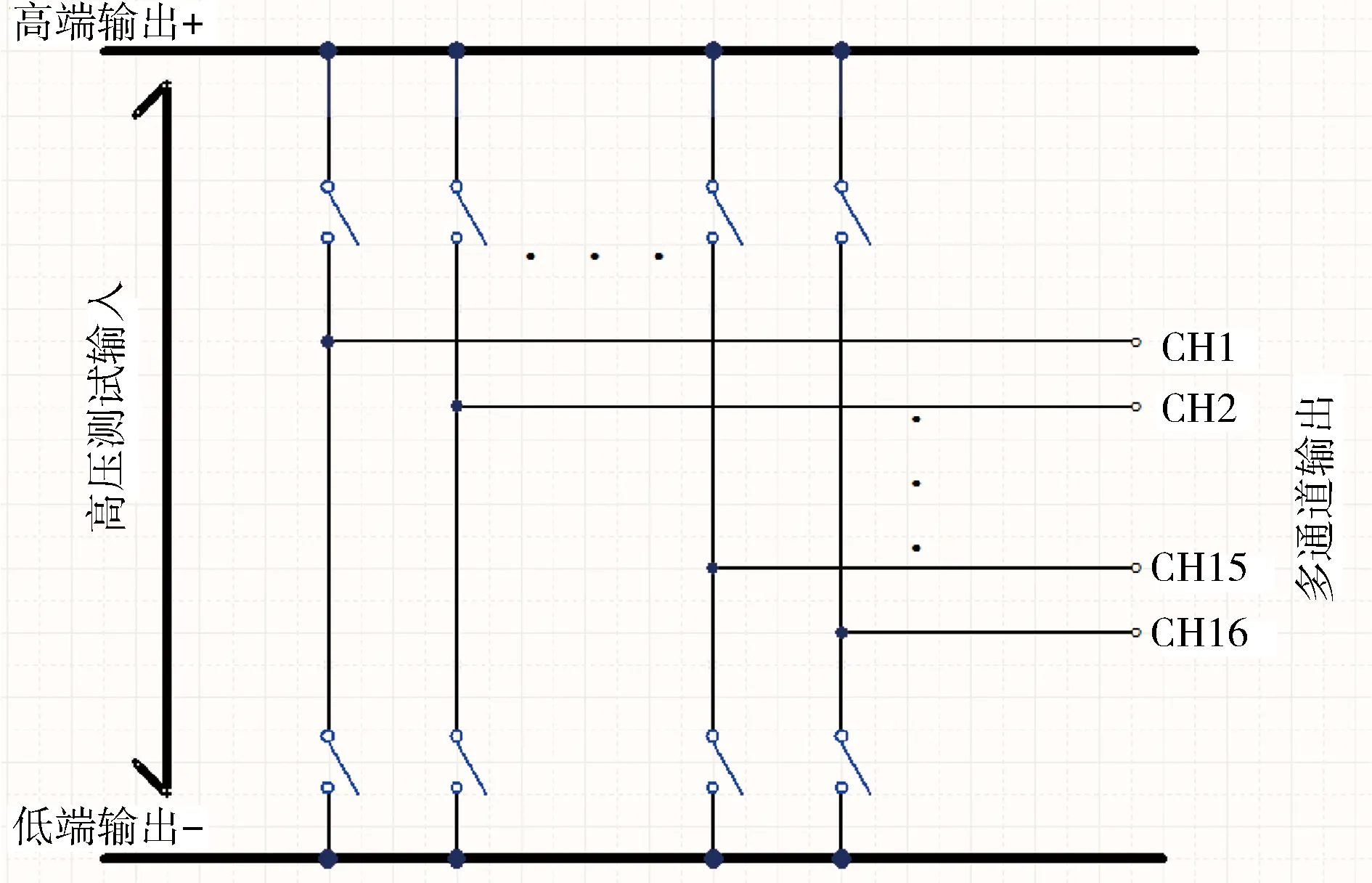

2.2高壓多通道掃描模塊設計

在電路設計時,滿足可靠性考慮,要采用必要的電氣隔離[8]。常用的電氣隔離方式有繼電器隔離、光電耦合器隔離、晶體管等隔離方式。在電路設計時,首先是高低壓的隔離,采用繼電器隔離法,用24 V繼電器對高壓通道進行控制;其次是STM32與24 V繼電器的電氣隔離,采用晶體管隔離法,在設計時使用ULN2803A,它是TI公司生產的高電壓、高電流達林頓管陣列,高壓輸出最高50 V,常用作繼電器等的驅動器。

在設計時,為了滿足耐壓絕緣測試要求,減少高壓多通道切換中繼電器的性能影響測試結果,在實際電路中使用的是高耐壓、高絕緣電阻的干簧管繼電器,其開關電壓7 500 VDC,最小負載電壓15 000 VDC,最大電流3 A, 絕緣電阻為1 010 Ω。其工作原理是將可磁化的簧片和惰性氣體密封在玻璃管中,當繞在干簧管上的線圈通電時,形成磁場使簧片磁化,簧片的觸點部分就會被磁力吸引,當引力大于簧片彈力時,常開接點吸合;當磁力減小到一定程度時,接點被簧片的彈力打開。多通道掃描模塊結構和原理如圖3所示,通常進行一步測試用到兩個通道,一個作為電壓高端通道、一個是電壓低端通道,測試時高端和低端與被測物之間形成測試回路。

圖3 多通道掃描模塊結構及原理圖

3 系統工作及測試

系統的上下位機交互的工作流程如下:首先是握手,上位機發送串口識別指令給下位機,下位機收到后反饋數據給上位機;接著上位機發送開機命令,下位機啟動開機自檢,對自身外圍模塊檢測,將自檢結果保存并且反饋給上位機;開機自檢過后,上位機開始發送測試條件命令,測試條件命令協議格式是“發送配置命令+通道”,對測試條件進行配置,配置完成后開始啟動測試。其他交互方式還有故障查詢和系統時間等,故障查詢時,上位機發送故障查詢指令,下位機將以往故障記錄反饋給上位機,故障格式是“故障時間+故障碼”。由于uCOS系統使用了RTC時鐘,在初次使用時要更新系統時鐘,以便發生故障時記錄故障的時間,當下位機接收到此指令,將系統時間更新。交互場景及流程如圖4所示[9]。

圖4 交互流程

該16通道耐壓絕緣測試系統下位機和硬件部分,通過與上位機界面整體聯調,能準確地完成上位機命令接收、解析和反饋、多通道的控制、故障存儲等,很好地完成了測試,測試結果滿足要求。系統測試的配置界面如圖5所示,測試結果如圖6所示。

圖5 測試配置界面

圖6 檢測結果

4 結束語

該多通道耐壓絕緣測試下位機和硬件電路部分,通過與上位機聯合調試,成功實現了測試條件的配置、多通道模塊的控制、測試數據的反饋、故障的存儲,通過實際測試能快速完成項目需求和性能要求。經過長期測試表明:該系統性能可靠、測試數據精確,同時能夠提高測試效率,具有較好的實用價值。

[1] 帥仁俊, 何慕容. 智能化耐壓絕緣測試設備的原理與實現[J] .南京建筑工程學院學報, 1997, 11(4): 50-54.

[2] 蔡祥,江冰. 基于485的耐壓絕緣測試系統設計[J]. 通訊技術,2011,44(3):32-34.

[3] 李琦,賀明,董利民,等.基于ARM嵌入式系統的SPI驅動程序設計[J].微型機與應用,2011,30(5):5-8.

[4] 陳娟,李元,李萬國.基于B/S模式的嵌入式系統測試方法與實現[J].電子技術應用,2016,43(2):50-52.

[5] 齊利芳, 劉虎, 賀占莊. 智能化絕緣/導通電阻測試系統的研制[J]. 微機發展, 2005, 11(15):78-82.

[6] 趙新民.智能儀器原理及設計[M].哈爾濱: 哈爾濱工業大學出版社, 1989.

[7] LABROSSE J J.嵌入式實時操作系統uC/OS-II[M].邵貝貝,等譯.北京:航空航天大學出版社,2010.

[8] 劉火良,楊森.STM32庫函數開發實戰指南[M].北京:機械工業出版社,2013.

Design of slave computer and hardware for multi-channel insulation withstand voltage test system

Xu Zhongyuan1, Zhou Hua1, Mu Jie2

(1. School of Big Data and Information Engineering, Guizhou University, Guiyang 550025, China; 2. Kaifeng Culture and Art Career Academy, Kaifeng 475000, China)

In order to meet the testing needs of the new multi-interface devices, for current voltage insulation tester has less common channel, and the degree of automation is not high, a multi-channel voltage insulation testing system is designed. The system mainly realizes reliable high-pressure multi-channel switching mode, the test data entry automation and efficient user interface. The practice results show that the system is simple, efficient and capable of analyst detection, rapid feedback and automated data entry. It improves test efficiency, and completes all the indexes and functions required by the system.

ulti-channel; voltage insulation testing; intelligence; slave computer

TP206.1

A

10.19358/j.issn.1674- 7720.2017.19.011

許中原,周驊,穆杰.多通道絕緣耐壓測試系統下位機及硬件設計[J].微型機與應用,2017,36(19):38-40.

貴州省科技廳聯合基金項目(黔科合LH字【2014】7630);貴州省功率元器件可靠性重點實驗室開發基金項目(KFJJ201502)

2017-04-06)

許中原(1988-),男,碩士研究生,主要研究方向:嵌入式系統、硬件設計。周驊(1978-),男,工學博士,副教授,主要研究方向:EDA,集成電路設計。穆杰(1975-),男,本科,副教授,主要研究方向:計算機軟件設計。