2.5 Gbit/s無電感高靈敏度寬動態范圍前置放大器設計

朱鐵柱,莫太山,葉甜春

?

2.5 Gbit/s無電感高靈敏度寬動態范圍前置放大器設計

朱鐵柱1, 2,莫太山1, 3,葉甜春1, 2

(1. 中國科學院微電子研究所,北京,100029;2. 杭州中科微電子有限公司,浙江杭州,310053;3. 嘉興禾潤電子科技有限公司,浙江嘉興,314001)

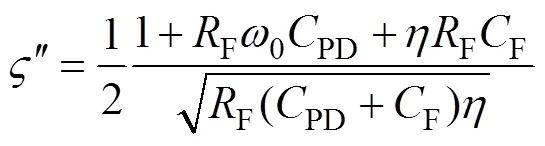

基于0.18 μm RF CMOS工藝設計一種應用于無源光網絡光接收機的無電感型2.5 Gbit/s前置放大器。該前置放大器主要包括跨阻放大器、單端轉差分運算放大器和輸出級電路。跨阻放大器基于3級推挽反相器結構,具有高增益和低噪聲的特點,提高前置放大器的靈敏度;分析零點補償原理,設計位于反饋環路之中的虛零點,提高跨阻放大器的工作速率,增加穩定性。提出一種新的具有自適應功能的自動增益控制技術,使得跨阻放大器在不同光輸入功率下保持帶寬不變,環路穩定,具有寬動態范圍特性。研究結果表明:在誤碼率為10?10,傳輸速率為2.5 Gbit/s時,該前置放大器的接收光靈敏度高達?29 dB·m,輸入最大光功率為2 dB·m,動態范圍達31 dB·m;在1.8 V的電源電壓下,芯片功耗為30 mW,芯片總面積為1×0.7 mm2。

光接收機;前置放大器;靈敏度

隨著多媒體技術的發展和應用,高速率的數據傳輸要求通信系統的帶寬越來越高,成本越來越低。光通信技術由于其具有低成本和高信道容量特性成為高速數據傳輸的首選方案。光接收機主要包括前置放大器(preamplifier)、限幅放大器(limiting amplifier,LA)和時鐘恢復電路(clock and data recovery,CDR)等。光電二極管(photodiode,PD)監測光信號強度并將其轉換為電流。前置放大器將電流信號轉換為電壓信號,并由限幅放大器放大電壓信號至足夠大,再輸入時鐘恢復電路。前置放大器的帶寬和靈敏度等關鍵參數[1]決定了最大數據傳輸速率和信道損耗,因此,通常也決定了光通信系統的性能。近年來,人們研究了多種前置放大器電路,這些研究主要集中在2個方面:1) 提高前置放大器的帶寬,例如電感峰化技術[2?4]、電容弱化技術[5?6]以及調節型共源共柵電路結構[7?9]等。電感峰化技術芯片面積大,并且會引起串擾。電容補償技術會降低電壓放大器的增益。調節型共源共柵結構雖然隔離了光電二極管的寄生電容,增大了電路的帶寬,但其噪聲性能比電壓反饋型跨阻放大器的性能差。 2) 提高前置放大器的靈敏度和動態范圍,例如噪聲消除技術[10]和自動增益控制電路[11?12]。噪聲消除技術增加了電路結構的復雜性。自動增益控制電路的設計則沒有考慮輸入光功率增大時前置放大器環路的穩定性變化。CMOS工藝具有成本低、功耗低的優點,本文作者基于CMOS工藝設計一種無電感的高靈敏度寬動態范圍前置放大器。傳統的3級推挽反相器構成的跨阻放大器具有噪聲性能好的特性[13],但由于其內部包含3個極點,僅限于千兆及以下跨阻放大器電路[14]。針對此缺點,本文作者設計位于反饋環路中的虛零點,加強了環路的穩定性,將其工作速率提高至2.5 Gbit/s;提出一種新的具有自適應功能的自動增益控制技術,以增大前置放大器的輸入動態范圍,保持前置放大器在不同輸入功率條件下環路的穩定性。

1 前置放大器結構設計

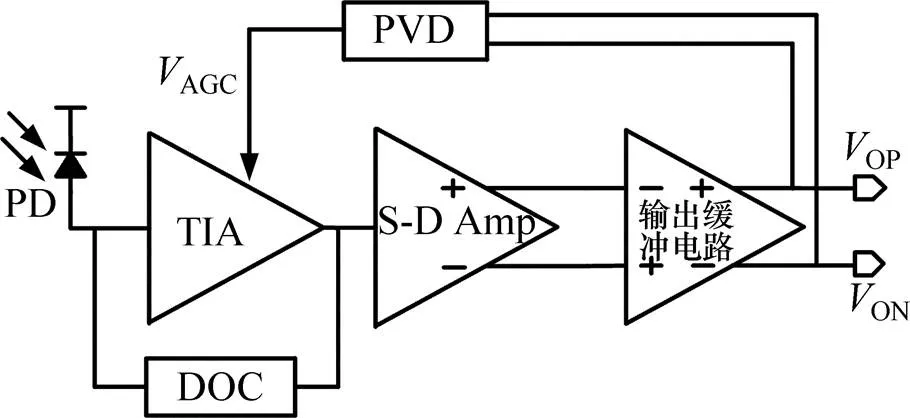

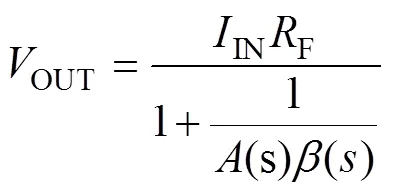

前置放大器芯片結構框圖如圖1所示,主要包括跨阻放大器(TIA)、單端轉差分放大器(single-ended to differential-ended amplifier,S?D amp) 、輸出緩沖電路 (driver)、峰值檢測電路(peak?value detection,PVD)和直流消失調電路(DC offset cancellation,DOC)等。PD將不同功率的光信號轉換為相應電流,跨阻放大器將電流信號轉換為電壓信號,并通過單端轉差分放大器將其轉換為差分信號。最后一級為輸出緩沖電路,輸出電阻為50 Ω。PVD檢測前置放大器輸出端口電壓OP和ON,產生自動增益控制電壓AGC。DOC保持前置放大器輸入級的直流工作點穩定,輸入輸出電壓相等。

圖1 前置放大器結構框圖

2 前置放大器電路設計

2.1 高靈敏度跨阻放大器設計

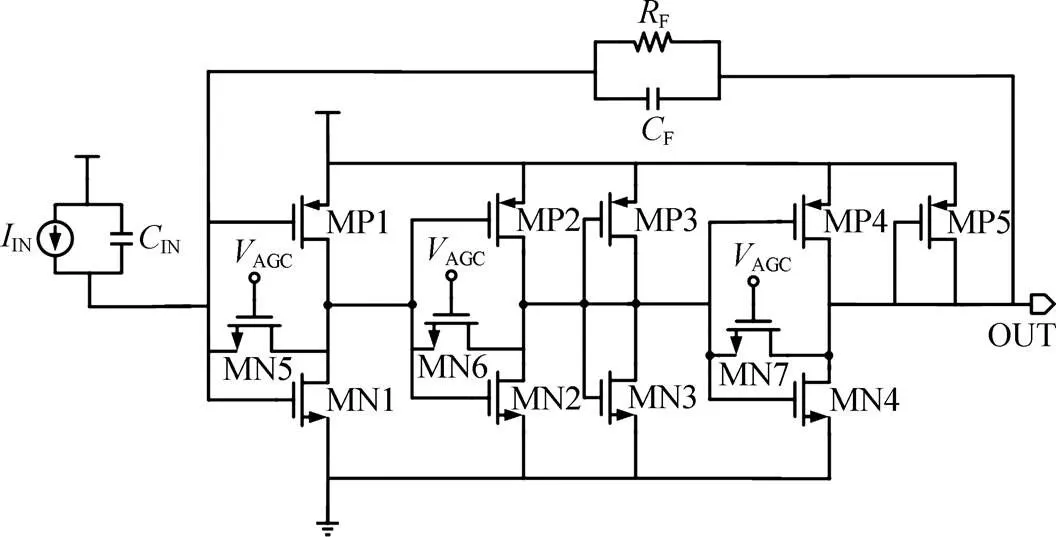

跨阻放大器電路如圖2所示。光電二極管原型復雜,簡化為寄生電容與理想電流源的并聯。圖2中,IN為流過光電二極管的電流,CIN包含光電二極管的寄生電容、TIA(transimpedance amplifier)輸入管腳Bonding寄生電容、輸入晶體管寄生電容等,它限制了電路的最大帶寬。晶體管MN1,MN2,MN4,MP1,MP2和MP4構成3級推挽反相器,電阻F與電容F構成反饋電路。3級推挽反相器和反饋電路組成跨阻放大器,輸出端口為OUT。第2級和第3級反相器輸出節點增加了二極管連接方式連接的晶體管MN3,MP3和MP5,降低了節點阻抗,減小了密勒效應。晶體管MN5,MN6和MN7組成具有自適應功能的自動增益控制電路,提高了電路的輸入動態范圍。

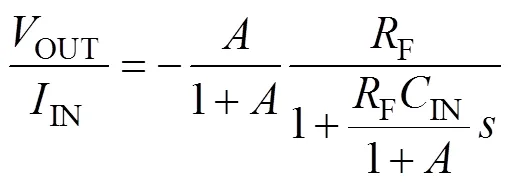

不考慮補償電容F的影響,在跨阻放大器電路輸入端處,由基爾霍夫定律得:

圖2 跨阻放大器電路

式中:OUT為跨阻放大器輸出小信號電壓;IN為PD注入電流;為3級推挽反相器的直流增益;F為跨阻;IN為輸入節點寄生電容;為函數的自變量。式(1)表明:當>>1時,TIA的中頻跨阻增益近似等于跨阻F。

式中:?3 dB為跨阻放大器的?3 dB帶寬。在給定傳輸速率下,要求跨阻放大器?3 dB帶寬最優值約為給定傳輸速率的0.7倍[15](對于2.5 Gbit/s,最佳設計?3 dB帶寬約1.8 GHz)。由式(2)可知:對于給定的?3 dB帶寬,跨阻RF的電阻決定了3級推挽反相器的直流增益設計指標。為了最小化主通道上寄生電容,提高跨阻放大器的速率,TIA電路主通道上所有晶體管采用最小柵長晶體管。負反饋環路通過跨阻RF提供直流偏置電壓,因為沒有電流輸入,RF兩端的電壓差幾乎為0 V,所以,TIA 的輸入輸出直流電壓相等,為設計TIA 電路增加了1個重要的約束條件。經優化后的電路,第1級推挽反相器的溝道寬度最大,第2級與第3級反相器溝道寬度較小,且兩者相等。

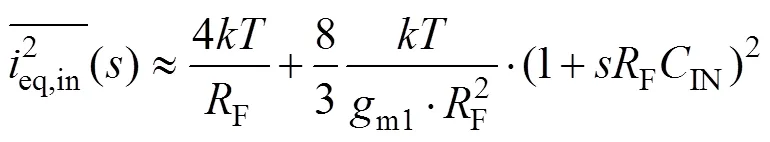

對于1個合理的跨阻放大器設計,跨阻放大器的主要噪聲是跨阻RF噪聲和放大器噪聲。由于3級推挽反相器具有高增益的特性,因此,放大器噪聲主要取決于第1級輸入晶體管的噪聲。晶體管的閃爍噪聲僅僅在低頻時起主要作用,因此,可以忽略不計,可得

式中:為等效輸入參考電流噪聲密度;k為玻爾茲曼常數;T為溫度;gm1為輸入級等效跨導。由式(3)可知:輸入跨導gm1越大,反饋電阻RF越大,跨阻放大器的等效輸入噪聲電流越小。3級推挽反相器結構簡單,不需要額外的偏置電路,對于給定電流,能提供最大跨導,等效跨導為PMOS和NMOS管跨導的總和。而且對于增益帶寬積大于500 MHz的工藝,采用3級等效推挽反相器級聯的跨阻放大器等效輸入噪聲電流最小[16],從而具有最優的噪聲性能。增大跨阻RF也可以減小跨阻放大器的等效輸入噪聲電流,但根據式(2),在保持跨阻放大器帶寬不變的前提下,增大跨阻RF需要增加3級推挽反相器的增益A。3級推挽反相器增益A增加引起主極點下降,從而降低環路的穩定性。因此,噪聲性能與放大器的負反饋環路穩定性應進行嚴格折中。優化后的跨阻放大器等效噪聲電流密度仿真結果如圖3所示。在跨阻放大器的?3 dB帶寬范圍內,跨阻放大器最小輸入噪聲電流密度僅為2.2 pA/Hz1/2,平均等效輸入噪聲電流密度僅為5.4 pA/Hz1/2。

2.2 帶寬與穩定性分析

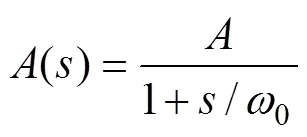

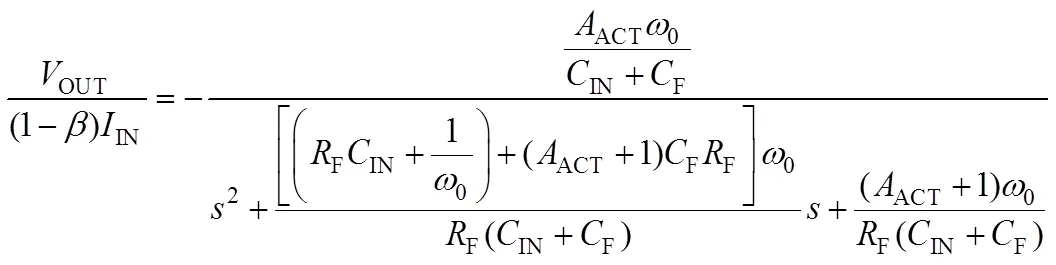

由于3級推挽反相器內部包含3個極點,限制了帶寬的提高。二極管連接方式的晶體管MN3,MP3和MP5降低了該節點的輸出阻抗,提高了3級推挽反相器的第2級和第3級輸出節點的極點頻率,使其遠遠大于第1級輸出節點的極點頻率和環路?3 dB帶寬頻率。3級推挽反相器第1級輸出節點成為主極點,設其拉普拉斯傳輸函數為

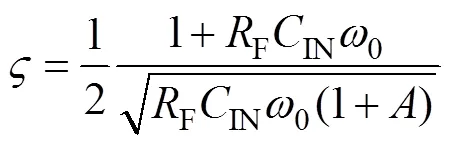

式中:0為放大器的主極點。當放大器輸入小信號電流時,晶體管MN5,MN6和MN7關閉。不考慮補償電容F的影響,跨阻放大器反饋系數為

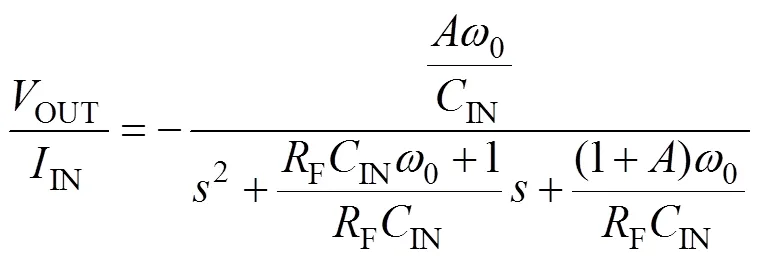

將式(4)和(5)代入式(6)得

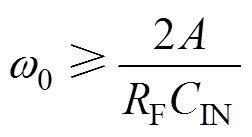

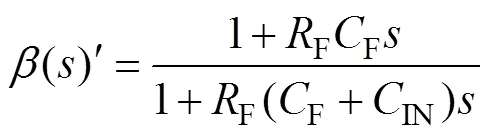

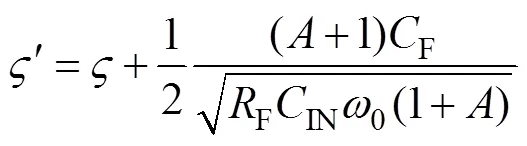

3級推挽反相器主極點0必須大于2/(FIN),跨阻放大器反饋環路才能穩定。由式(2)可知0限制了TIA工作速率的提高。本文提出一種新的補償方案,不使用電感,在保持跨阻放大器穩定性的前提下,能夠最大限度地提高跨阻放大器的工作速率。補償電容F與反饋電阻F并聯,不存在于系統傳輸函數中,僅存在于反饋網絡中。考慮構成虛零點的補償電容F影響,據式(5),有

補償電容F構成了位于反饋系數中的零點,稱為虛零點。顯然,虛零點減小了反饋系數的相位偏移。將式(10)代入式(6),可得

考慮到F<<IN,可得

1—零點補償;2—無零點補償。

圖4 跨阻放大器的頻率響應

Fig. 4 Frequency response of TIA

2.3 自動控制增益設計

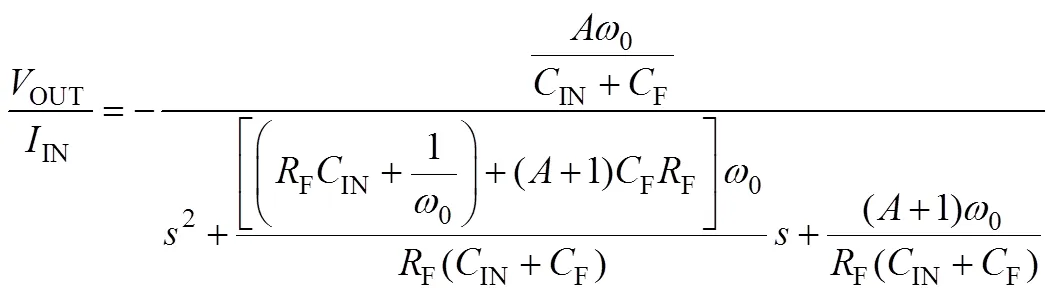

如圖1所示,自動增益控制電壓AGC由PVD根據信號強度產生,依據AGC可以將輸入光電流信號分為“非激活”區域、“激活”區域。在“非激活”區域,光電流信號小,AGC保持在最小值,MN5,MN6和MN7處于截止狀態,跨阻放大器保持線性工作,輸出電壓幅度與輸入電流信號呈線性關系。而在“激活”區域,輸入電流較大,為了避免跨阻放大器進入飽和狀態,自動增益控制被激活,AGC變大,MN5,MN6和MN7進入線性區,等效為隨AGC增大而變小的可變電阻,實現了大信號時的自動增益控制,保證在“激活”區域,跨阻放大器仍然保持線性工作。在“激活”區域,MN5,MN6和MN7開啟,此時,IN并非全部流過跨阻F,其中有一部分交流電流1流過MN5,且AGC越大,則1所占的比例越大。同時,MN5,MN6和MN7也降低了3級推挽反相器總增益。當輸入的光功率增加時,式(11)變為

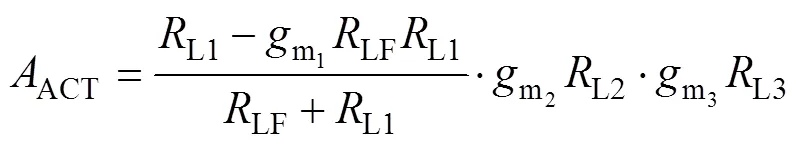

式中:為由反饋電壓AGC決定的常數,0≤≤1;ACT為3級推挽反相器在“激活”區域的電壓增益。由式(13)可見,等效跨阻變為原來的(1?)倍。不考慮晶體管MN6和MN7的影響,3級推挽反相器構成的增益為

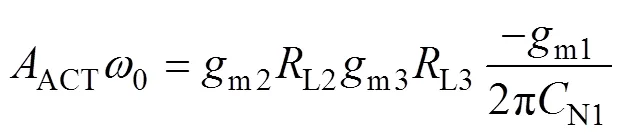

式中:m1,m2和m3分別為第1級、第2級和第3級反相器的等效跨導;L1,L2和L3分別為第1級、第2級和第3級反相器的輸出節點電阻;LF為MN5等效線性區電阻,阻值受控制電壓AGC控制。放大器的主極點在第一級輸出節點,大小為

式中:N1為第1級反相器輸出節點的等效電容。

即為1個常數,設其為常數,則有

反饋控制電壓AGC/V:1—0.9;2—1.2;3—1.5。

圖5 跨阻放大器在不同自動增益控制電壓下的頻率響應

Fig. 5 Frequency response of TIA at different auto-gain control voltages

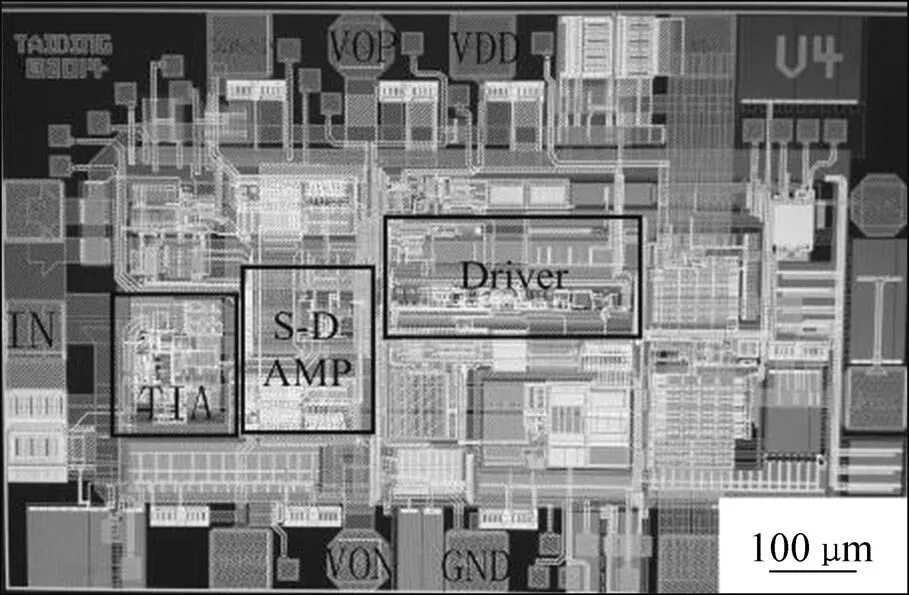

3 測試結果

前置放大器采用0.18 μm RF CMOS 工藝設計并流片。芯片版圖如圖6所示,面積為1×0.7 mm2。前置放大器測試時將與光電二極管封裝在一起,通過接收光信號完成測試。光電二極管寄生電容為0.65 pF,轉換效率為0.9 A/W。

圖6 前置放大器版圖

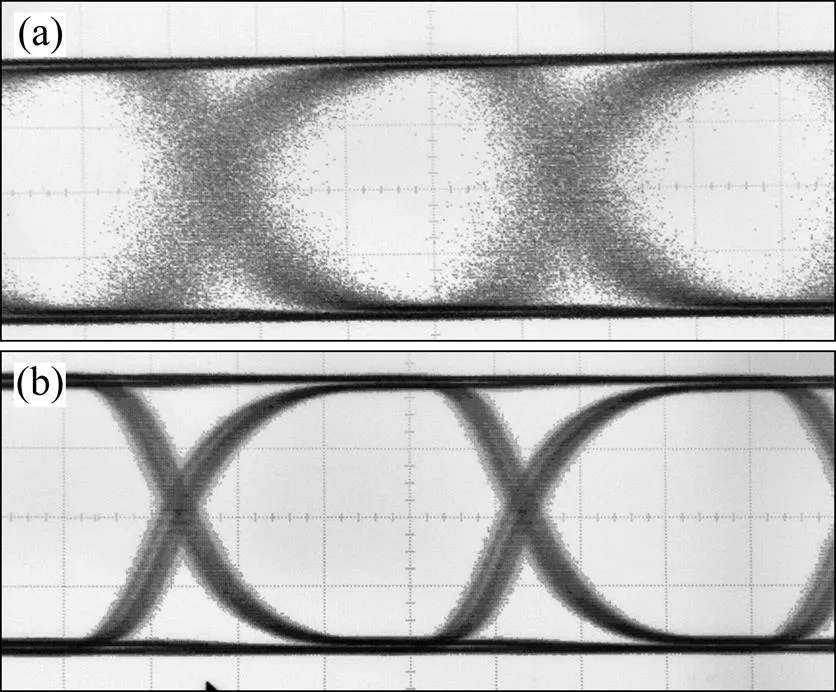

前置放大器的眼圖測試通過Advanstest D3186函數信號發生器和Agilent DCA 86100A眼圖儀完成測試。函數信號發生器產生速率為2.5 Gbit/s、周期為210?1的偽隨機二進制碼(PRBS),并通過光模塊發射消光比為12 dB的輸出激光信號,激光信號經過光衰減器后作為前置放大器的輸入。圖7所示為前置放大器在?29 dB·m和2 dB·m輸入光功率下的輸出眼圖,眼圖清晰,輸出電壓擺幅為380 mV。

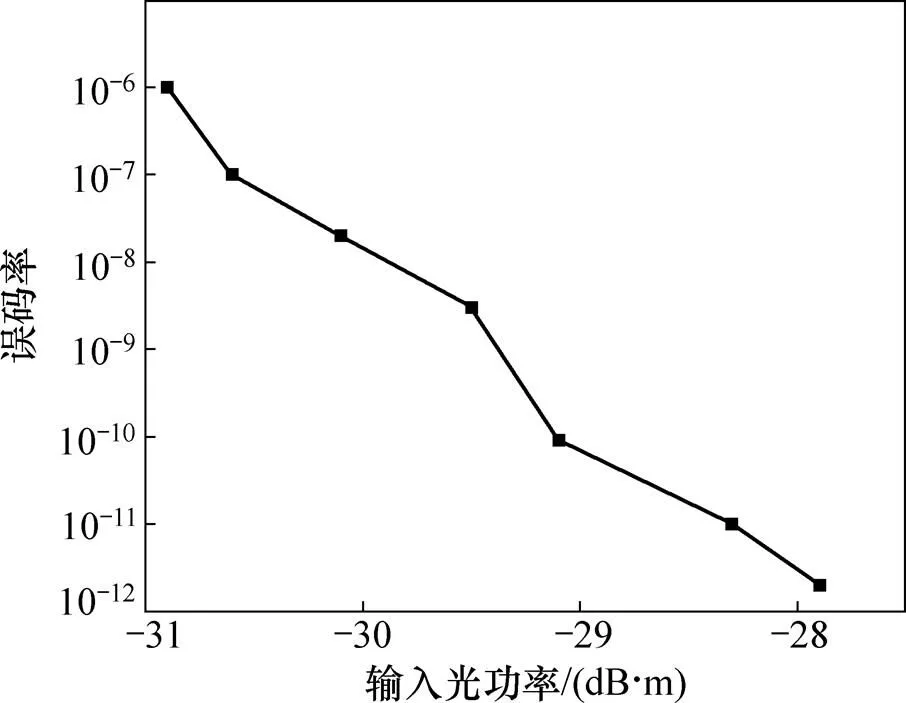

前置放大器靈敏度測試采用Antrisu的MP1763C和MP1764C 比特誤差率測試系統。在前置放大器的輸入端輸入消光比為12 dB、速率為2.5 Gbit/s、周期為210?1偽隨機碼流測試結果如圖8所示。對于常用的數字通信系統,比特誤差率一般要求為10?10。前置放大器在此比特誤差率的要求下光靈敏度為 ?29 dB·m。

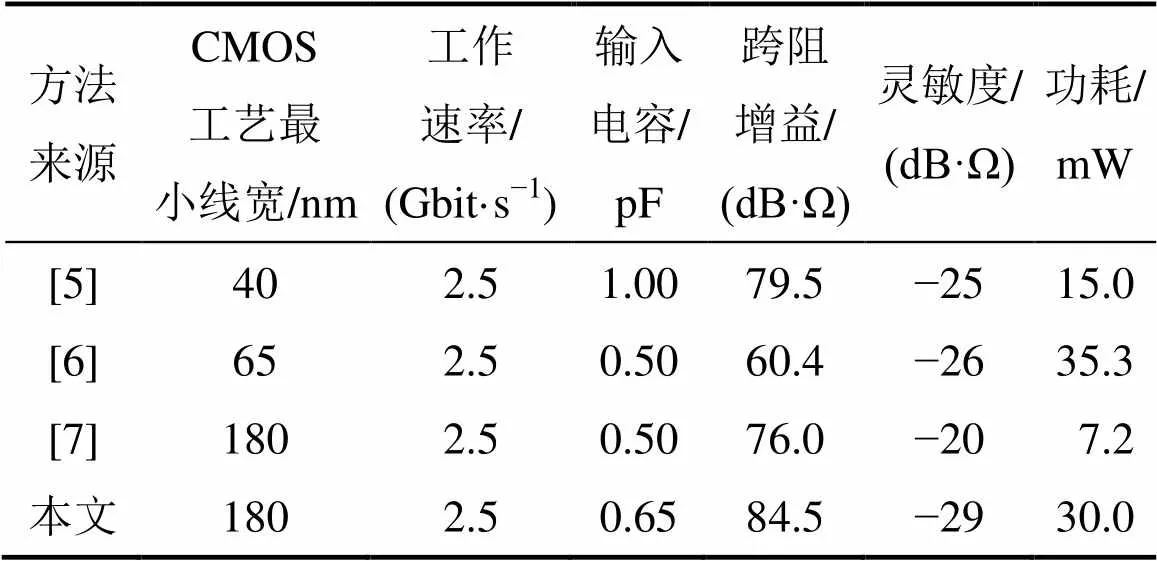

該前置放大器的性能見表1。從表1可見:經過本文的優化設計,前置放大器在保持帶寬的前提下,有效改善了噪聲性能。通過改善噪聲性能,在實際測試結果中,前置放大器的靈敏度為?29 dB·m。

輸入光功率/(dB?m):(a) ?29;(b) 2

圖8 不同光輸入功率下的比特誤碼率

表1 前置放大器性能比較

4 結論

1) 基于0.18 μm RF CMOS 工藝設計了一種應用于光接收機的無電感前置放大器。

2) 采用零點補償技術,將3級推挽方向器結構的跨阻放大器工作速率提高至2.5 Gbit/s。提出一種具有自適應功能的自動增益控制電路,使前置放大器在不同輸入光功率條件下環路保持穩定。

3) 在傳輸速率為2.5 Gbit/s、誤碼率為10?10時,前置放大器的光靈敏度達?29 dB·m,輸入范圍達 31 dB·m。該前置放大器可應用于光接收機之中。

[1] 朱恩, 王志功, 馮軍, 等. 2.5~40 Gb/s光收發關鍵器件芯片技術[J]. 中國有色金屬學報, 2004, 14(S1): 369?380. ZHU En, WANG Zhigong, FENG Jun, et al. Transceiver integrated circuit technology for 2.5?40 Gb/s optical-fiber communication[J]. Transactions of Nonferrous Metals Society of China, 2004, 14(S1): 369?380.

[2] JIN Junde, HSU S S H. A 40 Gb/s transimpedance amplifier in 0.18 μm CMOS technology[J]. IEEE Journal of Solid-State Circuits, 2008, 43(6): 1449?1457.

[3] WALLING J S, SHEKHAR S, ALLSTOT D J. Wideband CMOS amplifier design: time-domain considerations[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2008, 55(7): 1781?1793.

[4] LU Zhenghao, YEO K S, MA Jianguo, et al. Broad-band design techniques for transimpedance amplifiers[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2007, 54(3): 590?600.

[5] CHIEN F T, CHAN Y J. Bandwidth enhancement of transimpedance amplifier by a capacitive-peaking design[J]. IEEE Journal of Solid-State Circuits, 1999, 34(8): 1167?1170.

[6] HUANG Beiju, ZHANG Xu, CHEN Hongda. 1 Gb/s zero-pole cancellation CMOS transimpedance amplifier for Gigabit Ethernet applications[J]. Journal of Semiconductors, 2009, 30(10): 105005.

[7] KIM Y H, JUNG E S, LEE S S. Bandwidth enhancement technique for CMOS RGC transimpedance amplifier[J]. Electronics Letters, 2014, 50(12): 882?884.

[8] CHEN Yingmei, WANG Zhigong, FAN Xiangning, et al. A 38 Gb/s to 43 Gb/s monolithic optical receiver in 65 nm CMOS technology[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2013, 60(12): 3173?3181.

[9] XU Hui, FENG Jun, LI Quan, et al. A 3.125 Gb/s inductorless transimpedance amplifier for optical communication in 0.35 μm CMOS[J]. Journal of Semiconductors, 2011, 32(10): 105003.

[10] ATEF M, ZIMMERMANN H. 2.5 Gbit/s transimpedance amplifier using noise cancelling for optical receivers[C]//2012 IEEE International Symposium on Circuits and Systems. Seoul: IEEE, 2012: 1740?1743.

[11] LIU Lianxi, ZHAO Jiao, EN Yunfei, et al. A high gain wide dynamic range transimpedance amplifier for optical receivers[J]. Journal of Semiconductors, 2014, 35(1): 015001.

[12] TAGHAVI M H, BELOSTOTSKI L, HASLETT J W. A CMOS low-power cross-coupled immittance-converter transimpedance amplifier[J]. IEEE Microwave & Wireless Components Letters, 2015, 25(6): 403?405.

[13] del POZO J M G, CELMA S, SANZ M T, et al. CMOS tunable TIA for 1.25 Gbit/s optical gigabit ethernet[J]. Electronics Letters, 2007, 43(23): 1303?1305.

[14] SACKINGER E. Broadband circuits for optical fiber communication[M]. New York: John Wiley & Sons, 2005: 1?50.

[15] PIETRUSZYNSKI D M, STEININGER J M, SWANSON E J. A 50 Mbit/s CMOS monolithic optical receiver[J]. IEEE Journal of Solid-State Circuits, 1988, 23(6): 1426?1433.

[16] JUNG H Y, LEE J M, CHOI W Y. A high-speed CMOS integrated optical receiver with an under-damped TIA[J]. IEEE Photonics Technology Letters, 2015, 27(13): 1367?1370.

(編輯 陳燦華)

2.5 Gbit/s inductorless preamplifier with high sensitivity and wide dynamic range

ZHU Tiezhu1, 2, MO Taishan1, 3, YE Tianchun1, 2

(1. Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China;2. Hangzhou Zhongke Microelectronics Co. Ltd., Hangzhou 310053, China;3. Jiaxing Heroic Technology Co. Ltd., Jiaxing 314001, China)

An inductorless 2.5 Gbit/s preamplifier was designed for the application of optical receivers in passive optical network and fabricated in a 0.18 μm RF CMOS process. The preamplifer consisted of a transimpedance amplifier, a single-ended Ti differential ended amplifier and an output driver. The transimpedance amplifier was based on a three-stage push-pull inverter structure. The special configuration allows for high gain and low noise performance. Phantom zeros technique was analyzed and employed to improve the bandwidth and ensure the stability of the TIA. To achieve a wide dynamic range, an automatic gain control technique with self-adaptive function was proposed to keep the bandwidth constant and stabilize the feedback network. The results show that the optical sensitivity is ?29 dB·m and the maximum input optical power is 2 dB·m for 2.5 Gbit/s operation with a bit error rate of 10?10. The dynamic range is 31 dB·m.The chip consumes about 30 mW from a single 1.8 V supply. The chip area is 1×0.7 mm2.

optical receiver; preamplifier; sensitivity

10.11817/j.issn.1672?7207.2017.08.014

TN433

A

1672?7207(2017)08?2073?06

2016?08?08;

2016?10?12

國家科技重大專項(2013ZX02310);中國第二代衛星導航系統重大專項(GFZX030302020205)(Project(2013ZX02310) supported by the Major Project of National Science and Technology; Project(GFZX030302020205) supported by the Major Project of the Second Generation Satellite Navigation System of China)

朱鐵柱,博士研究生,從事數模混合集成電路研究與設計;E-mail:jinmulu@163.com