SoC芯片FPGA原型的軟硬件協同驗證

(重慶郵電大學 通信與信息工程學院,重慶 400065)

SoC芯片FPGA原型的軟硬件協同驗證

程翼勝

(重慶郵電大學 通信與信息工程學院,重慶 400065)

在IC設計中,驗證占據著舉足輕重的地位。為了達到高效率、高可靠性的驗證結果,保證芯片在流片的成功率,引入了FPGA原型驗證技術。本文以一款低功耗報警器SoC為對象,首先簡單介紹了低功耗報警器SoC芯片的系統架構,然后詳細說明了報警器SoC芯片FPGA原型驗證的具體實現。利用軟硬件協同驗證方法,驗證了報警器SoC芯片模塊的功能以及系統驗證。

SoC;FPGA;原型驗證

引 言

圖1 報警器芯片系統架構

芯片驗證的時間占據了整個研發周期的三分之二,驗證的充分性有效地保證了芯片投片的成功率。為了獲得高效可靠的驗證結果,本文引入了FPGA原型驗證。用FPGA作為硬件模塊的承載體,一方面可以使芯片設計在真實的硬件上運行,及時發現設計中的缺陷;另一方面基于FPGA的原型驗證平臺驗證速度快,彌補了軟件仿真慢的不足。

本文論述了一個基于ARM Cortex-M0處理器的報警器芯片架構,以及FPGA原型驗證平臺的實現過程,包括FPGA驗證板的介紹、RTL設計到FPGA代碼轉換、硬件下載流程、軟硬件協同調試的方法等。

1 報警器芯片架構

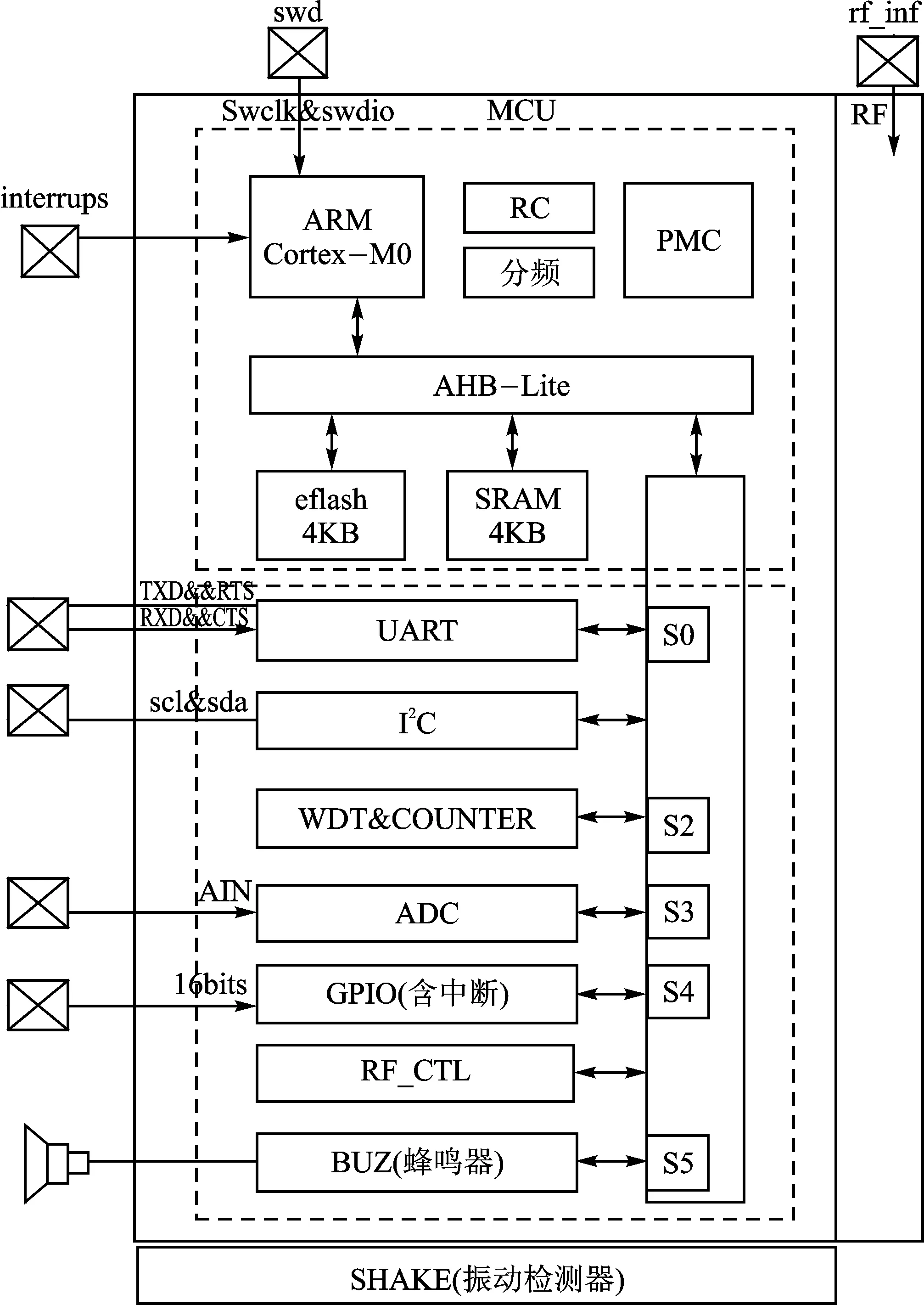

該系統應用于工業控制領域,具體應用為無線遙控、無線報警器。其將射頻和ARM集成到一塊芯片中,其中基帶部分和射頻部分通過兩根GPIO線實現連接,進行控制和數據交互。系統架構如圖1所示。

該芯片作為電動車報警器的接收部分,采用ARM Cortex-M0內核的MCU作為主控處理器,掛接在AHB總線上,使用AHB轉APB總線作為數據通路,連接多個外部接口控制器(UART、I2C、ADC等),芯片內部接有時鐘管理單元,其系統框圖如圖2所示。硬件模塊的描述如表1所列。

圖2 數字部分整體框架

在正常工作模式下,處理器可以定時伺服看門狗,也可以屏蔽掉看門狗的復位功能,處理器配置完畢后可以配置系統控制寄存器,使得系統進入sleep模式,此時外設保持工作狀態,任何外設的中斷信號都會導致處理器恢復到active模式下響應中斷,完成中斷服務程序后重新進入sleep模式。

表1 硬件模塊描述

2 報警器硬件平臺的設計

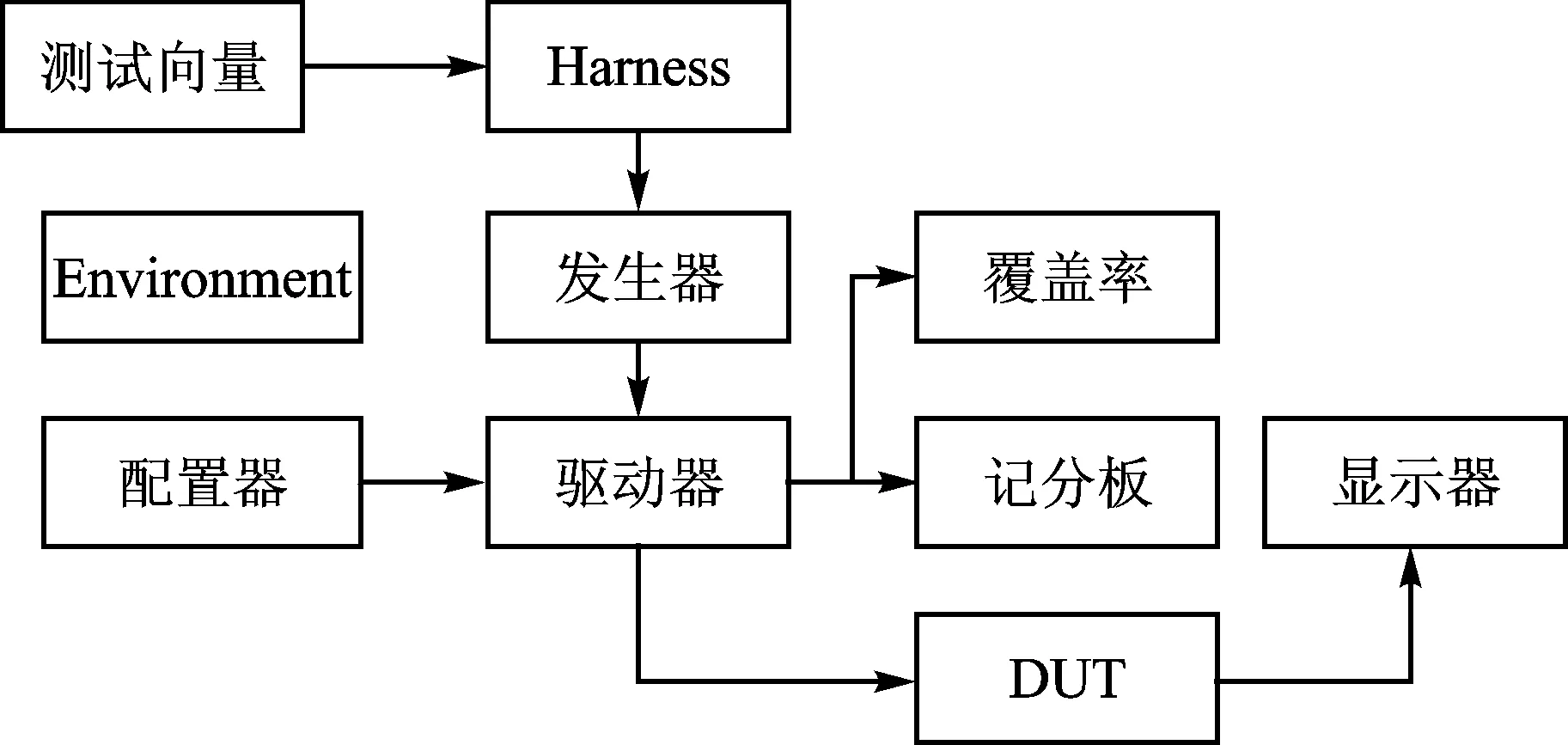

報警器芯片的驗證,主要是對芯片的模塊到系統功能的驗證,報警器具體驗證平臺的總體架構如圖3所示。

圖3 報警器驗證平臺結構

圖4 驗證環境

整個FPGA驗證工作可以劃分為三個部分:PC機上調試,FPGA驗證板上工作和軟硬件協同調試。其中PC機主要工作是產生配置文件、測試激勵收發數據的讀取以及結果的驗證。FPGA驗證板主要是設計芯片工作的載體,并把芯片實時狀態信息回傳給PC機。驗證環境如圖4所示。

PC機運用Quartus生成bit流文件,下載到FPGA驗證板中,通過Keil編寫調試軟件對FPGA芯片進行控制和調試。對于驗證板需要提供設計芯片的上電復位和測試時鐘,接收PC機發送的調試程序和調試數據,并運行程序調試,且將芯片運行的狀態信息回傳給PC機。

在調試部分,由于報警器芯片的內部結構復雜,僅憑借芯片引腳上的輸入/輸出信號很難判斷設計是否符合實際需求。因此,必須選擇合適的方法對FPGA芯片內部狀態進行調試,從而獲知芯片的狀態是否工作正常,若不正常還能定位到問題之所在。采用邏輯分析儀SignalTap II觀測內部信號,并通過串口調試助手來反饋信號的變化。

3 FPGA硬件平臺的介紹

表2 EP4SE820F1760

本文采用的FPGA驗證平臺為Hyper Silicon, 硬件平臺搭建主要運用了EP4SE820 FPGA器件,具有完善的時鐘和存儲資源,支持更快的速度。FPGA芯片擁有的主要可編程資源如表2所列。

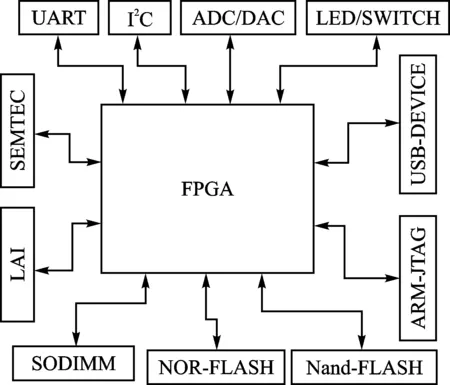

Hyper Silicon驗證平臺的所有外設在驗證前均要通過連通性和功能性測試,以保證板上各元件能夠穩定工作,為后續驗證中的問題定位打好基礎。其基本框架如圖5所示。

圖5 Hyper Silicon驗證平臺基本框架

4 FPGA軟件環境搭建

ASIC與FPGA兩者物理結構不同,ASIC采用的是生產廠商提供的標準單元庫,FPGA是基于查找表結構,因此造成了RTL代碼風格的不同,所以在采用FPGA原型驗證技術驗證ASIC設計時,必須先把ASIC設計代碼轉換為FPGA設計代碼,才能移植到FPGA上。但需要注意的是,這僅僅是物理結構上的差異,而對代碼進行轉換,并不改變設計邏輯功能。需要修改的部分包括以下幾個方面:

(1)存儲單元

ASIC中的存儲單元是用代工廠提供的Memory Compiler 來定制,只適合做ASIC功能仿真,FPGA是不能綜合的,而FPGA內部提供的存儲單元是經過驗證和優化的,因此存儲單元需要轉化為FPGA中的存儲單元。[1]

(2)時鐘單元

在ASIC設計中,時鐘是整個設計電路中最重要的信號,在ASIC中,用布局布線工具來放置時鐘樹,利用代工廠提供的PLL進行時鐘的設計生成,而在FPGA中通常內置有一定數量的PLL宏單元,并有經過時鐘優化了的全局時鐘,可以保證同源時鐘沿到達每個寄存器的延時時間差異可以忽略不計。[2]因此,時鐘單元要進行替換。替換方法如下:

`ifdef AUTO_FPGA

Pll_osc u_pll_osc (

.inclk0 (clk_32M),

.c0 (osc_clk) );

assign por_reset_n=hw_rstn_i;

`else

OSCRC020MCB osc_insn(

.FOUT (osc_clk ),

.RESET (~por_reset_n ),

.PD (~por_reset_n ),

ISEL (osc_trim) );

`endif

另外,特別需要注意的是門控時鐘,ASIC設計中為了實現低功耗,采用了門控使能時鐘設計。FPGA全局時鐘資源有限,經過門控延時較大,會產生毛刺現象,因此,需要把門控時鐘電路轉換為時鐘使能電路。替換方法如下:

`ifdef AUTO_ASIC

AND_X4_A7TR u_clk_gate(.Y(clk_out), .(clk_in), .B(clk_en));

`elseif AUTO_FPGA

assign clk_out=clk_en & clk_in;

`endif

(3)頂層PAD的替換

在ASIC的設計中,頂層模塊包含了一層PAD層,I/O引腳需要通過PAD與外部引腳相連,而PAD也是工藝庫提供的模塊單元,對FPGA實現來說,顯然實現不了PAD的功能,同樣也不需要這個模塊單元,所以在FPGA模式下代碼的頂層就不用包含PAD層的代碼。

5 軟硬件協同驗證系統

基于軟硬件協同仿真驗證是FPGA驗證SoC的常規方法,并搭建軟硬件協同驗證平臺環境,實現能夠滿足實際需求的FPGA驗證平臺。[3]

5.1 FPGA軟硬件協同驗證架構

FPGA驗證是為了驗證SoC設計芯片在實際物理硬件環境中功能和運行狀態是否正常。針對本文提出的基于報警器SoC芯片搭建能夠實現驗證的軟硬協同驗證系統的基本架構如圖6所示。

圖6 軟硬件協同驗證系統基本架構

其中包括FPGA驗證板、支持下載bit文件以及調試驗證過程中需要的FPGA下載線及編程器、支持芯片的仿真器,以及安裝有Keil軟件、Quartus軟件和串口調試助手軟件的PC機。軟硬件協同驗證的步驟如下:

① 先把需要驗證的SoC系統由Quartus工具綜合及布局布線生成對應的bit流文件,經過JTAG下載到FPGA驗證板中。

② 通過上位機Keil軟件編寫控制報警器芯片運行的軟件程序,完成系統的boot、初始化、測試激勵編譯及控制所需要的程序。

③ 通過編寫及測試激勵程序的加載、運行、調試,實現對設計芯片的狀態控制,觀察芯片運行的狀態信息是否正常。

④ 通過不同的測試程序控制運行相應的模塊以及整個系統的運行工作,保證驗證的完整性。

在驗證的過程中,根據各個模塊的功能以及SoC系統特性,使用示波器觀測相應的信號引腳,利用SignalTal軟件抓取內部信號來判斷邏輯功能關系,驗證系統各模塊交互、數據相互流通功能的正確性;驗證所有IP核協同運行狀態;驗證整個系統功能的正確性。驗證流程圖7所示。

圖7 驗證流程圖

5.2 SoC系統及各模塊功能驗證

首先對SoC系統功能驗證,前提是要保證FPGA軟件平臺以及硬件平臺的正確性,才能在Keil環境下編寫控制軟件程序,以達到驗證各個模塊功能正確的目的。Keil編程器與FPGA硬件平臺連線正確后,可以通過下載編寫控制軟件程序驗證各個模塊功能的正確性。

5.2.1 射頻模塊的功能驗證

射頻模塊接收發射機發出的射頻信號,經過ASK/OOK的解調輸出0~VDD的模擬信號。 由于在實際系統中使用基于OOK的曼徹斯特編碼方式(20位地址+4位命令),因此輸出的模擬信號實際為0或1的邏輯電平。MCU通過GPIO輸入端接收這個電平并且通過判決程序進行曼徹斯特編碼的判決,若正確接收命令,然后發送中斷,此時喚醒ARM來處理射頻數據,否則進入休眠狀態等待下一次系統喚醒,或者持續接收并判決直到接收到正確命令為止。

圖8 射頻采樣信號

在FPGA驗證中,運用示波器抓取相應的射頻信號波形,當射頻引腳有波形輸出時,表示能正確地接收射頻信號,驗證完成。配置相應的寄存器,用示波器抓取到的信號波形如圖8所示。

5.2.2 系統驗證

上電后,將系統復位,啟動MCU,然后MCU配置系統工作。MCU可以進入sleep,系統可進入Deep sleep模式以低功耗方式運行,在中斷情況下,MCU或者系統可以被激活,進行正常工作。射頻模塊接收發射機發出的射頻信號,振動模塊檢測振動電平信號,并通知MCU進行處理,MCU解析命令并執行相應的操作。驗證的步驟如圖9所示。驗證的場景如圖10所示。

圖9 驗證步驟

圖10 FPGA原型測試環境

結 語

[1] 楊安生,黃世震.基于ARM SoC的FPGA原型驗證[J].電子器件,2011,34(3):247-251.

[2] 章瑋.原型驗證過程中的ASIC到FPGA的代碼轉換[J].今日電子,2006(7):56-59.

[3] 張躍玲,張磊,汪健,等.FPGA的驗證平臺及有效的SoC驗證方法[J].單片機與嵌入式系統應用,2016,16(3):8-11.

程翼勝(碩士研究生),主要研究方向為芯片驗證。

FPGAPrototypeHardware/SoftwareCo-verificationBasedonSoC

ChengYisheng

(College of Communication and Information Engineering,Chongqing University of Posts and Telecommunications,Chongqing 400065,China)

In the IC design,the verification occupies a pivotal position.In order to achieve high efficiency and high reliability of the verification results to ensure that the chip in the success rate of the chip,FPGA prototype verification technology is introduced.In this paper,based on a low-power alarm SoC chip,first of all,a brief introductionof the low-power alarm SoC chip system architecture is introduced,and then the specific implementation of the alarm SoC chip FPGA prototype verification is descriped in detail.The function of the SoC chip module and the system verification are verified by the hardware and software co-verification method.

SoC;FPGA;prototype verification

TP31

A

2017-08-04)