基于有限狀態機的高速串口通信收發器的FPGA設計

陳孟春 馮建文

(杭州電子科技大學計算機學院 浙江 杭州 310018)

基于有限狀態機的高速串口通信收發器的FPGA設計

陳孟春 馮建文

(杭州電子科技大學計算機學院 浙江 杭州 310018)

針對在多任務操作系統環境下串口通信實時性和高速性受到影響的問題,提出一種基于有限狀態機的高速串口通信收發器的FPGA實現方法。串口通信收發器由波特率發生器、發送模塊、接收模塊和控制與狀態四個模塊構成,波特率發生器使用鎖相環對輸入時鐘進行倍頻和分頻;接收模塊和發送模塊分別使用一個四狀態和兩狀態的有限狀態機實現。仿真和實測結果表明,設計的FPGA串口收發器模塊電路工作穩定,速度可以達到3 Mbit/s。由于FPGA的高度并行性和有限狀態機的穩定性,使用有限狀態機實現的FPGA高速串口通信收發器在工業應用中能保證高速串行通信的實時性和可靠性。

有限狀態機 高速串行通信 收發器 FPGA

0 引 言

串行通信由于其連線少、可靠性高等特點,被廣泛應用于計算機與工業控制系統中[1-2]。傳統的RS-232、RS-485異步串行通信接口,更是成為嵌入式處理器上的標準配置接口[3]。然而,在多任務操作系統的應用背景下,因其分時共享CPU,使得串口通信的實時性與高速性受到影響[4]。雖然通過設置緩存或者開辟獨立線程來彌補時間片切換所帶來的不利影響,但是仍不能滿足工業現場對于高速串行通信的需求。隨著EDA技術的迅速發展,FPGA的可編程性、高速性、并行性等諸多優點,使其成為可編程PLD的主流器件。本文設計了一種基于FPGA的高速異步串行收發器模塊,并使用有限狀態機機制,保證了串行通信的高可靠性和高速性。

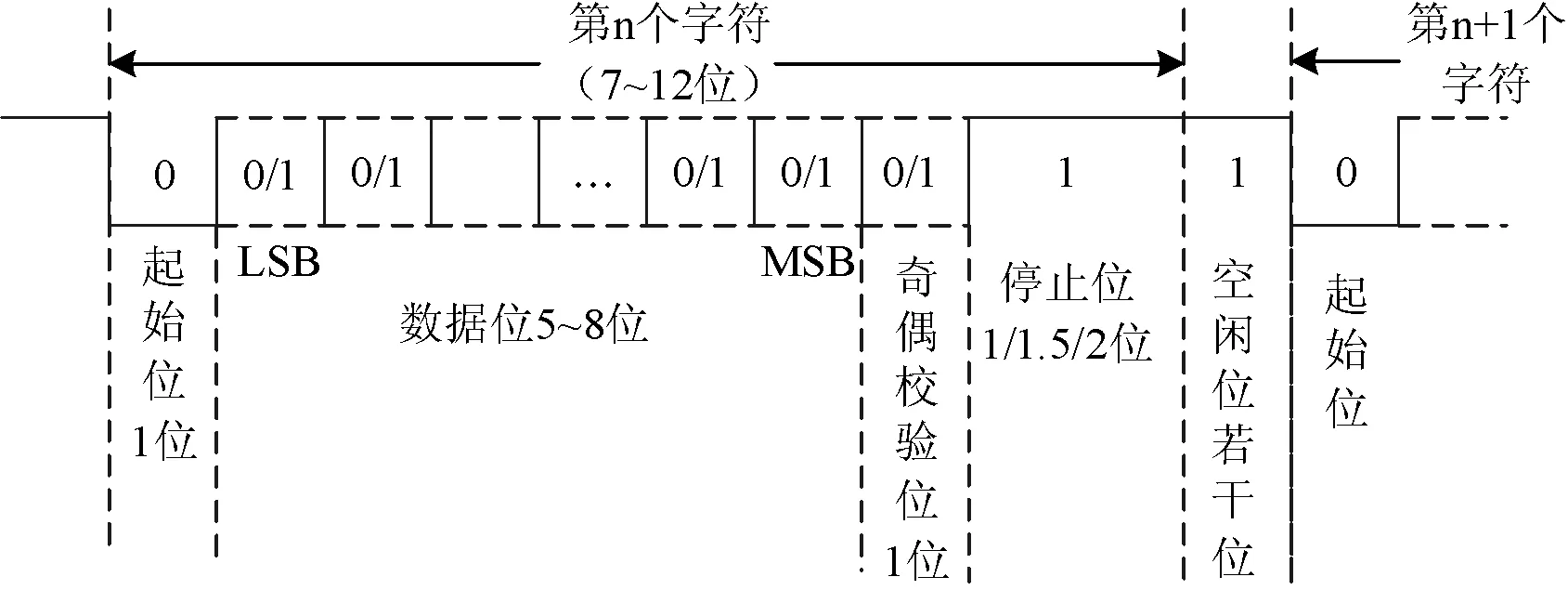

1 起止式異步串行通信

起止式異步串行通信以一個字符為一個數據幀,幀格式如圖1所示。其特點是:逐個字符傳輸,每個字符逐位傳輸,并且每幀。總是以低電平的“起始位”開始,以高電平的“停止位”結束,字符之間間隔以高電平的空閑位。幀數據按照起始位(1位)、數據位(5~8位)、奇偶校驗位(0或者1位)、停止位(1~2位)、空閑位順序排列[5]。

圖1 起止式異步串行通信數據格式

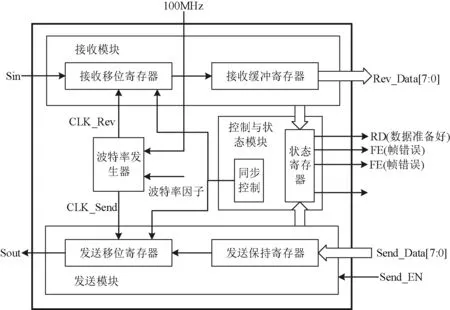

2 串行通信收發器模塊

使用Xilinx FPGA器件與Verilog HDL語言設計的串行通信收發器模塊如圖2所示。分為波特率發生器、發送模塊、接收模塊和控制與狀態模塊[5]。

圖2 異步串行收發器模塊框圖

2.1 波特率發生器

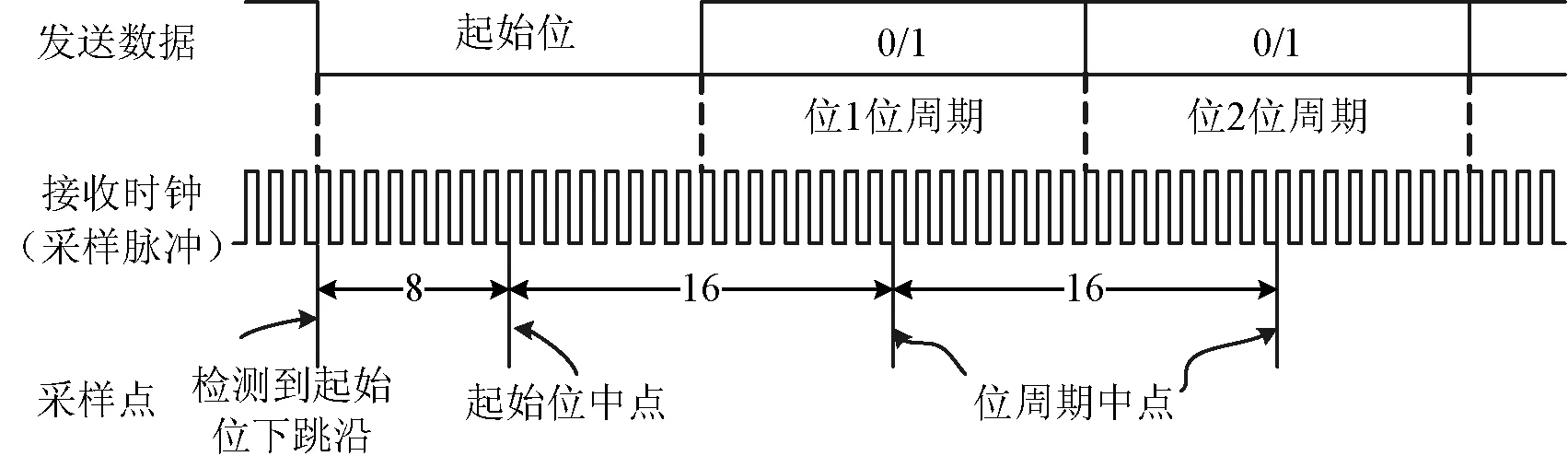

波特率發生器用于產生接收模塊所需的接收時鐘和發送模塊所需的發送時鐘,是根據約定的波特率、波特率因子,由100 MHz的時鐘源經過倍頻和分頻產生的。波特率因子為16的收發操作的位同步與采樣檢測原理如圖3所示。

圖3 收發數據同步與采樣原理

由圖3可知,發送數據是在位周期的邊緣處動作,即每16個脈沖發送一位,因此發送時鐘頻率可以等于波特率。而接收時鐘,需要更高的采樣頻率,所以接收時鐘頻率等于波特率×波特率因子。

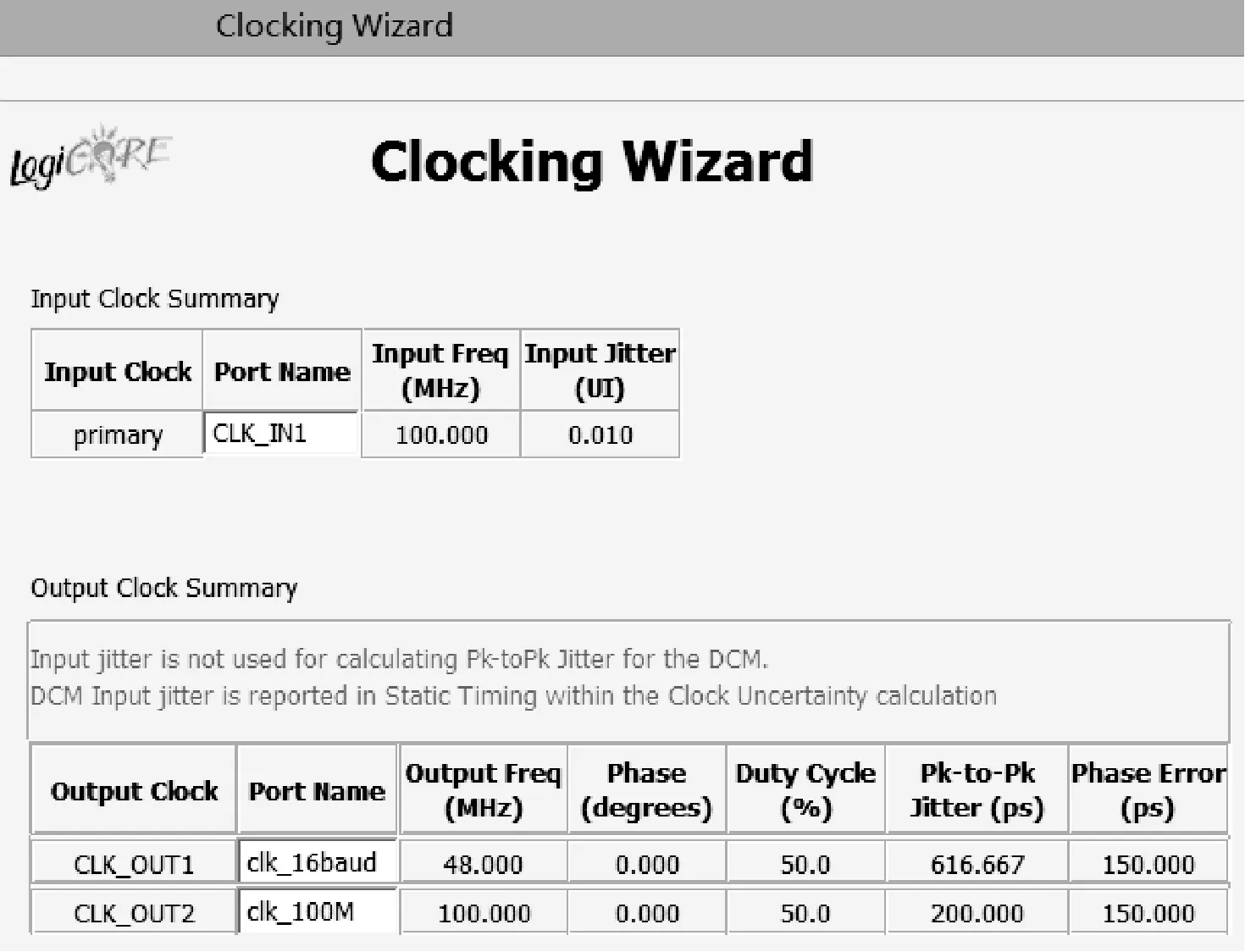

本收發器中使用了3 MHz的波特率,需要用到48 MHz的接收時鐘,故使用鎖相環IP核進行倍頻和分頻,如圖4所示。

圖4 鎖相環分頻向導示意圖

2.2 收發機制

對照圖3的收發原理,發送數據時,每16個脈沖發送一位二進制,從發送移位寄存器中,按順序發送起始位(0)、數據位(先低后高)、奇偶校驗位(可有可無)、停止位(1)。

接收數據時,則在每個接收時鐘的上沿采樣數據傳輸線,一旦監測到“0”(低電平),則表明起始位下跳沿來臨,如果數據線上低電平維持了8個采樣周期,則表明確實是起始位,而非干擾,此時是起始位位周期的中點。之后每隔16個脈沖采樣一次數據線,即在每個位周期中點處接收一位二進制數據,移位進入接收移位寄存器,直到接收完約定位數的幀數據。

3 串行通信的有限狀態機

3.1 有限狀態機概述

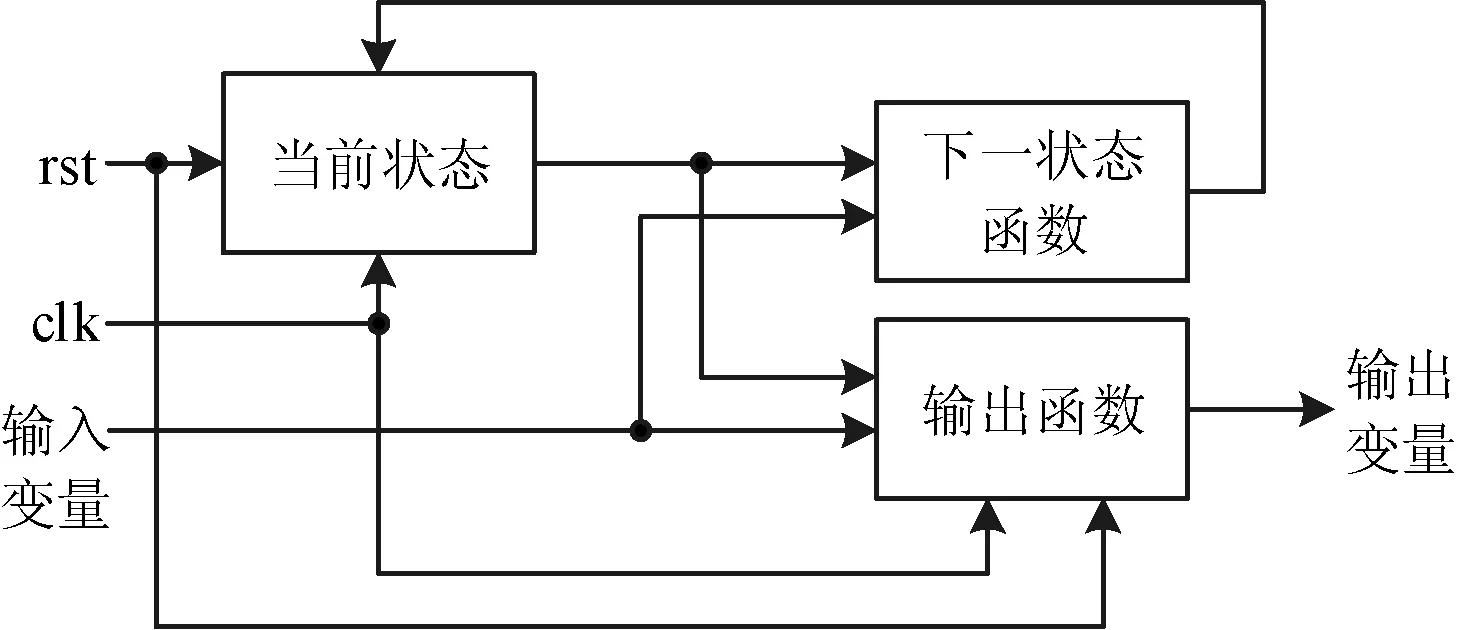

有限狀態機包含了一組有限的狀態量和兩個函數:下一狀態函數和輸出函數[7],如圖5所示。

圖5 有限狀態機結構圖

圖5中,rst信號用于確定有限狀態機的初始狀態(S0)和原始輸出,clk用于同步狀態轉換的邊沿或者定時狀態轉換的周期。狀態集包含在中間過程中可能出現的所有狀態量,使用觸發器保存。下一狀態函數,則是通過輸入變量和當前狀態確定轉移到下一狀態的組合邏輯函數。輸出函數根據當前狀態和輸入變量產生電路的一組輸出變量。與普通的時序邏輯函數一樣,如果輸出函數僅僅依賴于當前狀態,則稱該有限狀態機為Moore型狀態機。如果輸出函數不僅依賴于當前狀態,也依賴于當前輸入,則稱該有限狀態機為Mealy型狀態機[8]。

用硬件描述語言(HDL)描述的FPGA電路大都是并行實現,但是對于實際工程應用,往往需要讓硬件來實現一些具有一定順序邏輯的工作。而有限狀態機就是通過不同的狀態遷移來完成一些特定的順序邏輯。因此,有限狀態機是FPGA數字系統設計的重要工具與精髓所在[9-10]。

基于FPGA的有限狀態機的設計步驟如下[11-12]:

(1) 進行邏輯分析與抽象,確定輸入、輸出與狀態變量,畫出狀態轉移圖。

(2) 狀態簡化,得到最簡的狀態轉移圖。

(3) 對狀態進行編碼:可選擇binary、gray、one-hot編碼方式之一,在FPGA的開發綜合平臺和綜合工具中,可以進行選擇或者自定義。

(4) 用HDL描述,并綜合、仿真與實現:描述方式有一段式、二段式和三段式三種方式[11]。

3.2 串行接收模塊的有限狀態機設計

接收模塊始終掃描數據信號線Sin上的電平,一旦有數據傳送過來,則按照時鐘接收數據,并逐位串行移位至接收移位寄存器中,待數據幀接收完,則并行裝入接收緩沖寄存器。使用FPGA實現接收功能的時序如下描述:

(1) 開始通信時,信號線為空閑(邏輯1),當檢測到信號線Sin為0時,開始對“接收時鐘”計數。

(2) 當計到8個時鐘時,對Sin信號進行檢測,若仍為低電平,則確認這是“起始位”,而不是干擾信號。

(3) 接收端檢測到起始位后,每隔16個接收時鐘,讀取輸入信號Sin至接收移位寄存器,同時右移一位,直至規定的數據幀位數(含數據位和校驗位)。

(4) 16個接收時鐘后,應該收到停止位,即數據“1”,若未收到,則置位“幀錯誤”標志FE。

(5) 若收到停止位“1”,則對全部數據位進行奇偶校驗,無校驗錯時,把數據從接收移位寄存器中送接收緩沖寄存器,置“數據準備好”標志RD;如果有校驗錯,則在狀態寄存器中置“奇偶錯”標志PE。

(6) 本幀數據接收完,把線路上出現的高電平作為空閑位,回到(1)繼續監測下一幀數據。

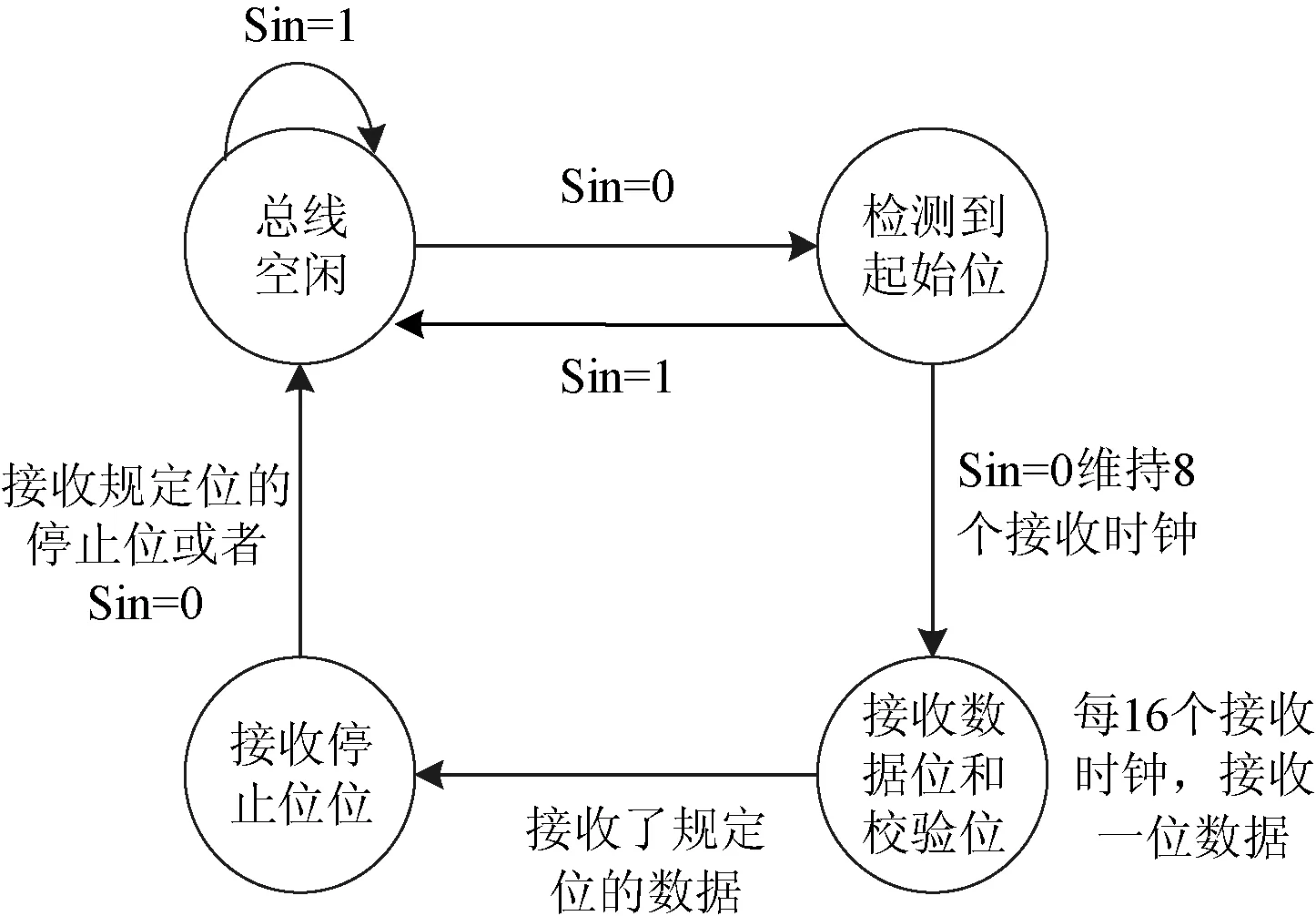

將上述時序歸納為四個狀態:總線空閑狀態、檢測起始位狀態、接收數據位和校驗位狀態、接收停止位狀態,則接收狀態機的轉換如圖6所示,圖中以波特率因子等于16為例。

圖6 接收狀態機狀態轉移圖

假設通信數據格式為:數據位8位,偶檢驗1位,停止位2位,按照兩段式書寫方法,接收狀態機模塊的Verilog HDL程序如下:

module Rev_x(

input rst,

input rev_clk,

//接收時鐘

input Sin,

//串行輸入

output reg[7:0] Rev_Data,

//并行輸出數據

output reg RD,

//已收到一個數據,可以讀取

output reg FE,

//幀格式錯誤

output reg PE,

//校驗錯誤

input clr_RD

//清RD,表明已經讀取Rev_Data

);

reg[3:0] bit_cnt;

//接收數據的位數計數器

reg[4:0] clk_cnt;

//時鐘計數器

reg[1:0] Rev_ST;

//接收狀態機的狀態

parameter Idle=0, StartBit=1, DataBit=2, StopBit=3;

//空閑狀態,起始位狀態,接收數據狀態,停止位狀態

reg[8:0] shift_reg;

//移位寄存器

always @(posedge rst or posedge rev_clk) begin

if(rst) begin

//初始賦值

Rev_ST <= Idle;

……

//信號清零,略

end

else begin

if (clr_RD) RD <= 1′b0;

case (Rev_ST)

Idle: begin

//空閑狀態

clk_cnt <= 5'b0;bit_cnt <= 4′b0;

if(!Sin) Rev_ST<=StartBit;

//狀態轉移

end

StartBit: begin

//起始位狀態

clk_cnt <= clk_cnt + 1′b1; bit_cnt <= 4′b0;

if((!Sin)&&(clk_cnt==5′d8)) begin

//起始位中點

Rev_ST <= DataBit;

//狀態轉移

clk_cnt <= 5′b0;

end

else if (Sin) Rev_ST <=Idle;

//擾動

else Rev_ST <= StartBit;

end

DataBit: begin

//數據位狀態

clk_cnt <= clk_cnt + 1′b1;

if(clk_cnt == 5'd15) begin

//16個脈沖

bit_cnt <= bit_cnt + 1′b1; clk_cnt <= 5′b0;

shift_reg<={Sin,shift_reg[8:1]};

//采樣數據

end;

if(bit_cnt == 4′d9) begin

//接收了9位數據

Rev_Data <= shift_reg[7:0];

//數據賦值

if ((^shift_reg[7:0])!=shift_reg[8])

//偶校驗

PE <= 1′b1;

//校驗錯

Rev_ST <= StopBit;

//狀態轉移

clk_cnt <= 5′b0; bit_cnt <= 4′b0;

end;

end

StopBit: begin

//停止位狀態

clk_cnt <= clk_cnt + 1′b1;

if((Sin)&&(clk_cnt==5′d31)) begin

//2位停止位

Rev_ST <= Idle;

//狀態轉移

RD <= 1′b1;

//接收到一個完整數據幀

end

else if ((!Sin)&&(clk_cnt>5′d8) &&(clk_cnt<5′d31))

begin

//停止位位數不對

Rev_ST <= Idle; FE <= 1′b1;

//幀格式錯誤

end

end

endcase

end

end

endmodule

接收模塊產生的接收標志和錯誤標志,送給控制與狀態模塊進行儲存,供頂層模塊調用。

由于受綜合工具的影響,在調試過程中,會碰到有限狀態機“跑飛”現象,即狀態機可能會進入無效狀態,且無法自啟動。因此,在ISE中設置有限狀態機的綜合選項非常重要,譬如狀態編碼(FSM Encoding Algorithm)選擇獨熱碼、開啟狀態機安全實現開關等,從而使得有限狀態機安全、可靠運行。

3.3 串行發送模塊的有限狀態機設計

發送模塊以“發送時鐘”和“波特率因子”決定一位的時間長度,如果發送波特率因子為1,則每隔1個發送時鐘發送一位,發送時鐘的頻率等于波特率。發送過程的時序控制如下:

(1) 當初始化后,或者沒有信息需要發送時,發送端輸出邏輯1到數據線Sout,即空閑位,空閑位可以有任意數量。

(2) 當需要發送時(Send_EN=1),將發送保持寄存器的內容傳送到發送移位寄存器,同時置位“發送保持寄存器空”標志THRE。

(3) 發送端首先輸出邏輯0到數據線Sout,作為起始位,維持一個位周期。

(4) 下一個發送周期,首先發送移位寄存器最低位,同時右移一位,直到各數據位發送完(含計算得到的校驗位)。

(5) 最后,發送端發送規定長度的停止位(邏輯1)。

(6) 如果沒有信息需要發送時,發送端繼續輸出邏輯1,即空閑位,空閑位可以有任意數量;如果還有信息需要發送,轉入第(2)步,發送下一幀。

在編程實現時,可以采用發送狀態機完成,將上述時序歸納為兩個狀態:總線空閑狀態、發送狀態。空閑狀態下,始終發送“1”到Sout;當狀態機檢測到發送使能有效時(Send_EN=1),則進入發送狀態,每個發送時鐘從Sout發送一位,按約定的數據格式依次發送停止位、數據位、校驗位、停止位,發送完成后進入空閑狀態。狀態轉移圖如圖7(a)所示,發送模塊的端口如圖7(b)所示。

以同樣的數據格式為例,主要程序如下:

always @(posedge rst or posedge send_clk) begin

if(rst) begin

//初始賦值

Send_ST <= Idle; shift_reg <= 12′b0;

bit_cnt <= 4′b0; Sout <= 1′b1; THRE <= 1′b1;

end

else begin

Send_EN1 <= Send_EN;

//記錄上一時鐘狀態

case (Send_ST)

Idle:begin

//空閑狀態

Sout <= 1′b1; THRE <= 1′b1; bit_cnt <= 4′b0;

if ((!Send_EN1)&& Send_EN) begin

//上跳沿

shift_reg<={2′b11,^Send_Data,Send_Data,1′b0};

Send_ST <= SendBit;

//狀態轉移

end;

end

SendBit: begin

//發送狀態

Sout <= shift_reg[bit_cnt]; THRE <= 1′b0;

bit_cnt <= bit_cnt + 1′b1;

if(bit_cnt == 4′b1011)

//12位數據發送完成后

Send_ST <= Idle;

end

endcase

end

end

4 仿真與實測

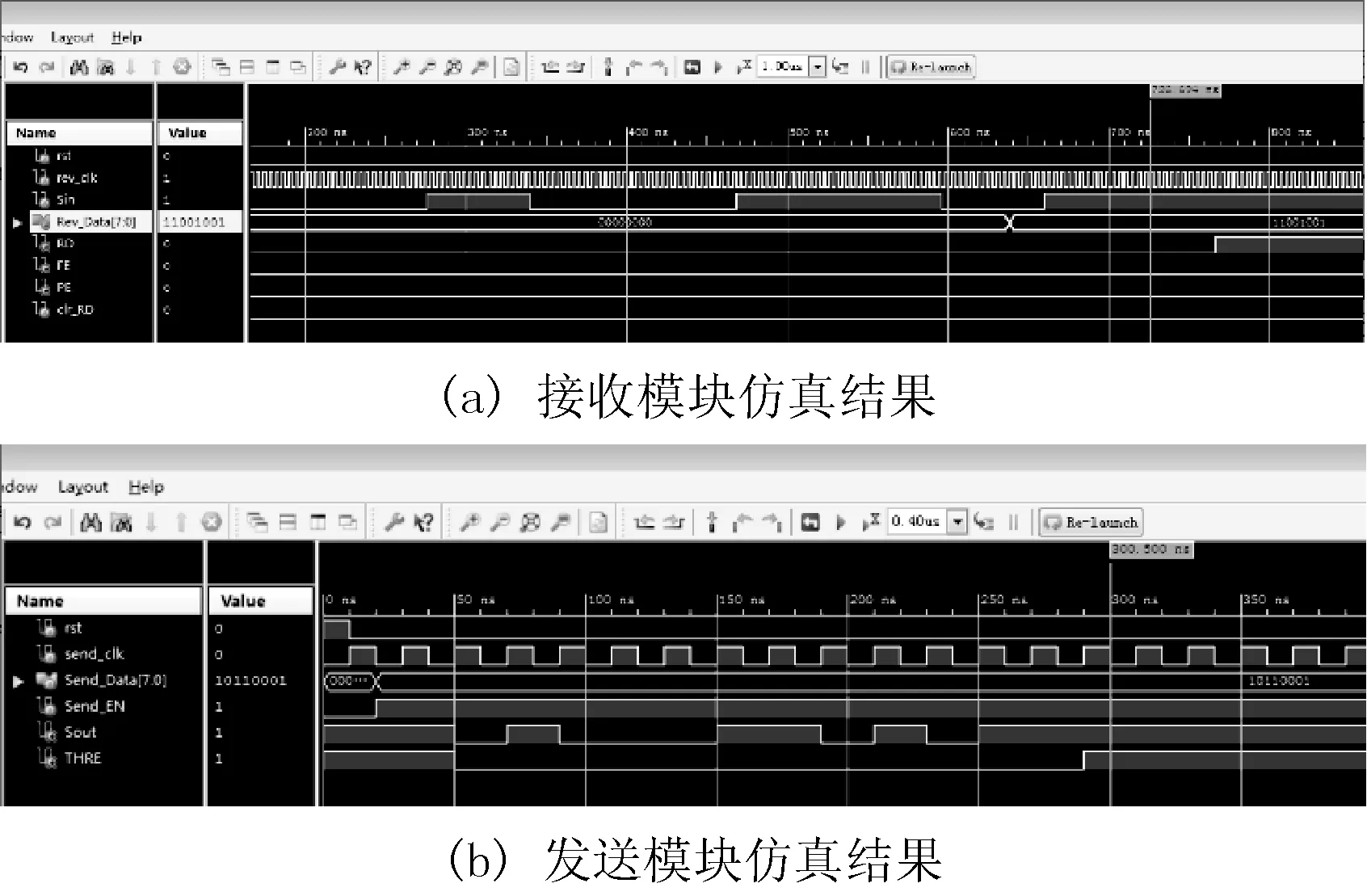

對接收模塊進行仿真,結果如圖8(a)所示,接收了一幀數據11001001B;對發送模塊仿真,結果如圖8(b)所示,發送了一幀數據10110001B。

圖8 收發模塊仿真圖

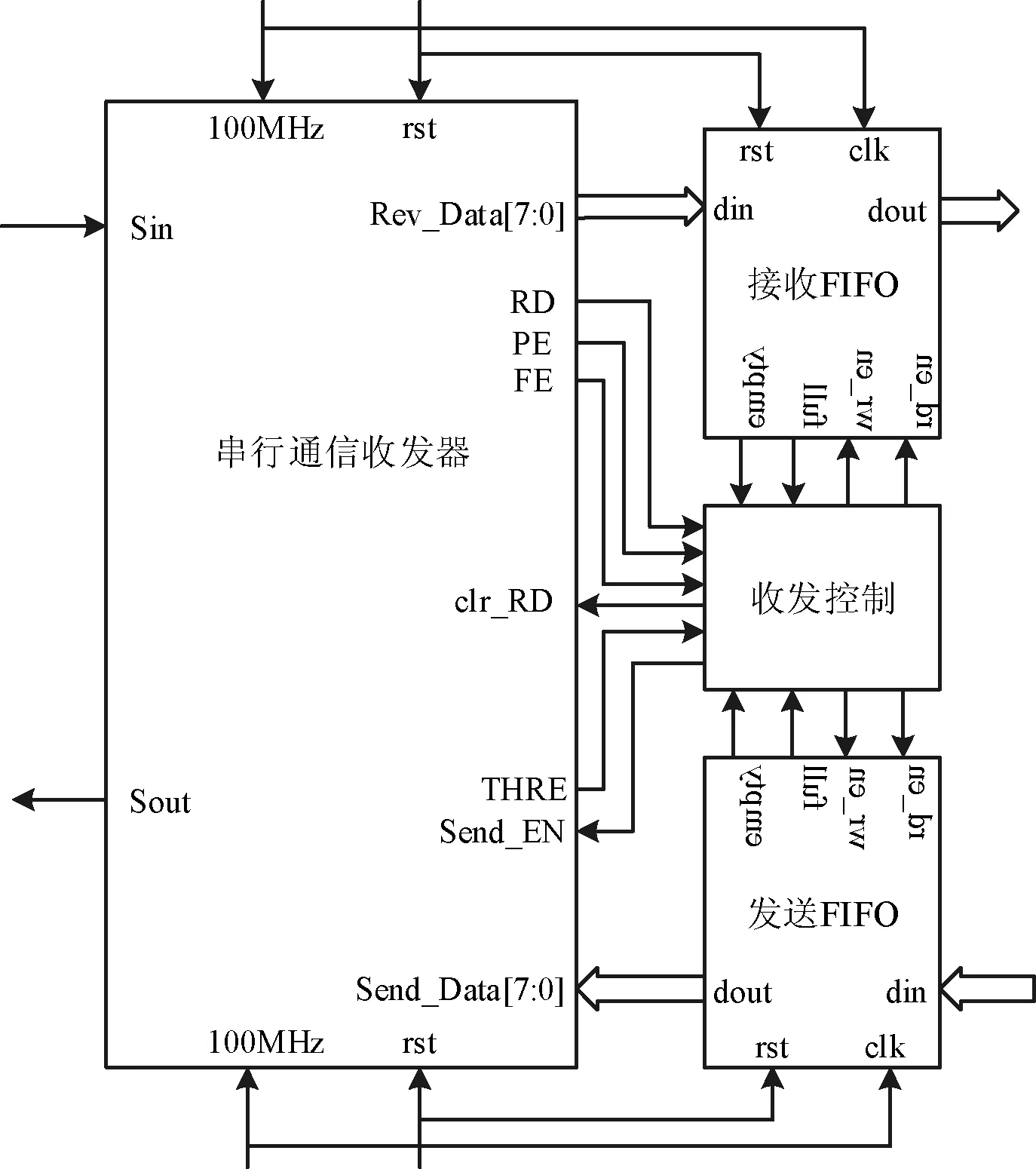

為實現高速的串口通信,需要在頂層模塊添加兩個FIFO作為接收和發送緩存區[12],頂層模塊的結構如圖9所示。

圖9 頂層模塊結構圖

測試程序將接收FIFO的dout和發送FIFO的din內部短接,具體由收發控制模塊實現:從Sin收到的數據自動寫入接收FIFO;只要發送FIFO不滿,收發控制模塊就自動從接收FIFO讀取數據寫入發送FIFO;同時只要THRE=1,就自動從發送FIFO讀取數據,從Sout發送出去。

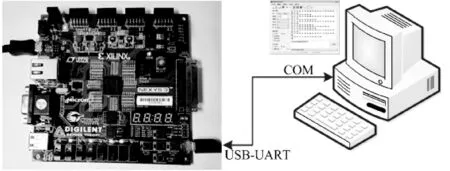

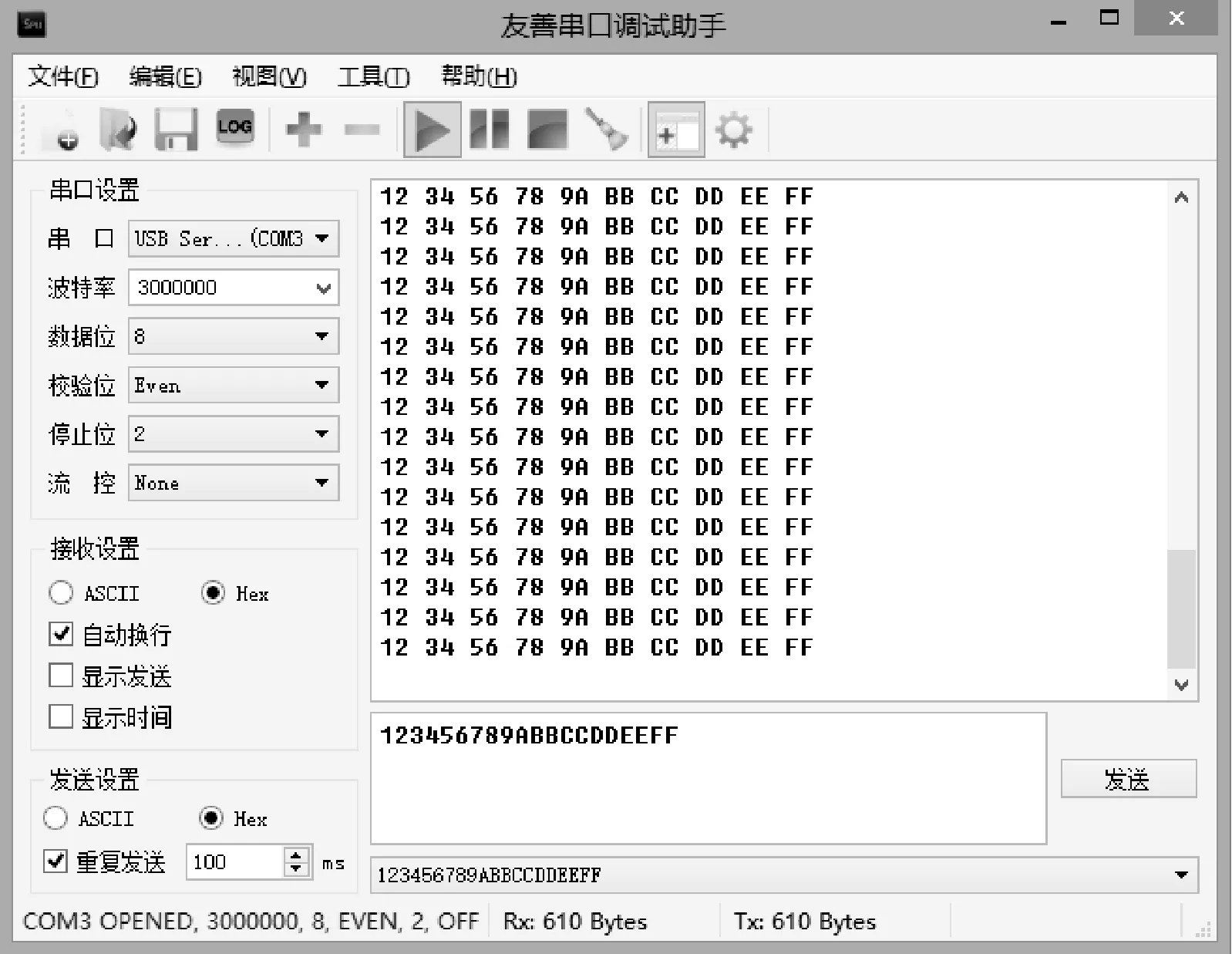

測試程序下載到FPGA測試板卡,將板卡的UART-USB口連接到PC機的COM口,連線是普通的USB連接線,圖10是實驗系統連接圖。在PC上,通過串口助手和FPGA互發信息,得到的測試結果如圖11所示。

圖10 實測與調試系統

圖11 PC串口助手收發數據

圖11選擇重復發送10個數據,則PC機發送數據到FPGA的UART,FPGA頂層模塊將接收的數據經由接收FIFO和發送FIFO,又重新發送回PC端。可以看出,在以3 Mbit/s的高速速率連續傳輸數據時,仍能收發正確。

5 結 語

本文使用有限狀態機實現了基于FPGA的高速串行通信收發器的設計,分頻器精準,接收自動機和發送自動機完全并行執行,自動差錯檢測,實時性好,可靠性高,適應于高速系統。經過升級改造后,應用于某航天測控系統的發射控制繼電柜,實現了3 Mbit/s的高速RS-422串口通信。

在頂層模塊可添加設置通信參數的端口,則將具有更好的通用性;在上層模塊設計接收和發送FIFO模塊,將進一步提高串行通信的可靠性和速度。

[1] 戴彥,王誠意,孫春.基于FPGA的RS-232串行通信設計[J].唐山學院學報,2011,24(3):74-76.

[2] 劉亞兵,馬瑞卿,張慶超,等.基于FIFO的串口通信模式研究[J].計算機測量與控制,2014,22(7):2301-2303.

[3] 于志翔.基于FPGA的UART設計與實現[J].電子測量技術,2015,38(3):77-81.

[4] 羅檸,皮佑國.基于FPGA的高速串行通信接口研究[J].信息技術,2013(7):113-116.

[5] 馮建文,章復嘉,包健,等.基于FPGA的數字電路實驗指導書[M].西安:西安電子科技大學出版社,2016:137-140.

[6] 鄧岳平,肖鐵軍.基于FPGA的并行DDS信號發生器的設計與實現[J].計算機工程與設計,2011,32(7):2319-2323.

[7] 陳勇.有限狀態機的建模與優化設計[J].重慶工學院學報(自然科學版),2007,21(5):55-58.

[8] Wakerly J F.數字設計原理與實踐[M].林生,葛紅,金京林,譯.4版.北京:機械工業出版社,2007:387-396.

[9] 孔昕,吳武臣,侯立剛,等.基于Verilog的有限狀態機設計與優化[J].微電子學與計算機,2010,27(2):180-183.

[10] 劉小平,何云斌,董懷國.基于Verilog HDL的有限狀態機設計與描述[J].計算機工程與設計,2008,29(4):958-960.

[11] 吳厚航.深入淺出玩轉FPGA [M].2版.北京:北京航空航天大學出版社,2013:35-38.

[12] 陳標龍,王保成,周江華.基于FPGA和FIFO技術的多串口系統設計與實現[J].計算機測量與控制,2013,21(10):2835-2837.

FPGADESIGNFORHIGHSPEEDSERIALCOMMUNICATIONTRANSCEIVERBASEDONFINITESTATEMACHINE

Chen Mengchun Feng Jianwen

(SchoolofComputerScience,HangzhouDianziUniversity,Hangzhou310018,Zhejiang,China)

Under the environment of multitask operating system, the character of real-time and high speed of serial communication is significantly affected. This article puts forward an FPGA implementation method of high speed serial communication transceiver based on finite state machine. The serial communication transceiver consists of four modules, baud rate generator, transmission module, reception module and control and status module. The baud rate generator uses a phase-locked loop to multiply and divide the input clock. The reception module and the transmission module use a finite state machine of four states and two states, respectively. Simulation and experimental results show that the FPGA serial transceiver module circuit works stably with the speed up to 3 Mbit/s. Due to the high parallelism of FPGA and the stability of finite state machine, the FPGA high speed serial communication transceiver based on finite state machine can guarantee the real-time and reliability of high speed serial communication in industrial applications.

Finite state machine High speed serial communication Transceiver FPGA

2017-03-22。國家自然科學基金項目(61471150)。陳孟春,本科生,主研領域:計算機應用。馮建文,副教授。

TP331.2

A

10.3969/j.issn.1000-386x.2017.12.034