渦流檢傷信號高速實時采集系統的研究

劉 康,彭樂鋒,劉 繼

渦流檢傷信號高速實時采集系統的研究

劉 康,彭樂鋒,劉 繼

(同濟大學鐵道與城市軌道交通研究院,上海201800)

渦流無損檢測在近年來取得了很大的發展,在工業檢測領域有著重要的應用。作為渦流探傷設備的重要環節,高速信號實時采集傳輸模塊的速度的穩定性通常是設備的瓶頸所在。硬件平臺采用Xilinx公司的Zynq SoC,同時集成軟件平臺基于Linux操作系統,通過AXI DMA傳輸FIFO的渦流檢傷數據到DDR內存,供上位機用戶程序使用。比較輪詢和中斷兩種機制啟動AXI DMA,確定中斷方式可以實現實時采集和處理而無數據丟失情況。同時Linux驅動中斷處理程序采用Netlink消息機制通知用戶程序啟動AXI DMA。經測試,該渦流信號采集系統傳輸速度和穩定性滿足性能要求。

渦流檢測;Zynq片上系統;片內擴展總線;直接內存存取;中斷;Netlink套接字

1 引 言

電磁渦流檢測是一種重要的無損檢測技術,已廣泛用于現代工業領域,具有結構簡單、靈敏度高、頻率特性好、可非接觸性測量和易于實現自動化等特點[1]。針對電磁渦流檢測中數據采集量大、實時性要求高的特點,設計一個新型渦流信號高速實時采集系統十分必要。

目前的渦流無損探傷設備的設計方案大都基于FPGA+ARM+上位機架構方案,FPGA實現DDS輸出激勵信號,并承擔渦流數據采集的任務,ARM承擔缺陷評估和IO模塊控制功能并通過TCP協議和上位機通信,而上位機承擔人機交互,離線數據存儲的功能[2];或者加入DSP芯片,用來實現數據濾波的功能[3]。這些方案都面臨著研發周期長,底層硬件方案復雜,ARM或者DSP和FPGA之間數據傳輸慢、不穩定等問題。隨著工業自動化水平不斷提高,對渦流探傷設備的高速實時采集和處理要求也不斷提高,提出一種基于Zynq SoC的渦流信號高速實時采集系統。Zynq SoC同時集成雙核ARM和FPGA,打破了傳統的ARM/DSP+FPGA核架構,提供一種新型解決方案[4]。

2 平臺設計

2.1 Xilinx Zynq-7000 SoC

Xilinx Zynq-7000 SoC集成兩個主頻高達1GHz的ARM Cortex-A9內核和FPGA,每個內核都配有NEON高性能媒體引擎進行浮點運算,可用于數學運算或者視頻編碼解碼。ARM配有AMBA開放總線互聯端口,可以通過AXI片內高速總線互聯和FPGA通信,帶寬速度高達100Gbps。ARM帶有DDR內存控制器硬核,支持最大1GB地址空間,支持64MB的TrustZone安全認證區域,支持DDR3、DDR3L、DDR2等多種內存,適合用作系統的高速存儲[5]。

2.2 AXI總線

AXI(Advanced eXtensible Interface)是一種總線協議,是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0協議中最重要的部分,是一種面向高性能、高帶寬、低延遲的片內總線。隨后ARM公司推出的升級版本AMBA 4.0總線包括AXI、AXI-Lite、AXI-Stream三種標準。其中 AXI-Lite是AXI的簡化版本,用于訪問低速外設,AXI-Stream進行數據傳輸的時候不需要地址,適用于視頻,高速AD,PCIe等需要高速流數據傳輸的場合[6]。

AXI3,AXI4和AXI4-Lite基于內存映射協議,所有的傳輸都是在系統內存空間實現的。由于內存映射系統的一致性,通過AXI-GP或者AXI-HP端口連接到PS系統總線的IP核,它的控制寄存器直接映射到指定的PS系統內存地址上。這也是ZYNQ實現PS(Process System)控制PL(Programmable Logic)的根本原因。系統整體框架如圖1所示,由AXI總線在其中的地位可知,它是連接PS和PL的核心技術。

圖1 渦流信號高速采樣系統整體框架

2.3 系統框架

從圖1可見,A/D轉換器采集到的渦流信號,經過相敏檢波后進入FIFO,AXIDMA通過AXI-HP0端口將FIFO數據送到DDR,ARM從DDR獲取數據,進行進一步處理。

軟件流程步驟:

1.用戶空間啟動程序,CPU向FIFO控制IP核發送開啟指令,經過相敏檢波后的渦流數據被允許進入FIFO,同時FIFO累加器開始累加進入FIFO的數據量;

2.當累加器的值達到預先設置的閾值時,FIFO控制IP核發通過gic(通用中斷控制器)向CPU發送中斷,并自動清空自身累加的值,但FIFO內的數據仍然存在;

3.CPU接收到中斷時,啟動AXIDMA傳輸,將FIFO數據遷移到指定DDR內存地址;

4.傳輸結束后,處理DDR內存對應地址的數據,應用程序進行數據濾波后顯示阻抗平面圖;

5.關閉程序時,CPU向FIFO控制IP核發送關閉指令,禁止數據流進入FIFO。

3 AXIDMA高速傳輸流程

AXI DMA是Xilinx官方提出的用于高速數據傳輸的IP核,可以實現雙向數據傳輸,最大傳輸速度可以達到300 MB/s[7]。同時ARM可以通過AXI-Lite端口控制AXIDMA的運行并獲取傳輸狀態。

用戶空間初始化AXIDMA步驟:

1.打開設備文件;

2.使用mmap()進行內存映射,底層驅動會將驅動初始化申請的內存地址傳遞給用戶空間;

3.探測AXIDMA的通道數目,發送通道和接收通道視為不同的通道;

4.設置AXI DMA-0接收通道的基本參數,比如傳輸方向,延時時間,復位狀態。

用戶空間在接收到Netlink消息后,啟動DMA傳輸步驟:

1.設置緩存的信息,比如緩存長度,起始偏移,傳輸方向,緩存對應的通道;

2.啟動AXIDMA-0的接收通道,在接收完成后發送完成信號。

內核態AXIDMA驅動啟動一次傳輸的步驟如圖4所示。

圖2 AXIDMA驅動傳輸步驟

在滿負荷狀態下,進行AXIDMA自收自發測試,可以看到滿載傳輸速度為250MB/s。在測試渦流數據傳輸時,設置數據量分別為64KB、1MB以及4MB,檢測到傳輸速度分別為285MB/s、279MB/s和269MB/s。同時程序持續運行6h沒有崩潰,滿足渦流數據高速傳輸和穩定性的要求。

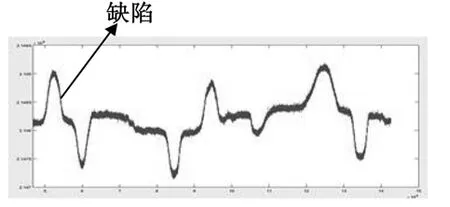

4 中斷和輪詢方案實時性比較

AXIDMA的啟動有兩種方案:PL端FIFO中斷通知用戶程序啟動AXIDMA或者用戶程序定時查詢中斷狀態位寄存器并啟動AXIDMA。由于相敏檢波數據量的大小會根據用戶設置的參數變化,輪詢機制無法準確判斷FIFO中斷狀態寄存器的狀態,可能導致FIFO溢出,數據丟失。而中斷機制可以保證用戶程序及時收到通知。如圖3所示為分別使用中斷和輪詢方案進行渦流探傷曲線。

圖3 輪詢和中斷方案渦流探傷曲線

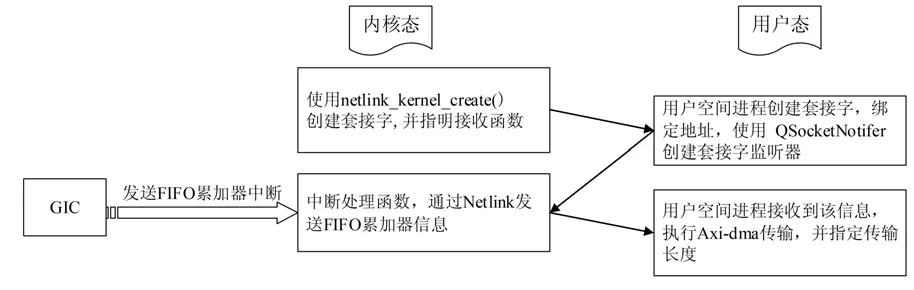

5 異步通信機制Netlink

中斷方案需要在驅動的中斷處理函數中通知用戶程序。由于中斷上下文不能允許引起阻塞的函數,因此傳統的copy_from_user()和copy_to_user()不能使用,因為調用might_sleep(),可能導致睡眠。Netlink是一種在內核與用戶程序之間進行雙向數據傳輸的非常好的方式,用戶態使用標準的socket API就可以使用Netlink提供的強大功能;內核態需要使用專門的API來使用Netlink。

Netlink套接字的通信依據是一個對應于進程的標識,一般定為該進程的ID。Netlink通信最大的特點是對中斷過程的支持,它在內核空間接收用戶空間數據時不再需要用戶自行啟動一個內核線程,而是通過另一個軟中斷調用用戶事先指定的接收函數。通過軟中斷而不是自行啟動內核線程保證了數據傳輸的及時性[8]。

和其他通信機制相比,Netlink有如下優點:

1.支持全雙工通信,由于套接字的全雙工特性,一條Netlink連接可以同時用于用戶空間和內核空間的互傳消息;

2.Netlink支持多播,屬于一個Netlink組的模塊和進程都能獲得該多播消息;

3.采用異步通信機制,基于socket緩存隊列;

4.內核可以使用Netlink首先發起會話,而系統調用和ioctl只能由用戶程序發起調用。

如圖4所示為利用Netlink通信通知AXIDMA啟動一次傳輸的步驟。

圖4 Netlink通信啟動AXIDMA傳輸

通過比較內核發送消息的時間和用戶程序接收到消息的時間,可以得到Netlink通信的延遲時間。經測試,采用Netlink通信的延遲在1ms以內,滿足通信實時性的要求。

6 結束語

基于ZYNQSoC的高速實時采集系統,完全可以代替傳統的DSP/ARM+FPGA架構。將ZYNQSoC運用到渦流探傷設備上,PL端實現DDS激勵信號發生器,數據采集和相敏檢波等功能,PS端實現數據濾波,阻抗平面圖繪制,數據傳輸通過AXIDMA實現,傳輸速度達到250MB/s,滿足高速渦流信號的傳輸要求,同時基于Netlink的異步通信機制滿足實時性要求,實現了更高效、更節省的解決方案。

[1] 張俊哲.無損檢測技術及其應用:第2版[M].北京:科學出版社,2010.Zhang Junzhe.The Nondestructive Testing and Its Application:2nd Edition[M].Beijing:China Science Publishing Media,2010.

[2] 呂世磊.高速在線渦流探傷系統的設計與實現[D].華東理工大學,2015.Lv Shilei.Design and Implementation of High-speed Online Eddy Current Testing System [D].East China University of Scienceand Technology,2015.

[3]劉增.嵌入式雙CPU脈沖渦流檢測數據采集系統的設計與實現[D].江蘇科技大學,2012.Liu Zeng.Design and Implementation of Pulse Eddy Current Testing Data Acquisition System Based on Embedded Dual-CPU[D].Jiangsu Universityof Scienceand Technology,2012.

[4] Louise Crockett,Ross Elliot,Martin Enderwitz.The ZYNQ Book:1st Edition[M].UK :Strathclyde Academic Media,2014.[5] Xilinx Inc.ug585-Zynq-7000-TRM(EB/OL).http://www.origin.xilinx-china.com/.2016.09.27.

[6] Xilinx Inc.ug1037-vivado-axi-reference-guide(EB/OL).http://www.origin.xilinx-china.com/.2105.06.24.

[7] Xilinx Inc.pg021_axi_dma(EB/OL).http://www.origin.xilinx-china.com/.2106.10.05.

[8]Campbell J,Comer D.Software:Practiceand Experience[M].John Wiley&Sons,1991.

Research on High-speed and Real-time Eddy Current Data Acquisition System

In recent years,eddy current nondestructive testing has made great progress,and has an important application in the industrial inspection field.As an important part of eddy current testing instrument,the speed stability of high-speed signal real-time acquisition and transmission module is usually the bottleneck of the equipment operation.Zynq SoC from Xilinx Company is chosen as the hardware platform,while the software platform is based on Linux operation system,and through AXI DMA,FIFO eddy current test data is transferred to DDR memory to supply upper computer user program for use.By comparing the two mechanism of polling and interrupt to start AXI DMA,it is determined that the interrupt method can anchieve the real-time acquistion and disposal without data loss.At the same time,Netlink message mechanism is chosen by Linux diver interrupt disposal program to inform user program to start AXI DMA.After test,it is proved that the speed and stability of this eddy current signal acquisition system can meet the performance requirement.

Eddy current testing;Zynq SoC;AXI;DMA;Interrupt;Netlink socket

10.3969/j.issn.1002-2279.2017.06.020

TP277

A

1002-2279-(2017)06-0086-04

劉康(1994—),男,湖北省黃石市人,碩士研究生在讀,主研方向:無損檢測。

2017-09-18