基于FPGA的模擬視頻信號到SDI信號轉換的實現

張曉晶

摘要:隨著眼下數字電視的普及和多媒體技術的迅猛發展,數字視頻數據日益增多。數字化引起了電視技術領域的極大變革。如何將已經存在的模擬視頻信號轉換為SDI信號已經成為一個重要的課題。目前,我國處于模擬、數字信號并存階段,而模擬視頻信號到SDI信號的轉換就是這個過渡階段必不可少的關鍵性技術。本文介紹了一種基于FPGA芯片的實時視頻圖像處理系統。詳細討論了從模擬復合視頻信號CVBS到SDI信號之間的轉換過程。經實驗結果證明,本設計基本實現了模擬視頻信號到SDI信號的轉換,達到了一定的預期效果。

關鍵詞:模擬信號;SDI信號;FPGA;I2C總線

中圖分類號:TN791 文獻標識碼:A 文章編號:1007-9416(2017)11-0059-03

隨著多媒體技術及Internet的迅速發展,人們對數字化的需求日益增加,圖像、音頻、視頻等多媒體數據大量涌現。視頻作為一種主要的媒體類型,在豐富人們的生活、教育、娛樂等方面起到了越來越突出的作用。同時,隨著視頻類型的增加和數據量的日益龐大,如何有效地傳輸這些數據已成為一種迫切的需求。并且毫無疑問數字電視是個大方向,與其它任何事物的發展一樣,中國數字電視產業的發展,也有其自身發展的規律。目前,我國處于模擬、數字信號并存階段,而模擬視頻信號到SDI信號的轉換就是這個過渡階段必不可少的關鍵性技術。

1 研究對象與方法

本次研究將開發一個FPGA硬件平臺,該平臺利用TVP5150解碼芯片對由攝像頭采集到的視頻數據進行A/D轉換,得到的數據流經FPGA處理最終輸出SDI信號。我們使用到的TVP5150是超低功耗、支持NTSC/PAL/SECAM等格式的高性能視頻解碼器,在正常工作時,它的功耗僅115 mW,并且具有超小封裝(32腳的TQFP),因此非常適用于便攜、批量大、高質量和高性能的視頻產品。基于FPGA的模擬視頻信號到SDI信號轉換的實現也在推動著數字化的進一步發展和成熟。因此,本研究有著非常重要的現實意義。

2 系統方案設計

2.1 硬件系統描述

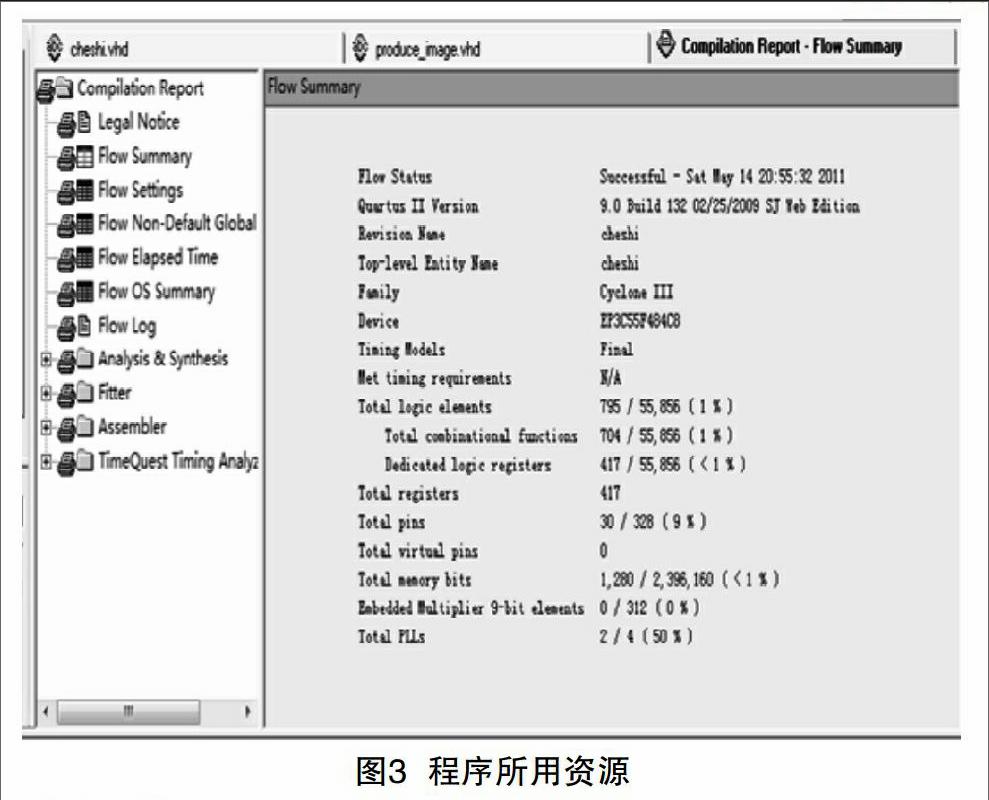

對于一路模擬視頻信號,將其作為輸入接到我們設計的實驗箱上,經過處理后輸出為SDI格式的串行數字信號。整個硬件平臺如圖1所示,其中FPGA采用高性能的CycloneIII EP3C55F484芯片[1]。

開發板外形如圖2所示。開發板涉及的硬件有:(1)FPGA芯片:EP3C55F484C8;(2)解碼芯片:TVP5150;(3)攝像頭;(4)并串轉換芯片:CY7B9234;(5)SDI輸出驅動芯片:CLC007;(6)27M晶振一個;(7)程序下載電纜USB Blaster一條;(8)顯示器。

本硬件平臺已具有實現模擬視頻信號到SDI信號的轉換的功能。模擬視頻的解碼需要解碼芯片TVP5150來完成,I2C總線的配置和加擾等功能都需要FPGA來完成。本平臺綜合布局FPGA,在QuartusII環境下加擾碼、NRZI編碼器,集成為完整的可編程片上系統。至此,硬件部分的設計完成[2]。

2.2 硬件系統與FPGA關聯過程

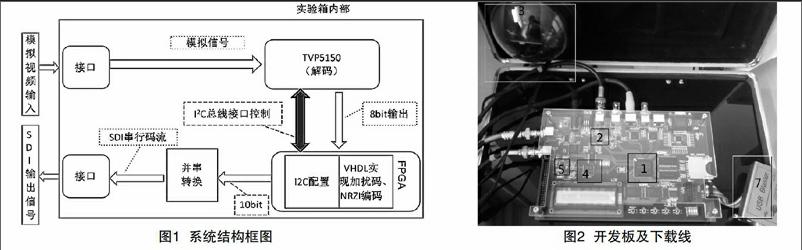

本次課設使用FPGA芯片為Cyclone III的EP3C55F484C8,功能較為強大,整個程序僅使用了其很少一部分資源,其中使用了9%的管腳和兩個鎖相環[3]。具體情況如圖3所示。

整體設計流程分為“前期”工程和“后期”工程兩步。所謂“前期”步驟開始于提出基本方法和建立在框圖層次上的模塊,大型的邏輯設計通常是分層次的。第二步是真正為模塊編寫VHDL程序,包括接口,內部細節。第三步是仿真/驗證。仿真/驗證之后,進行“后期”階段的工作,“后期”階段分為三個步驟:邏輯綜合、裝配與布局/布線、延時分析。

編寫程序完成后,要選擇與開發板上使用FPGA芯片對應的芯片,本設計中選擇的是EP3C55F484C8,選擇的方法是Assigments/Device,在Device Family中選擇Cyclone III,Availiable device中選擇EP3C55F484C8即可。在編譯無誤后進行引腳的分配。在開發板上,FPGA芯片與其它外圍設備的連接時固定的,各引腳都與不同外圍芯片的不同引腳相連,經過以上編譯,片上系統已經為映射到相應EP3C55F484C8芯片產生了FPGA資源的分配文件[4]。引腳分配界面如圖4所示。

分配好引腳后的某些選項需要設置。選Assigments/Device/Device and pins Options進行設置。對于沒有用到的引腳,在Unused Pins標簽頁選擇As inputtri-stated。經過這步設置后,再編譯工程就會正常而不報錯。編譯無錯后,可以使用Quartus II中的Tool/Programmer將生成的FPGA分配文件通過USB Blaster從PC機下載到FPGA芯片中,以上步驟完成后硬件系統就與FPGA芯片內部相關聯了[5]。

3 信號解碼流程

3.1 關于TVP5150解碼模塊

只有將模擬視頻信號轉換成為符合ITU-R BT.656標準的數字信號,才可方便地利用FPGA或者DSP甚至PC機來進行信號處理。本模塊就是利用超低功耗TVP5150芯片對視頻信號A/D解碼,由FPGA通過I2C總線控制,預留地址數據等接口,作為后續數字信號處理之用。視頻采集系統由攝像頭與解碼芯片TVP5150兩部分組成。CCD攝像頭輸出的模擬視頻信號,通過解碼芯片TVP5150的放大,抗混疊濾波和A/D轉換等處理后將模擬信號轉換為數字視頻信號。解碼芯片TVP5150由I2C總線控制。 FPGA通過I2C控制模塊配置TVP5150后,就可以在輸入時鐘(CLK,27MHz)的同步下讀入YCRCB 4:2:2格式的并行8bit視頻數據[6]。endprint

3.2 對解碼后的數據進行處理使之成為標準SDI格式

SDI接口是數字串行接口(serial digital interface),是把數據字的各個比特以及相應的數據通過單一通道順序傳送的接口。由于串行數字信號的數據率很高,在傳送前必須經過處理。用擾碼的不歸零倒置(NRZI)對原始數據流進行擾頻,并變換為NRZI碼確保在接收端可靠地恢復原始數據。這樣在概念上可以將數字串行接口理解為一種基帶信號調制。SDI接口能通過270Mb/s的串行數字分量信號[7]。

本系統解碼后的輸出數據對極性很敏感,容易造成鎖相環失鎖,從而產生嚴重的接收誤碼。通過加擾可以消除這些缺陷。使用VHDL語言實現信號的加擾碼和NRZI編碼的編程實現思路:

G1(X)=X9+X4+1

G2(X)=X+1

編程思路:對一組數據實時進行處理,一組含10bit數據。將10bit數據分為三組:0~4bit、5~8bit、9bit分別進行循環編碼打到編碼目的。

3.3 對系統I2C總線進行配置

我們基于FPGA,使用VHDL語言對整個系統的I2C總線進行配置。程序思路:本次設計中,我們僅設置了I2C的一部分功能。把TVP5150設計為主機,FPGA為從機,僅僅由TVP5150向FPGA寫數據。

因為I2C的在傳送數據時,分為等待開始信號、開始、傳送數據、等待應答、結束等幾個工作模式,我們可以type state_n is (waitn,start,wr,ask,delay,stop),考慮到在數據的傳輸中會發生很多不可預料的情況,我們引入一個時延,在這個時延范圍內我們就按照I2C總線的工作流程而執行,一旦超出這個時延而未等到我們所需信號時,程序就轉到結束模式,等待下一次的開始信號。這樣就避免了程序走入死胡同,保證了程序的正常運行。在本次課設中通過Quartus II中的功能添加一個鎖相環模塊,并選擇輸出為27M/122=211 KHz的時鐘信號來作為I2C程序的驅動程序[8]。

4 結語

本論文介紹了一種基于FPGA芯片的實時視頻圖像處理系統。詳細討論了從模擬復合視頻信號CVBS到SDI信號之間的轉換過程:模擬視頻信號經過解碼芯片TVP5150的A/D轉換,轉換為ITU-R BT.656格式的8bit并行數字視頻信號,該數字信號在FPGA內擴充為10bit并進行加擾碼和NRZI編碼運算,經過處理后輸出為10bit,27M的并行數字信號,之后經過并串轉換得到270M串行SDI信號,并將該信號接于顯示屏上。本系統在QuartusII軟件平臺下開發并在硬件上得到實現。經實驗結果證明,本設計基本實現了模擬視頻信號到SDI信號的轉換,達到了一定的預期效果。

參考文獻

[1]姜秀華,柴劍平,林正豹,等.現代電視原理[M].高等教育出版社,2008.

[2]李國洪,胡輝,沈明山.EDA技術與實驗[M].機械工業出版社,2009.

[3]李宰辛.Altera發布Quartus II軟件8.1,延續效能領先優勢[N].Altera資訊,11-2008.

[4]劉韜.FPGA數字電視系統設計與開發實例導航[M].北京:人民郵電出版社,2005.

[5]于楓,張麗英,等.ALTERA可編程邏輯器件應用技術[M].北京:科學出版社,2004.

[6]張凱,林偉.VHDL實例剖析[M].國防工業出版社,2004.

[7]ITU601/656編碼標準.國際電信聯盟無線電通信部門656-3號建議書[S].1982.

[8]Wayne.Wolf FPGA-Based System Design[M].機械工業出版社,2005.

Abstract:With the popularity of digital television now and the rapid development of multimedia technology, digital video data is increasing. Digital TV technology caused a great change. How to transform analog video signals existed to SDI signal has become an important issue. At present, We are in a phase that analog signals and digital signals are co-existenced, while the analog video signals to SDI signal conversion is the key technology essential to the transition phase.This topic describes the FPGA-based real-time video image processing system. Finally, the experimental results prove that the design of the basic realization of analog video signals to SDI signal conversion.

Key Words:Analog signal; SDI signal; FPGA; I2C BUSendprint