用于圖像壓縮系統(tǒng)的SDRAM控制器設(shè)計

吳聰睿 ,張忠偉 ,張學(xué)全

(1.中國科學(xué)院大學(xué)北京100190;2.中國科學(xué)院國家空間科學(xué)中心北京100190)

在基于FPGA的圖像壓縮系統(tǒng)中,由于圖像壓縮核的圖像接收速率與處理速率的不同,需要對圖像數(shù)據(jù)執(zhí)行緩存操作,這就需要設(shè)計高速率、高容量的緩存器。目前構(gòu)成緩存的存儲芯片主要有FLASH、FIFO、SRAM、SDRAM等,對這幾種緩存芯片的性能進行比較,由于SDRAM存儲容量大、讀寫速率高、價格低、體積小,所以SDRAM是理想的緩存器件[1-3]。但是由于SDRAM結(jié)構(gòu)設(shè)計的特點,導(dǎo)致其工作機制特殊,控制邏輯復(fù)雜,時序要求較高,使用起來有一定難度。雖然有一些專用芯片提供SDRAM控制功能,可是其可控制性和靈活性不足,不能滿足特殊需求[4-5],所以本文結(jié)合實際應(yīng)用,設(shè)計了一種基于FPGA的SDRAM控制器方案,以滿足圖像壓縮系統(tǒng)的使用需求。

1 SDRAM控制操作與時序

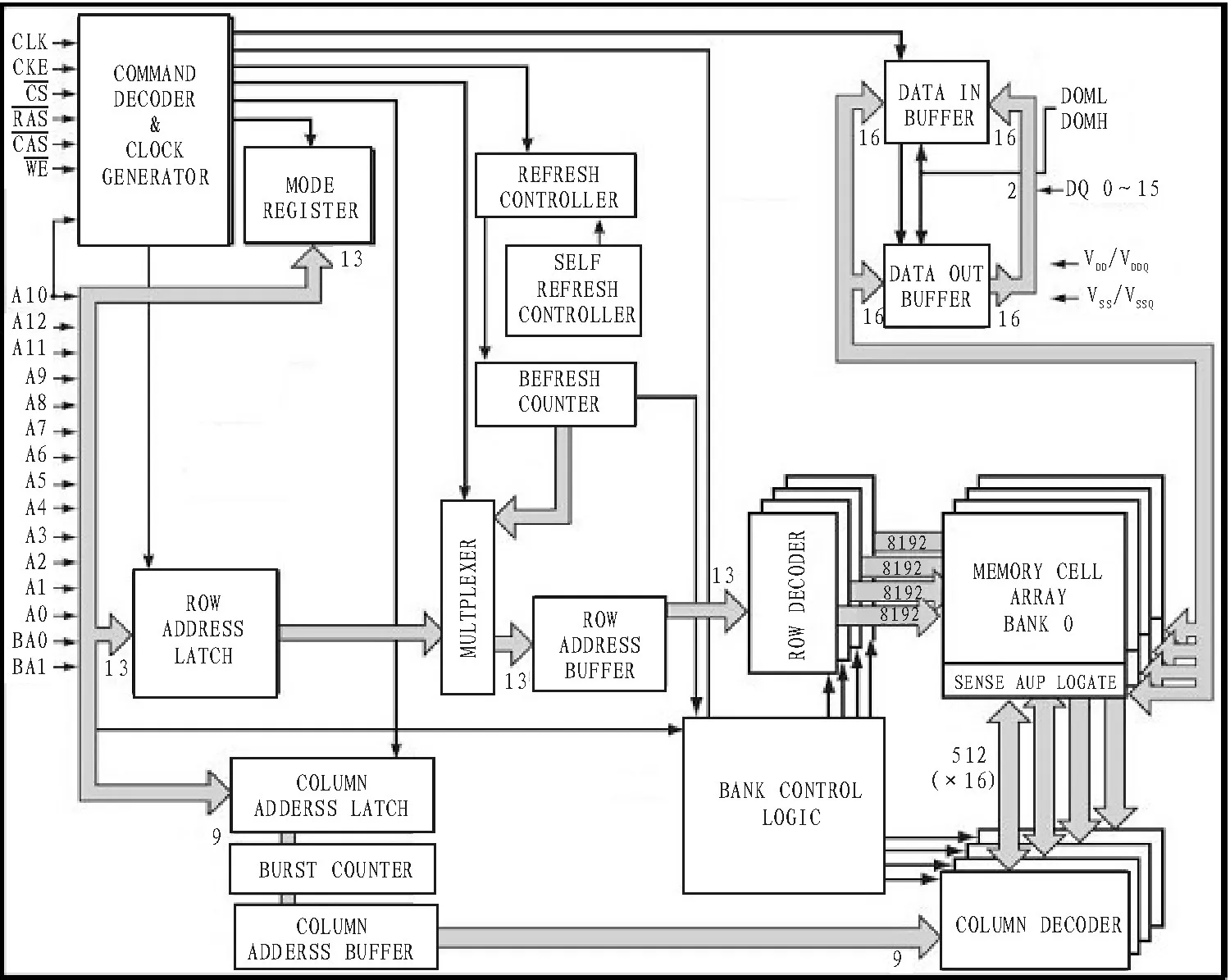

1.1 SDRAM芯片結(jié)構(gòu)

文中采用ELPIDA公司EDS5116ABTA芯片,存儲容量是256 Mbit,數(shù)據(jù)位寬16位,最大工作時鐘為143 MHz,自動刷新周期要求為8 192(周期)/64 ms。圖1為該款SDRAM的結(jié)構(gòu)圖。在上圖結(jié)構(gòu)中,SDRAM是由內(nèi)部的4個BANK構(gòu)成,每個BANK有8 192行,每行各有8 192 bit數(shù)據(jù)位,稱之為“一頁”,按照需求每個存儲單元為16 bit位深,則每行有512列。SDRAM芯片的主要引腳如下:1)A0~A12:復(fù)用地址選擇線,A0~A12是行地址選擇線,A0~A9是列地址選擇線;2)BA0~BA1:BANK 地址選擇線;3)DQ0~DQ7:雙向數(shù)據(jù)端口;4)CLK:系統(tǒng)時鐘輸入端口;5)CKE:時鐘信號使能端口;6)CS:片選信號端口;7)CAS:列地址選通脈沖控制;8)RAS:行地址選通脈沖控制;9)DQ:數(shù)據(jù)掩碼端口;10)WE:讀寫使能控制端口。

相比其他存儲器件,SDRAM特點如下:

圖1 SDRAM結(jié)構(gòu)圖

1)為防止SDRAM中的數(shù)據(jù)丟失,需要定時執(zhí)行刷新操作。

2)SDRAM在上電工作時,需要首先進行配置模式寄存器操作,該操作規(guī)定了工作參數(shù)以決定當(dāng)前SDRAM工作模式,包括突發(fā)長度(BURST LENGTH),列地址選通脈沖時間延時(CAS LATENCY),操作模式(OPERATING MODE)等[6]。

3)SDRAM端口使用靈活。控制命令由控制端口(CS、CAS、RAS、WE)產(chǎn)生,通過這些端口的時鐘上升沿狀態(tài)決定控制命令。SDRAM行地址線與列地址線復(fù)用,取決于當(dāng)前控制命令的不同,按照先行激活后列選取的順序完成一次讀或?qū)懖僮鱗7]。

1.2 控制

SDRAM的所有操作同步于系統(tǒng)時鐘,根據(jù)時鐘上升沿的控制端口和地址端口狀態(tài),可產(chǎn)生多種輸入命令[8]:1)模式寄存器設(shè)置(MSR);2)預(yù)充電所選BANK(PRE)3)行激活(ACT);4)突發(fā)讀指令,突發(fā)寫指令;5)帶自動預(yù)充電的突發(fā)讀/寫指令;6)自我刷新(SELF);7)自動刷新(REF)8)突發(fā)終止(BST);9)空操作(NOP)。

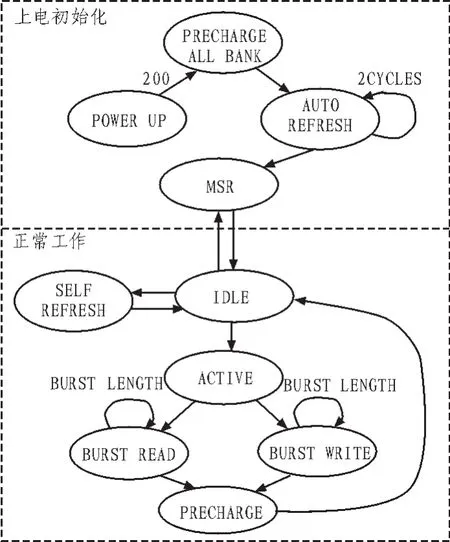

圖2 SDRAM控制器狀態(tài)機

根據(jù)SDRAM控制器的功能設(shè)計其狀態(tài)機如圖2,共包含10個狀態(tài),分為兩個子部分,上電初始化部分和正常工作部分。上電初始化包括從上電到配置模式寄存器4個狀態(tài)機;正常工作包括空閑狀態(tài)、行激活狀態(tài)、突發(fā)讀、突發(fā)寫、預(yù)充電等6個狀態(tài)機。

1.3 SDRAM時序邏輯

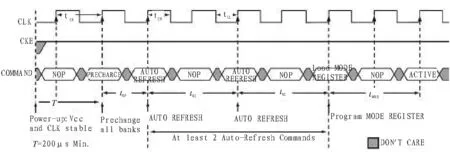

1.3.1 SDRAM初始化與自動刷新

首先,SDRAM在所有引腳同時加電后,需要等待200μs進行上電初始化的穩(wěn)定過程;然后發(fā)出預(yù)充電命令(PRECHIARGE),等待tRP時間完成對所有邏輯BANK的預(yù)充電操作;然后發(fā)出至少8個自動刷新命令(AUTO REFRESH),相鄰的兩個自動刷新命令需要時間間隔tRP;最后,發(fā)出模式寄存器設(shè)置命令(LOAD MODE REGISTER)配置工作模式,此階段需要tMRD時間[9]。

初始化完成后,SDRAM處于空閑(IDLE)狀態(tài),為了防止數(shù)據(jù)掉電丟失,在SDRAM工作時需要定時對SDRAM執(zhí)行自動刷新操作,其要求是需要每64 ms對所有BANK內(nèi)的所有行完成一輪刷新操作,所以每行數(shù)據(jù)的刷新間隔為64 ms/8 192=7.812 5 μs,因此在SDRAM工作狀態(tài)下,每隔最多7.812 5 μs需要發(fā)出一個自動刷新指令[10]。時序圖如圖3所示。

圖3 SDRAM控制器初始化時序

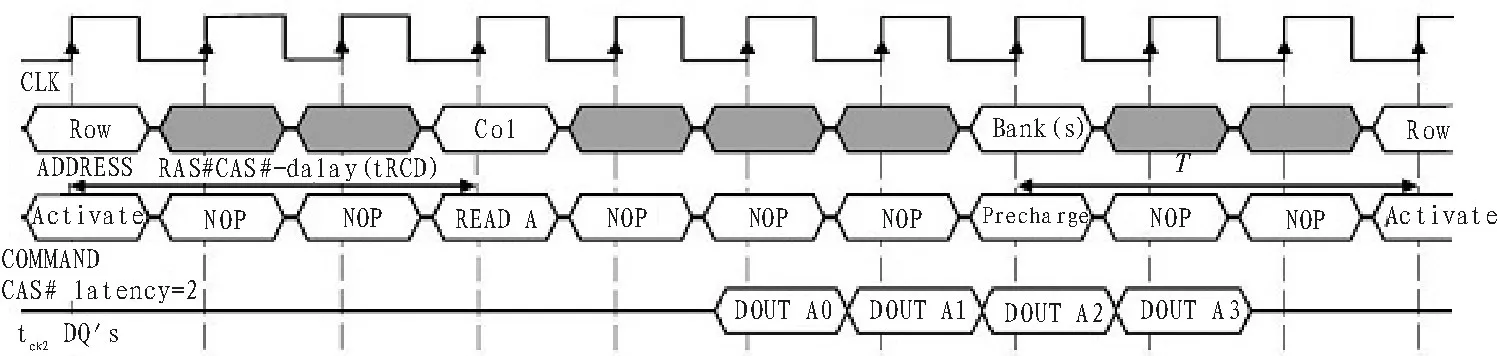

1.3.2 SDRAM突發(fā)讀操作

SDRAM處于空閑(IDLE)狀態(tài)下,可發(fā)出一系列指令組合完成對SDRAM的讀寫操作,這些指令需要在控制端口和地址線的配合下共同完成[11]。先分析突發(fā)讀操作的時序,首先發(fā)出行激活(ACTIVE)指令,由BANK地址(BA0,BA1)和行地址(A0~A12)共同選定需要讀寫的行進行激活。行激活命令發(fā)出后需要等待tRCD時間(RAS to CAS DELAY),才能發(fā)出讀指令與列地址。經(jīng)過tCL(CAS LATENCY)個時鐘周期后,讀出的數(shù)據(jù)出現(xiàn)在數(shù)據(jù)總線DQ上,讀出數(shù)據(jù)的多少由BL(BURST LENGTH)決定,一般為1、2、4、8或全頁突發(fā)模式。突發(fā)讀操作的讀命令操作完成后,需要發(fā)出預(yù)充電命令,以關(guān)閉當(dāng)前激活的行,等待tRP時間后(預(yù)充電到行激活間隔),再執(zhí)行下一個操作。SDRAM控制器突發(fā)讀的時序如圖4所示。

圖4 SDRAM控制器突發(fā)讀時序

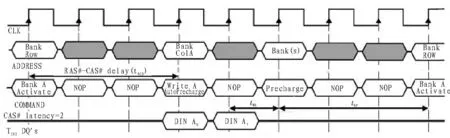

1.3.3 SDRAM突發(fā)寫操作

相比較于SDRAM控制器讀操作的時序,其突發(fā)寫操作的時序稍有不同。當(dāng)檢測到突發(fā)寫命令時,首先執(zhí)行行激活指令以激活指定BANK的指定行,等待tRCD時間后,從地址線讀取列起始地址,同時將數(shù)據(jù)寫到數(shù)據(jù)總線DQ上,執(zhí)行BL個周期的寫操作后,延遲tWR時間(tWR為寫操作延時,將數(shù)據(jù)寫入所用時間)需發(fā)出預(yù)充電命令,以關(guān)閉當(dāng)前激活的行,等待tRP時間后可執(zhí)行下一個操作[12]。SDRAM控制器突發(fā)寫的時序如圖5所示。

2 SDRAM控制器系統(tǒng)設(shè)計

SDRAM控制器的系統(tǒng)模塊設(shè)計如圖6所示。圖中控制器左側(cè)的端口信號與FPGA的系統(tǒng)控制接口相連,用以對控制器發(fā)出讀寫等控制命令、地址信息與數(shù)據(jù)信息等;控制器右側(cè)與SDRAM芯片對應(yīng)端口相連,用于控制SDRAM工作;圖中控制器內(nèi)部為各系統(tǒng)各個模塊結(jié)構(gòu),包括系統(tǒng)接口模塊(Sys_interface)、命令模塊(Command)、控制接口模塊(Ctrl_interface)與數(shù)據(jù)選通模塊(Data_path)。各個模塊功能如下:系統(tǒng)接口模塊用于接收FPGA系統(tǒng)傳遞的操作信號,并將其轉(zhuǎn)換為控制命令(CMD命令碼);命令模塊用于解析CMD命令,并解碼成為相應(yīng)的SDRAM控制指令;控制接口模塊用于解析SDRAM控制指令,轉(zhuǎn)化為SDRAM能夠識別的端口電平組合;數(shù)據(jù)選通模塊用于控制數(shù)據(jù)線的選通情況,完成有效的輸入輸出功能。

圖5 SDRAM控制器突發(fā)寫時序

圖6 SDRAM控制器系統(tǒng)結(jié)構(gòu)圖

2.1 系統(tǒng)接口模塊

系統(tǒng)接口模塊(Sys_interface)包含SDRAM與控制器的上電初始化功能,使兩者處于相同的工作模式下。其控制流程如下:檢測到上電后,首先啟動Count_200計數(shù)器執(zhí)行200 μs的計數(shù)操作以等待器件的穩(wěn)定;之后執(zhí)行初始化配置操作:發(fā)出PRECHARGE_ALL指令預(yù)充電所有BANK,然后執(zhí)行2組自動刷新指令;最后發(fā)出配置模式寄存器指令,以配置SDRAM的工作模式。由于上電后SDRAM工作模式是不定的,所以應(yīng)當(dāng)在使用之前配置模式寄存器[9]。之后通過地址線[A0:A10]發(fā)送模式寄存器配置數(shù)據(jù)。

完成以上配置后,系統(tǒng)指令分析機制才可以接收并分析系統(tǒng)的讀寫信號和地址信息,以及命令模塊的反饋信號CMD_ACK,產(chǎn)生對應(yīng)的CMD命令碼和ADDR地址信息并傳遞給命令模塊[13]。此外該模塊同時將當(dāng)前SDRAM的工作狀態(tài)反饋給系統(tǒng)用戶,標(biāo)明當(dāng)前SDRAM占用情況。

2.2 命令模塊

命令模塊(Command)將解析系統(tǒng)接口模塊傳來的CMD命令碼,并輸出相應(yīng)的SDRAM作指令。例如,當(dāng)CMD命令碼為3’b000時,則輸出NOP指令,表示執(zhí)行空操作;當(dāng)CMD命令碼為3’b001時,輸出READA指令。表示執(zhí)行自動預(yù)充電讀操作。命令模塊同一時刻只能允許一個命令碼和對應(yīng)操作指令有效[14]。

2.3 控制接口模塊

控制接口模塊(Ctrl_interface)用來處理將命令模塊解析出來的CMD命令碼,根據(jù)不同CMD命令碼做出相應(yīng)的端口電平變化操作,以控制SDRAM完成特定功能。例如,若當(dāng)前操作命令為行激活(ACTIVE)操 作 ,則 令 SDRAM_CKE=1,SDRAM_CS_N=0,SDRAM_RAS_N=0,SDRAM_CAS_N=1,SDRAM_WE=1_N,同時通過SDRAM_BA和SDRAM_SA選定要激活的BANK地址與行地址,如此SDRAM器件根據(jù)其引腳特性便激活指定行,應(yīng)當(dāng)注意的是,在此例的行激活命令中,SDRAM_DQ與SDRAM_DQM的端口電平取值對操作沒有影響,只有在讀出寫入時數(shù)據(jù)位才有效[15]。此外控制接口模塊也發(fā)出數(shù)據(jù)使能控制信號DATA_EN對數(shù)據(jù)選通模塊進行控制。

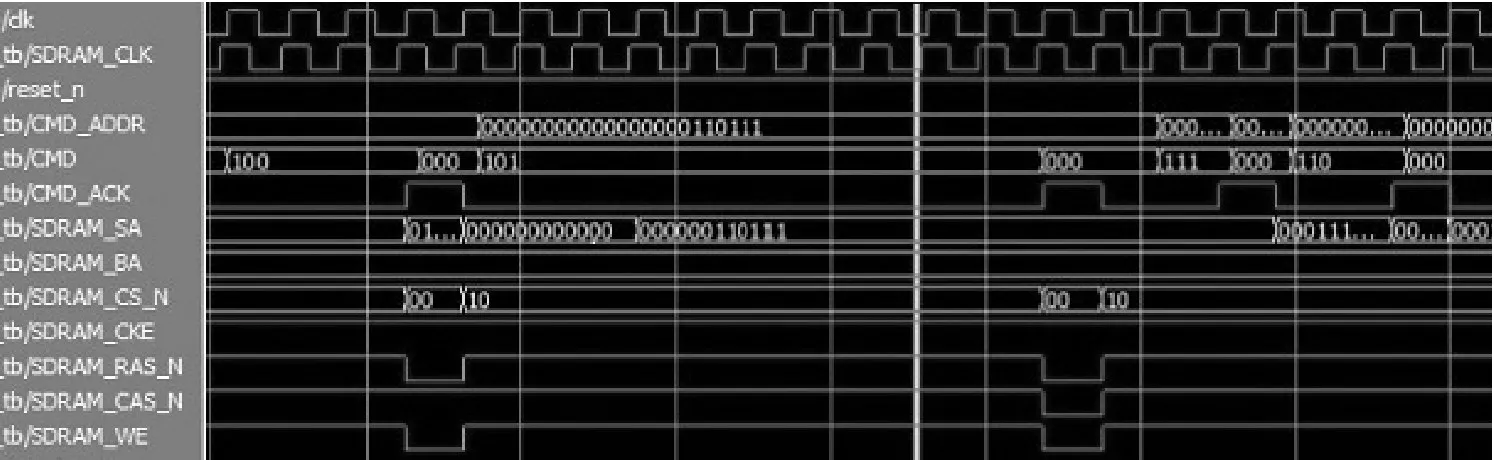

圖7 初始化與加載模式寄存器仿真波形

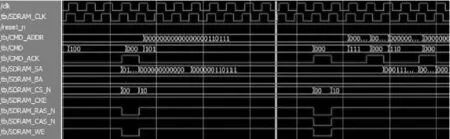

圖8 突發(fā)讀與突發(fā)寫仿真波形

2.4 數(shù)據(jù)選通模塊

此模塊接收接口控制模塊發(fā)出的DATA_EN信號,控制數(shù)據(jù)的讀出或是寫入。當(dāng)信號DATA_EN=1,數(shù)據(jù)線DQ寫使能,允許數(shù)據(jù)寫入SDRAM;當(dāng)信號DATA_EN=0,數(shù)據(jù)線DQ讀使能,允許讀出SDRAM中的數(shù)據(jù)。通過DATA_EN與數(shù)據(jù)選通模塊的控制,能夠使數(shù)據(jù)的讀出、寫入操作在操作指令上達到時序同步[16]。

3 系統(tǒng)仿真與驗證

本文采用硬件描述語言Verilog HDL對系統(tǒng)進行設(shè)計輸入,使用ISE14.6作為系統(tǒng)編譯工具,建立了SDRAM控制器的RTL級(寄存器傳輸級)模型,并使用第三方工具Modelsim10.1c進行仿真驗證。經(jīng)過ISE14.6綜合后,得到其資源占用率為4%;仿真采用32 MHz時鐘作為SDRAM控制器工作時鐘,低于其最大工作時鐘143 MHz,所以滿足其實時性要求。

下面為SDRAM控制器仿真波形圖。圖7為初始化波形,圖8為突發(fā)寫和突發(fā)讀波形。

從圖7、圖8可看出,在初始化過程中,控制器先后執(zhí)行了等待200 μs初始化穩(wěn)定過程、預(yù)充電操作、2個自刷新周期操作和模式寄存器設(shè)置操作。在突發(fā)寫過程中,先后執(zhí)行了行激活、行列有效延時、寫操作(突發(fā)長度為8)。在突發(fā)讀過程中,先后執(zhí)行了行激活、行列有效延時、讀操作(突發(fā)長度為8)。系統(tǒng)的仿真結(jié)果與預(yù)期時序相符合,端口的電平變化與狀態(tài)轉(zhuǎn)換均有效工作,正確的完成了SDRAM控制器的控制功能。

4 結(jié)論

本文提出的用于圖像壓縮系統(tǒng)的精簡SDRAM控制器針對其應(yīng)用場景做了精簡處理,采用典型精簡狀態(tài)機進行控制,并且控制其資源占用情況,具有高效性、高穩(wěn)定性和通用性,滿足星載平臺圖像處理系統(tǒng)的要求,為以后遙測圖像的采集、處理和傳輸提供了技術(shù)支持。

[1]黃云翔.DDR3 SDRAM控制器的設(shè)計和驗證[D].廣州:華南理工大學(xué),2012.

[2]李圣.DDR2 SDRAM控制器的研究與實現(xiàn)[D].西安:西安電子科技大學(xué),2011.

[3]鐘觀水.基于FPGA的高速數(shù)據(jù)采集系統(tǒng)設(shè)計[D].南京:南京大學(xué),2013.

[4]趙樂.基于FPGA的高速實時數(shù)據(jù)采集存儲系統(tǒng)的設(shè)計[D].武漢:武漢理工大學(xué),2012.

[5]陳雨,陳科,安濤.高速圖像處理系統(tǒng)中DDR2-SDRAM接口的設(shè)計[J].現(xiàn)代電子技術(shù),2011,34(12):104-107.

[6]徐永剛.基于FPGA與DDR2-SDRAM的高速數(shù)據(jù)緩沖器的設(shè)計與實現(xiàn)[D].南京:南京郵電大學(xué),2012.

[7]司孝平.基于SDRAM的FPGA實時圖像采集系統(tǒng)的設(shè)計[J].西南大學(xué)學(xué)報自然科學(xué)版,2011,33(1):128-132.

[8]張剛,賈建超,趙龍.基于FPGA的DDR3 SDRAM控制器設(shè)計及實現(xiàn)[J].電子科技,2014,27(1):70-73.

[9]侯宏錄,張文芳.基于FPGA的SDRAM控制器設(shè)計方案[J].兵工自動化,2012,31(2):57-60.

[10]仵宗欽,王曉曼,劉鵬,等.基于FPGA的SDRAM控制器設(shè)計與實現(xiàn)[J].電子與封裝,2014(10):20-24.

[11]孟曉東.基于FPGA的DDR3控制器設(shè)計與驗證[D].長沙:國防科學(xué)技術(shù)大學(xué),2012.

[12]高群福,陳星,程越.基于FPGA的DDR SDRAM控制器設(shè)計與實現(xiàn)[J].電子測量技術(shù),2011,34(8):56-59.

[13]朱文斌,劉春平,黃振.基于FPGA的高可靠性SDRAM控制器設(shè)計與實現(xiàn)[J].電訊技術(shù),2011,51(10):113-116.

[14]武震,郎維燕.基于FPGA的SDRAM控制器的設(shè)計與實現(xiàn)[J].北華航天工業(yè)學(xué)院學(xué)報,2012,22(5):10-13.

[15]鄧耀華,劉桂雄,吳黎明.高速SDRAM控制器的嵌入式設(shè)計[J].計算機工程,2010,36(16):216-218.

[16]王艷春,祖靜,崔春生.基于FPGA的SDRAM的控制器實現(xiàn)與性能分析[J].電子測試,2010(12):44-46.