基于Open VPX的數字陣列雷達信號處理平臺設計

劉文佳 徐光輝 陳業偉

摘要 本文設計了一種基于OpenVPX的數字陣列雷達信號處理平臺,并在基于此平臺提出了具有擴展性的雷達數字處理算法工程實現方法。

【關鍵詞】ADC DBF雷達信號處理 Open VPX

現代戰場環境下,雷達體制日益多樣化,與傳統的模擬相控陣雷達相比,數字陣列雷達具有動態范圍大、多波束調度靈活、抗干擾能力強、易實現寬帶寬角掃描、結構體積更緊湊等諸多優點。

一般模擬相控陣雷達只有和通道、方位差通道、俯仰差通道三路接收通道,而數字陣列雷達則有大量接收通道,要求數字處理系統擁有多通道ADC采樣以及數字下變頻的能力。另外多個接收通道經過數字波束形成處理后需要進行同時多波束處理,信號處理運算量是傳統單波束雷達的數倍。基于VPX標準的信號處理平臺具備強大的信號處理、數據處理能力,以及I/O能力和高性能網絡交換能力,適用于數字陣列雷達。

1 0pen VPX概述

Open VPX( VITA65)是在VPX( VITA46)的基礎上,專門針對軍用、航天等高可靠應用領域的行業標準,由美國國防部組織28家大公司聯合制定,于2010年初發布。該標準是目前最新、最先進的專業技術標準之一,也是面向軍工、航天的高性能、高可靠的計算機體系標準。Open VPX總線標準提高了背板帶寬、集成了更多的I/O、拓展了格式布局更適用于數字陣列雷達信號處理的高密度運算和大寬帶數據傳輸。

2 陣列雷達信號處理系統功能

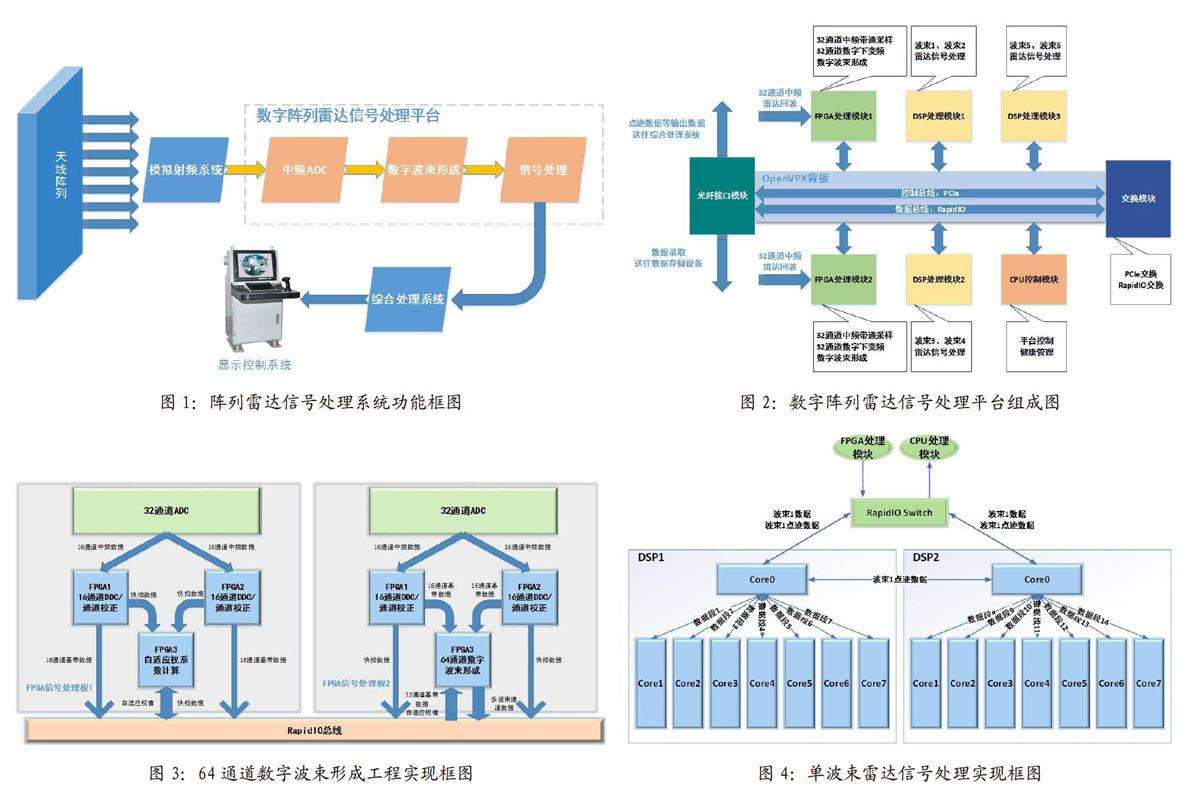

如圖1所示,整個數字陣列雷達分為天線陣列、模擬射頻系統、數字陣列雷達信號處理平臺、綜合處理系統、顯示控制系統組成。本文介紹的數字陣列雷達信號處理平臺實現了從中頻回波數據輸入到目標點跡輸出的數字處理功能。具體包括中頻ADC、數字波束形成和雷達信號處理三大功能。

3 平臺設計

3.1 整體方案

數字陣列雷達信號處理平臺為基于OpenVPX的6U組合。如圖2所示,平臺以RapidIO總線為數據通路,PCIe總線為控制通路,串接了多種功能模塊。整個平臺有5種VPX模塊,其中FPGA處理模塊和DSP處理模塊為平臺主要的處理節點,承擔著從中頻采樣到信號處理的所有運算處理任務;CPU控制模塊為平臺的控制中心;數字信號的輸出由光纖接口模塊負責。

數字陣列雷達信號處理平臺處理流程如下:中頻雷達回波從FPGA處理模塊輸入,信號的帶通采樣、數字下變頻處理由此類型模塊負責。另外,通過Rapid 10總線進行數據交換,多個FPGA處理模塊協同工作,完成數字波束形成功能。數字波束形成處理后產生多個波束,分別送往各個DSP處理模塊進行后續包括脈沖壓縮、雜波圖處理、恒虛警檢測等雷達信號處理功能。每個DSP處理模塊可處理兩個和差波束,各個DSP處理模塊并行處理,處理結果送往光纖接口模塊進行數據匯總和打包。

3.2 FPGA處理模塊

FPGA處理模塊用于高速實時計算,具備高速的互聯接口以及強大的計算能力,滿足VPX全交換結構協議規范。FPGA處理模塊是一種標準6U板卡,以三片高性能FPGA為處理核心,板載大容量QDR SRAM,適合于多種高速信號采集與處理、高速總線接口相關的嵌入式計算應用。FPGA選用FFVA1517封裝XILINX Kintex UltraScale器件,根據需求可選配相同封裝不同規格FPGA。

為了提高平臺集成度,使平臺支持更多通道中頻回波輸入,每個FPGA處理模塊支持安裝一塊雙寬FMC ADC子卡,每個ADC子卡支持32通道ADC,最高轉換速率為125MSPS,分辨率為16bits。雙寬尺寸的FMC子卡寬度為13 9mm,可擺放器件的長度不超過80mm。在如此緊湊的空間內實現32通道的ADC,必須選用更小的ADC芯片。平臺內的雙寬ADC子卡板載8片支持JESD204B接口的4通道ADC芯片,采用JESD204B的ADC芯片由于采用了高速串行總線進行數據輸出,芯片管腳較少,與傳統ADC芯片相比體積跟小。

圖3是基于FPGA處理模塊的64通道數字波束形成工程實現框圖。整個處理流程使用了兩個FPGA處理模塊。每個FPGA處理模式上的雙寬FMC ADC子卡實現32通道中頻采樣,與ADC子卡通過JESD204B接口連接的兩個FPGA分別實現16通道的數字下變頻運算和16通道的通道校正運算。FPGA處理模塊1的第三片FPGA用于自適應權系數計算,FPGA處理模塊2的第三片FPGA則進行64通道數字波束形成處理,并把合成后的波束數據送往DSP處理模塊。兩個模塊之間的通信采用Rapid IO協議。

3.3 DSP處理模塊

DSP處理模塊硬件框圖如圖4。板載4片TI TMS320C6678八核DSP處理器,4片TMS320C6678的理論處理能力為640GFLOPS;每片DSP外擴8GB DDR3SDRAM內存。4片DSP通過Rapid IO交換芯片實現數據互聯;通過PCIe交換芯片實現控制信號互聯。

雷達探測距離內一個完整脈沖回波的數據在FPGA處理模塊中打包通過Rapid IO數據鏈路送往DSP。回波數據包容量是根據雷達工作狀態時變的,當雷達波束探測遠距離目標時,回波數據容量十分可觀;而雷達處于跟蹤近距離目標時,回波數據包雖然容量小,但發送頻率較高。為了兼容雷達不同工作方式,且充分利用硬件資源,DSP處理模塊采用數據分段處理的方式。如圖4所示,每兩片DSP芯片實現單波束雷達信號處理功能。輸入雷達回波數據分別送往DSP1和DSP2的核O。DSP1核O僅接收數據包的前半部分;DSP2核O僅接收數據包的后半部分。兩片DSP的核O負責把收到的數據分別等分為7個數據段送往核1到核7。每片DSP的核l到核7運行相同的雷達信號處理程序,處理結果送往各自核O匯總。兩片DSP的核O通過Hyperlink接口進行互聯,最終形成波束1的點跡數據。

4 結束語

此基于Open VPX的數字陣列雷達信號處理平臺基于通用化、標準化、模塊化思想設計。多種高速信號處理模塊、交換模塊、電源模塊,基于全交換技術實現機箱內系統互聯以實現對信號處理系統硬件的快速搭建;提供對高速信號處理模塊的圖形化、模型化開發工具和基礎算法庫,提供顯示控制模塊的腳本化開發工具以對信號處理系統邏輯和軟件的高效開發。基于此平臺的雷達數字處理算法具有良好的擴展性,例如圖4所示的基于DSP模塊的雷達信號處理算法架構可以基本程序結構不改變的前提下調整為采用更多的DSP芯片處理單一波束回波數據,以增加處理速度或者增加處理算法。

參考文獻

[1]ANSI/VITA 65-2010 0penVPXTM SystemSpecification

[2]陳伯孝.現代雷達系統分析與設計[M].西安電子科技大學出版社,2012.

[3]王繼安,高速高精度ADC集成電路的研究與設計[D].電子科技大學,2009.