基于FPGA的高速采樣及處理裝置設計

趙紫旋,趙曉宇

?

基于FPGA的高速采樣及處理裝置設計

趙紫旋,趙曉宇

(武漢科技大學, 武漢 430081)

本文介紹了一種基于FPGA的高速數據采樣及處理裝置的設計。分析了高速采樣及處理在大功率變流裝置中的應用背景。介紹了采用FPGA實現高速采樣及處理的優勢以及具體的實現方法,描述了高速數據處理的原理及實現方法。通過Verilog編程完成了相關的功能要求,并在Quartus II環境下實現了功能的仿真驗證。介紹了相關的硬件設計內容,器件選型分析,驅動編寫等。最終通過SignalTap II抓取了在實際硬件上模擬的工作過程,驗證了設計的正確性。

FPGA 高速采樣及處理 Verilog編程 硬件實現

0 引言

隨著電力電子技術的發展,人們對電能變換裝置也提出了新的要求,具體表現為:更高電壓、更大電流、更大功率。受限于器件性能,高電壓大電流設備的故障必須實現快速檢測、快速切除,否則將對設備造成不可逆的損害,帶來很大的經濟損失。這就對系統的保護裝置提出了新的要求。

若想實現快速保護,就必須實現對外部狀態的高速采集與處理。由于大功率電力電子設備現場電磁環境惡劣,要想實現數據的高速采集與處理就必須選用相應的器件和對外部電路進行特殊處理。

本文將從外部電路設計、器件選型原則、高速數據采集及處理、芯片驅動編寫等幾個方面,較全面的對高速數據采樣及處理進行論述,并完成裝置的開發與驗證。

1 數據的高速采集與處理技術要點分析

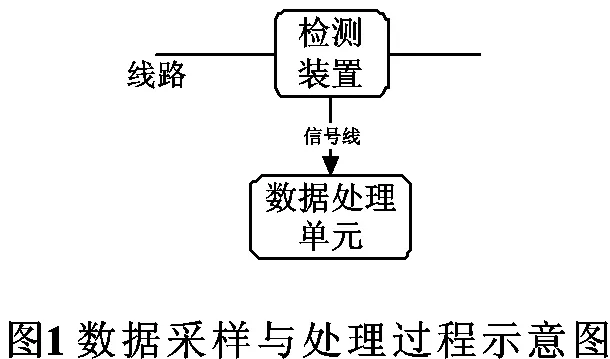

如圖1所述的數據采樣與處理過程示意圖,要想實現數據的高速采集與處理,就必須使檢測裝置、信號線、數據處理單元都能夠滿足相應速度的工作條件。

以常用的電流或電壓傳感器為例,其響應時間就代表著它能夠多快的響應外部激勵,也就決定著其多能實現的最高采樣速度。所以要想獲得有效的高速數據首先要從檢測裝置選型做起。

信號線對信號質量有著重要的影響,尤其在高頻以及惡劣的電磁環境下。所以要選滿足對應頻率、屏蔽條件、阻抗特性的信號線,以保證信號質量,確保數據的正確性。

數據處理單元作為數據處理的終端,要有足夠的處理速度,包括接收速度與處理速度,只有兩者配合才能達到期望的效果。

2 高速采樣及處理裝置總體設計

基于以上分析可知高速數據采樣與處理系統性能主要由檢測裝置、信號線、數據處理單元三部分決定。

由于檢測裝置需要根據不同的檢測對象而變化,所以在本文中將不對其進行進一步的分析。僅以最高采樣速度來表示其性能。信號線雖然很重要,但其并無技術要點需要論述,在此也不進一步展開。

本文將重點對數據處理單元的設計進行詳細論述。

目前數據處理芯片主要有兩種類型,為DSP和FPGA。

DSP優點是開發簡單,片上資源豐富,主頻高,處理速度快。但其程序為順序執行,當有多路高速數據輸入時,有可能造成數據擁擠,無法滿足實時處理要求。而且DSP引腳支持速率普遍較低,且電平標準相對單一,通用性較差。

相比較而言FPGA為并行處理,IO引腳支持的電平豐富,引腳速率可支持G級別。所以在本設計中采用FPGA進行數據處理。

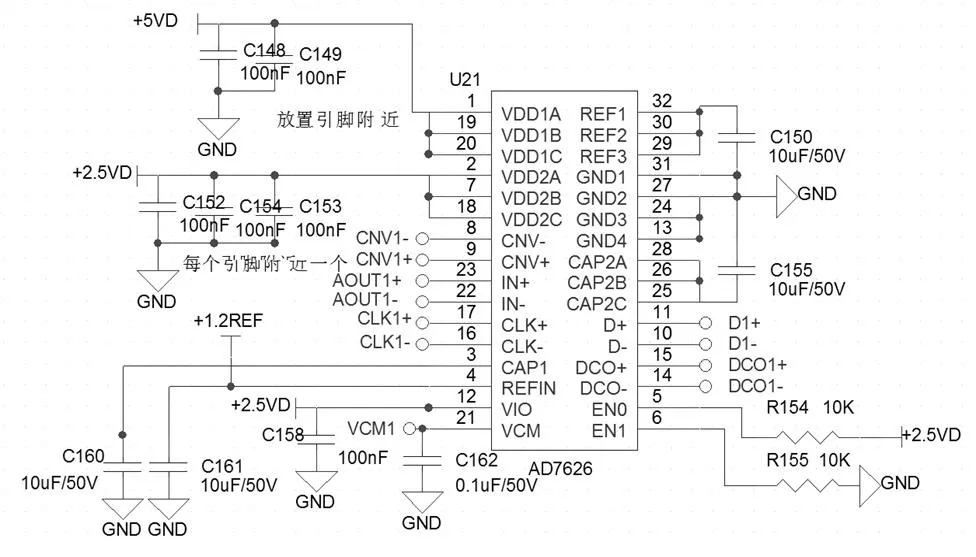

數據采樣需要借助AD芯片,本次設計中選用AD公司的AD7626,其最高采樣速率為10M。其數據輸出和控制輸入均采用LVDS接口,達到高速和抗干擾的目的。

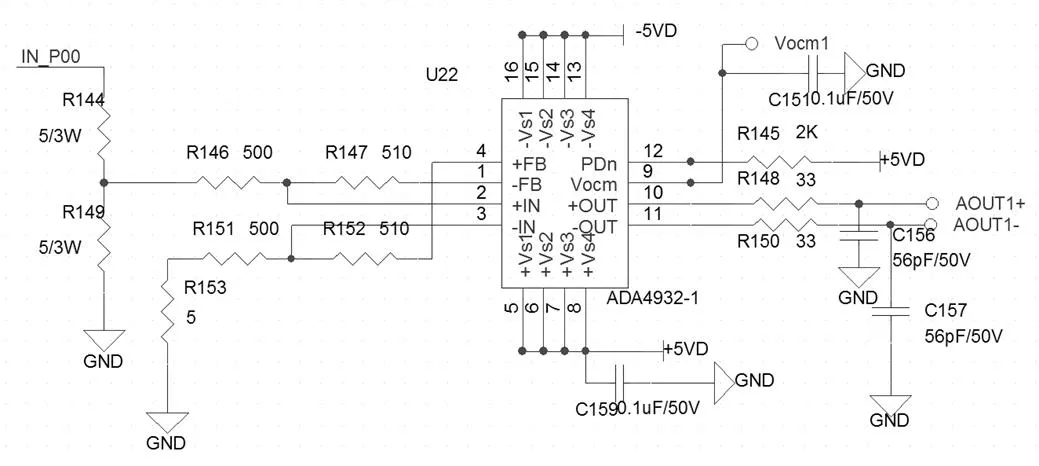

而要想將外部模擬量信號接入AD7626還需要有前端處理電路將其處理成AD7626能接受的信號。在本設計中采用了ADA4932-1作為其前端處理芯片,其主要完成將單端信號轉換成差分,并與AD7606輸入要求相匹配。

圖2 AD7626硬件電路設計

圖3 ADA4932-1硬件電路設計

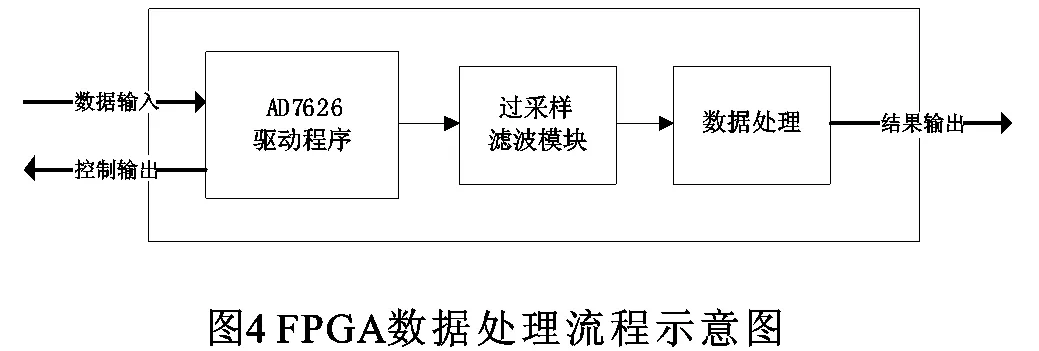

數據處理通過Verilog編程在FPGA中實現,本次設計中采用的FPGA芯片為EP4CE75F23I7。程序流程圖如下所示。

當采樣速率為10 M時,串行輸入數據的速率將達到160 M,所以數據數輸入與控制輸出接口均需要接至FPGA芯片的專用LVDS接口上,并在布線時注意加防干擾措施。

采用過采樣濾波是考慮到由于高頻信號才采樣端不宜設置濾波,所以可通過過采樣取平均值的方式來消除干擾,提高采樣精度。

3 數據處理在FPGA中的實現

要想獲得AD7626的數據首先就要有相應的驅動來完成對其操作。由芯片手冊可得到其時序圖,如下所示。

所以我們需要通過Verilog代碼來實現如上所述的時序邏輯。

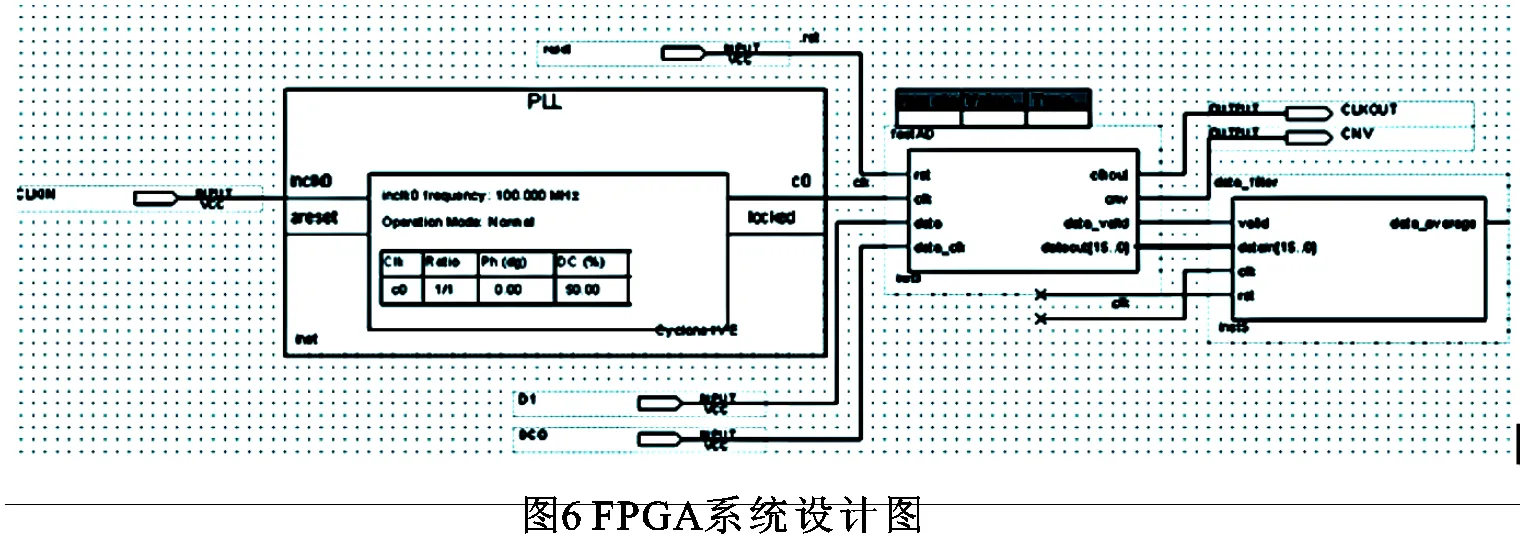

由于數據處理單元跟實際的應用相關,所以在此次設計中就不在對此單元進行設計。如下圖6中所示的FPGA設計中所示:PLL為時鐘單元為各個模塊提供所需時鐘;fastAD單元為高數數據采集單元;data_fliter單元為濾波單元。幾個模塊共同工作最后從data_fliter模塊中得到最終所需數據。

圖5 AD7626時序圖

然后,通過綜合、編譯并下載到電路板上運行。此次過采樣率我們設置為5倍。運行程序,從SignalTap II中觀察程序運行結果。如圖7所示。

從圖中可以看出,其能夠正確的讀出采樣數據,并將每五個數據進行平均處理進行濾波,然后輸出。從而驗證了設計的正確性。

4 結論

本文分析了影響高速數據采樣設計的關鍵因素,對比了DSP與FPGA芯片在這放面的優劣勢,并設計出了一個10M數據采樣處理系統,并驗證了其正確性。這一方面驗證了理論分析的正確性,另一方面也可以為具體的設計工作提供參考。

[1] 關守平, 尤富強, 董國偉. 基于FPGA的高速數據采集系統設計[J]. 控制工程, 2013, 20(05) :970-975

[2] 夏宇聞. Verilog數字系統設計[M].北京:北京航空航天大學出版社, 2007.

[3] 安海磊. 高速數據采集存儲系統設計[D]. 西安電子科技大學, 2012.

[4] Cyclone IV Device Handbook[J]. Altera Corporation.

[5] AD7626 Device Handbook[J]. Analog Device.

Design of High-speed Data Sample and Process Device Based on FPGA

Zhao Zixuan,Zhao Xiaoyu

(Wuhan University of Science and Technology, Wuhan 430081, China)

TM461

A

1003-4862(2018)01-0040-03

2017-10-15

趙紫旋(1997-),女,本科。研究方向:電子信息與應用。