基于自定義協議的機載數據記錄儀控制系統設計

穆蔚然,靳 鴻,張志偉

(中北大學 電子測試技術國家重點實驗室 儀器科學與動態測試教育部重點實驗室,太原 030051)

在飛行器飛行試驗中,機載數據記錄儀作為重要的記錄設備,記錄著飛行器的重要工作環境參數和飛行動態參數。隨著機載數據傳輸速度以及數據量的不斷增加,多通道、大容量、高存儲速度成為現代記錄儀發展的主流趨勢[1-2]。另外各通道之間信號類型的多樣性和功能的復雜性使得整個存儲系統更加龐大,多通道多任務管理復雜。而且機載環境下的存儲設備、測試參數具有實時性強的存儲要求[3]。因此需要一套實時性強、可靠性高的控制系統實現對機載數據記錄儀多通道記錄模塊的統一管理,實現參數高速存儲記錄。

目前數據記錄儀控制系統大多基于Linux、Unix等通用操作系統,與PCI等計算機標準總線接口[4-6]。通用PCI/CPCI、PXI總線標準采用分時復用的工作模式[7-8],同一時刻只允許一個采集終端擁有總線的使用權,所以系統總線的數據傳輸速度取決于當前優先級最高的采集終端,限制了系統整體的存儲速率。操作系統自身的消耗勢必會造成總線數據傳輸帶寬的降低[9]。由于大多通用操作系統多任務非實時響應的特點,當多個任務同時執行時,影響數據總線傳輸和存儲性能[10],雖然具有操作簡單、通用性強和易于實現等優點但難以滿足機載環境下對存儲系統的實時性和可靠性要求。

1 控制系統總體設計

基于自定義協議的機載數據記錄儀控制系統采用非標準總線來實現對各記錄模塊的控制。系統采用STM32F103單片機和FPGA作為主控制器,STM32對接口板卡的RS422指令數據進行解析,FPGA是整個系統指令的管理中心和數據的傳輸媒介,STM32通過配置和讀取FPGA內部的寄存器實現系統各項功能。各通道記錄模塊相互獨立且實時并行記錄。

機載數據記錄儀有上位機控制與1553B總線數據流2種控制模式,采用1553B總線數據流控制模式時,通過機載/地面計算機發送1553B總線數據流控制記錄儀的工作。使用上位機控制模式時,通過上位機控制管理記錄儀的工作,實現存儲數據的上傳。

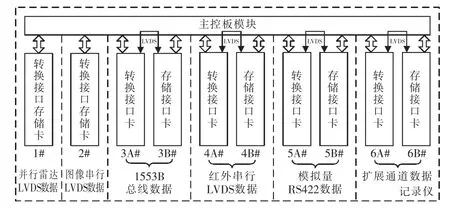

該數據記錄儀采用了按照功能劃分的插卡式模塊化設計結構[11],將LVDS記錄模塊、模擬量記錄模塊、1553B總線記錄模塊、RS422總線記錄模塊進行整合。LVDS傳輸方式實現各通道記錄模塊存儲數據的高速上傳。使用RS422總線實現主控制板卡與各通道記錄模塊之間以及與上位機之間指令的通訊。各子板模塊通過主控板卡連接、控制、傳遞各通道的信號。在主控板卡的控制下,協調統一各子板工作。整個系統具有擴展功能預留擴展插槽,記錄儀總體結構組成示意如圖1所示。

2 控制系統雙模式控制方案設計

圖1 記錄儀總體結構組成示意Fig.1 Recorder overall structure diagram

機載數據記錄儀有上位機與1553B總線數據流2種控制模式,在進入相應的工作模式前,需要在上位機控制模式下通過上位機對記錄儀各通道記錄模塊進行上電配置,選擇相應的控制模式。當記錄儀采用1553B總線數據流控制模式時,通過機載/地面計算機發送1553B總線數據流控制記錄儀的工作,此控制模式適用于機載環境和地面環境;當記錄儀采用上位機控制模式時,通過上位機控制管理記錄儀的工作,并實現存儲數據上傳的功能,此控制模式適用于地面環境。

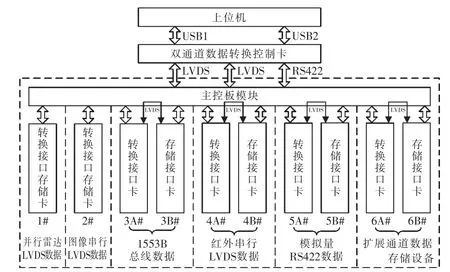

2.1 上位機控制模式設計

上位機控制模式下的系統結構組成示意如圖2所示,上位機通過2個USB接口與雙通道數據轉換控制卡連接,其中USB1接口與芯片CY7C68013進行通信[11],將雙通道數據轉換控制卡讀到的數據回傳給上位機;USB2通過CP2102(RS232)來接收和下發配置和控制指令。發送“下載”命令后,雙通道數據轉換控制卡收到上位機命令后通過RS422接口與主控板卡進行通信;主控板卡收到雙通道數據轉換控制卡轉發的命令后,主控板卡FPGA從子板的存儲單元中讀取數據,通過LVDS接口向雙通道數據轉換控制卡發送數據。雙通道數據轉換控制卡收到數據后會判斷數據是否有效,若有效則將數據寫入緩存,上位機發送讀數請求將緩存中數據存儲至計算機硬盤,進行后續分析處理。

圖2 上位機控制模式下的系統結構組成示意Fig.2 Host computer control mode composition of the system structure

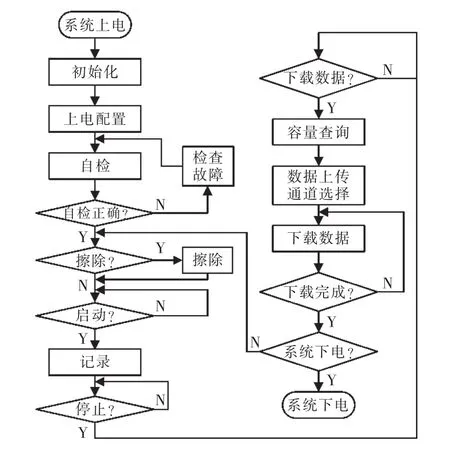

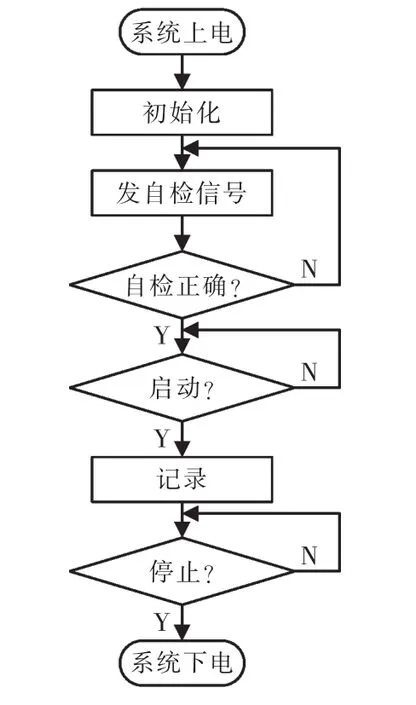

上位機控制模式下的系統工作流程如3所示,連接記錄儀與上位機。通過上位機對記錄儀各通道記錄模塊進行電源配置,配置信息將保存至主控板卡上。上位機操作記錄儀進行自檢,自檢通過則表明初始配置設置正確。如未通過,則需檢查相關配置是否與使用狀態一致。當自檢通過后,主控板卡根據上位機控制指令對子板進行操作。

圖3 上位機控制模式下系統工作流程Fig.3 System workflow under the control mode of host computer

2.2 1553B總線數據流控制模式設計

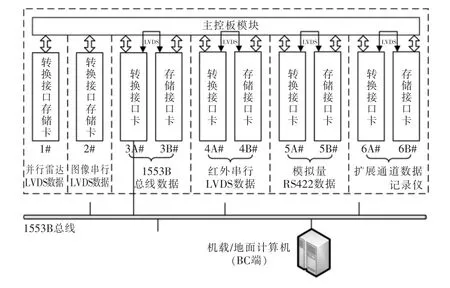

1553B總線數據流控制模式下的系統結構組成示意如圖4所示。1553B接口子板是實現這一控制模式的主要模塊,1553B接口子板主要功能是將1553B消息命令轉換為RS422通訊指令,1553B接口子板接收到機載/地面計算機(BC端)的1553B消息命令后轉換成相應的RS422通訊指令,發送給主控板卡,主控板卡接收到對應的RS422通訊指令后控制記錄儀的工作。

圖4 1553B總線數據流控制模式下的系統結構組成示意Fig.4 Schematic diagram of the system structure under the 1553B bus data flow control mode

1553B總線數據流控制模式下的系統工作流程如圖5所示。數據記錄儀與上位機連接,通過上位機對記錄儀各通道存儲模塊進行電源配置,配置信息將保存至主控板卡上。上位機發送自檢指令,記錄儀進行自檢,若通過則表明初始配置設置正確。自檢通過后連接記錄儀與機載/地面計算機,數據記錄儀進入1553B總線數據流控制模式,主控板卡根據1553B接口子板傳來的控制指令對其余子板卡進行操作。

圖5 1553B總線數據流控制模式下系統工作流程Fig.5 System workflow under 1553B bus data flow control mode

3 控制管理系統通訊協議設計

主控板卡與所有子板卡之間通訊協議采用自定義指令協議實現各板卡之間指令通訊和存儲板卡上記錄數據的下載。

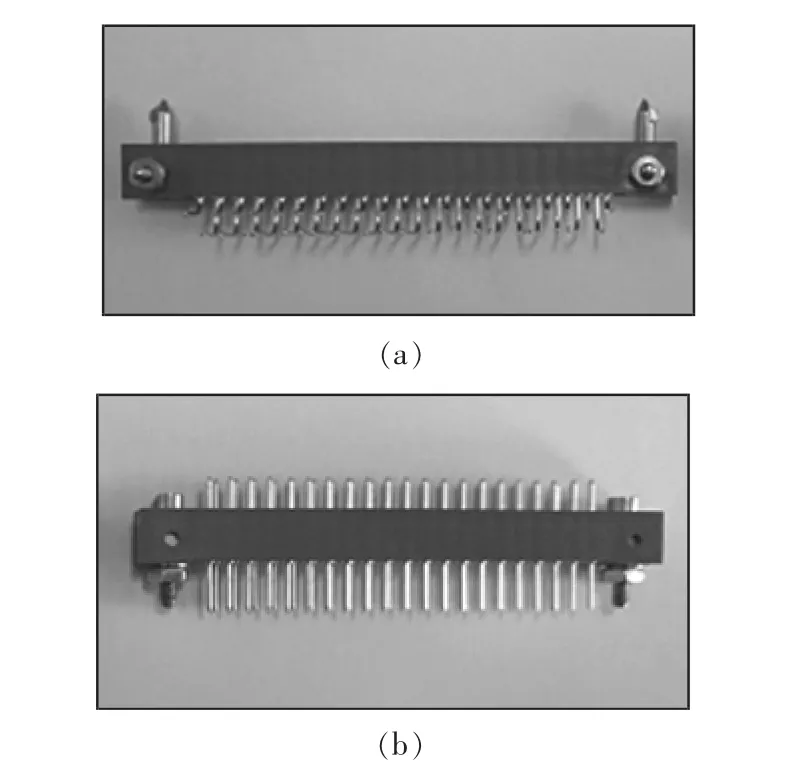

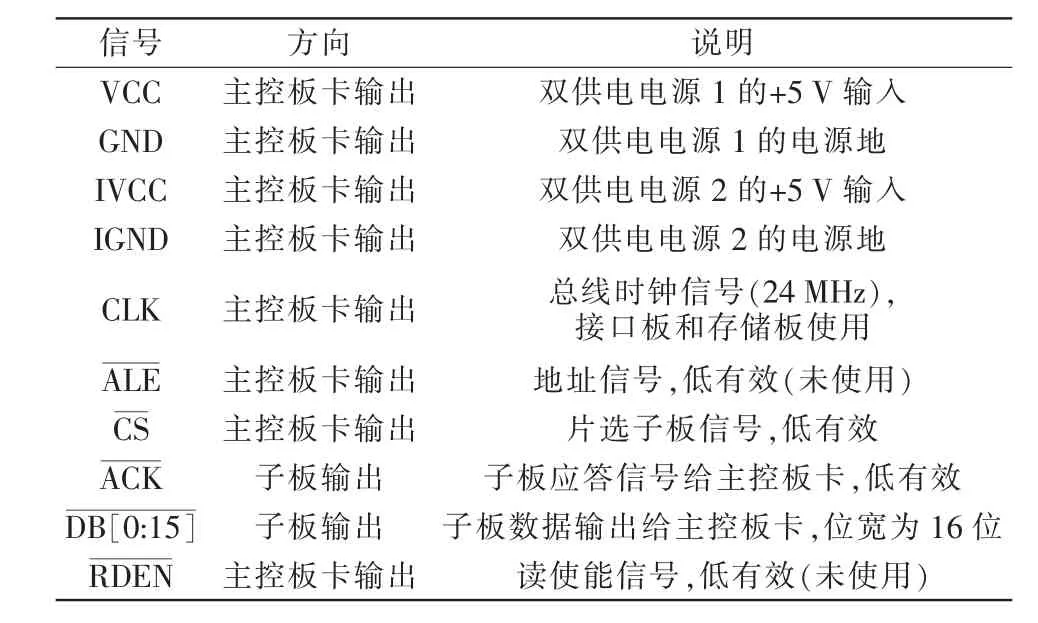

3.1 電氣接口設計

為滿足機載環境要求,主控板卡與子板的連接器件采用J27A-41ZJXⅡBC/BW-0.8航天級接插件。該接插件具有高可靠性和高速傳輸的特點,產品示意如圖6所示。這一系列的電路連接器可用于電子設備、計算機內部印制板之間、印制板與電纜之間、電纜與電纜之間的電路連接。具有插拔力低、接觸可靠性高、支持熱插拔、使用壽命長、耐用等特點。J27A-41TKⅡBW-0.8連接器部分引腳定義信號描述如表1所示。

圖6 接插件產品示意Fig.6 Connector product diagram

表1 部分引腳定義信號描述Tab.1 Part of the pin definition of the signal description

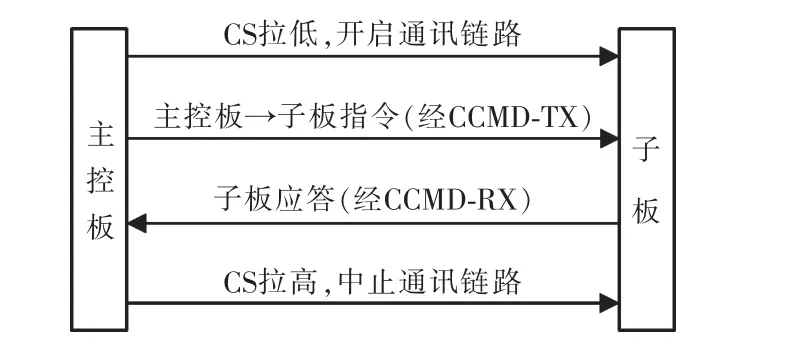

3.2 主控板卡與子板卡之間指令通訊

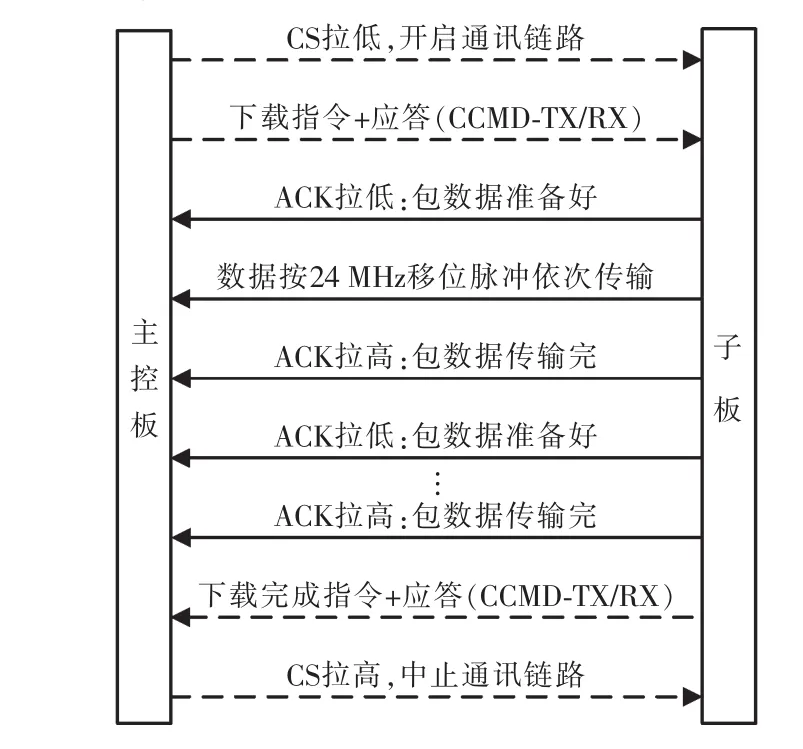

主控板卡與子板之間進行指令傳輸時,主控板卡作為從站子板作為主站。完成主控板卡與子板卡間指令通訊和存儲數據的高速上傳。通訊模式為在CS片選信號下的雙向對等方式傳輸。傳輸過程如圖7所示。

圖7 主控板卡與子板間指令傳輸過程示意Fig.7 Schematic diagram of the instruction transmission between the main control board and the sub board

指令協議的具體格式為

起始符 目標地址 源地址 指令 字節數 DATA數據 校驗和

目標地址和源地址定義方式比較隨機,與各板卡地址相對應即可。字節數表示要發送的數據字節數,范圍為0x00~0xFF。數據指需要發送的數據,該數據大小為字節數所規定的值。校驗即為前面所有數據(START至DATA)異或得到的數值,然后需要將該數值MSB位清零,使其滿足0~7F的要求。

對于各子板而言,RS422指令的有效性需要配合子板接口上的CS片選信號一起使用。在默認情況下,CS片選信號選通1553B接口子板。當有指令需要向其它子板發布時,先用CS片選信號選通指定的子板然后才可以進行通訊。發布指令的通訊任務完成后CS片選信號回歸默認狀態,仍然選通1553B總線子板。

3.3 主控板卡與子板間數據傳輸通訊協議

主控板卡與子板之間數據傳輸的完整過程如圖8所示。

圖8 主控板卡與子板數據傳輸過程示意Fig.8 Schematic diagram of the main control board and the sub board data transmission

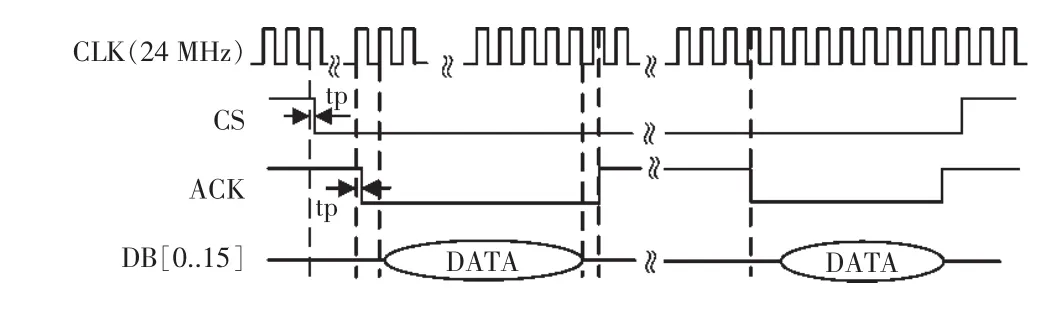

CS、ACK 及 DB[0:15]的變動均與 CLK 時鐘脈沖的上升沿同步,CS電平變化由主控板卡進行控制。ACK 與 DB[0:15]變化由子板進行控制,在 ACK拉低的下一個CLK時鐘移位脈沖上升沿開始數據傳輸。在DB[0:15]總線的DATA傳輸完畢后的下一個CLK時鐘移位脈沖上升沿ACK拉高。對于各存儲子板,數據上傳時,將按幀頭、幀計數、數據字、校驗和、幀尾組成模式進行組幀。數據幀會連續發送,直至下載指令中所要求的數據全部傳送完為止。指令相關的時序如圖9所示。

3.4 1553B接口子板與主控板卡之間通訊協議設計

圖9 指令時序圖Fig.9 Instruction timing diagram

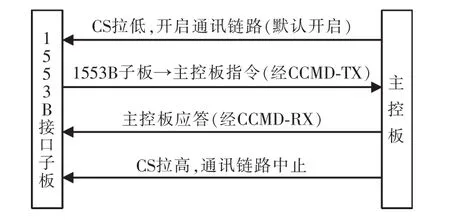

1553B接口板卡與主控板卡之間進行指令傳輸時,1553B板卡作為主站,主控板卡作為從站。

通訊模式為片選信號有效時雙向對等傳輸方式,該操作只有當CS片選信號選定1553B接口子板時指令才有效,默認設置1553B接口板與存儲板插在A號插槽、B號插槽,主控板卡與子板通訊空閑情況下CS信號默認選通1553B接口子板。1553B總線數據流控制下的指令包括自檢、啟動、停止3個指令,其傳輸過程如圖10所示。

圖10 1553B接口子板與主控板卡指令傳輸示意Fig.10 Schematic diagram of the 1553B interface sub board and main control board instruction transmission

4 時序仿真

STM32控制邏輯通過配置和讀取FPGA內部相關的寄存器對目標子板的RS422指令數據包的轉發和接收目標子板的RS422指令應答數據包,實現與子板的指令通訊以及雙控制模式功能。

地面計算機發送 “自檢”指令后,系統進入1553B數據流控制模式的在線仿真圖,如圖11所示,圖中主控板卡STM32首先讀取到1553B接口子板發送的數據包的起始符5A,接著等待接收RS422指令數據包的下一個數據字。

圖11 1553B數據流控制模式在線仿真圖Fig.11 1553B data flow control mode online simulation diagram

上位機或1553B數據流發送“自檢”指令,以子板卡C1為例,主控板卡轉發“自檢”指令的在線仿真如圖12所示。圖12局部放大后,串口發送FIFO寫操作的在線仿真如圖13所示。

圖12 主控板卡轉發“自檢”指令在線仿真圖Fig.12 Online simulation diagram of “self-examination”instruction on the main control board

圖13 串口發送FIFO寫操作的在線仿真圖Fig.13 Online simulation diagram of FIFO write operation by serial port

上位機或1553B數據流發送“自檢”指令后,以子板C1的為例,主控板卡接收C1子板的應答指令的在線仿真如圖14所示。圖14局部放大后,串口接收FIFO寫操作的在線仿真如圖15所示。

圖14 主控板卡接收C1子板應答指令在線仿真圖Fig.14 Online simulation diagram of main control board receiving C1 sub board response instruction

圖15 串口接收FIFO寫操作在線仿真圖Fig.15 Online simulation diagram of FIFO write operation by serial port

5 結語

整個控制系統所有通道記錄模塊實時并行記錄,不需要經過主控板卡控制器干預,具有功能特定、指令精簡、實時性強的優點。

板卡通訊采用的自定義指令協議是完全開放的,凡按照該指令設計的板卡均可兼容此記錄儀,實現功能擴展。控制模式的多樣性和靈活性使得記錄儀適用范圍更加廣泛。若使用其他總線改變控制管理系統控制模式,只需更換1553B接口板卡即可實現。例如:實現CAN總線數據流控制模式,可按照1553B接口子板與主控板卡之間指令通訊協議設計“CAN接口板卡”,插入對應卡槽即可。

控制管理系統工作于復雜的機載環境,系統結構設計按照抗震動、抗沖擊的規范;電路板符合電磁兼容性設計要求;主控板卡與子板接插件選用航空接插件,參照國家軍用標準插件規范,滿足傳輸速率,保證數據傳輸的可靠性。

[1]裴俊杰.基于FPGA的多路數據接收存儲的設計與實現[D].太原:中北大學,2011.

[2]王歡,靳鴻,陳昌鑫,等.模塊化和柔性化的機載數據記錄儀設計[J].工程設計學報,2014,21(4):373-377.

[3]Qin G,Liu G,Feng H.Design and implementation of a solidstate flight data recorder using multichannel technique[C]//IntelligentControland Information Processing (ICICIP),2013 Fourth International Conference on,IEEE,2013:726-729.

[4]吳良.分布式試飛測試總線系統的硬件設計與實現[D].重慶:重慶大學,2008.

[5]劉九洲,杜國興,盛文.基于CPCI總線的雷達便攜式儀器測試系統設計[J].儀表技術,2013(1):4-6.

[6]祖東輝.大容量雷達數據存儲與管理技術研究[D].成都:電子科技大學,2013.

[7]TakeshiSasada,Sato Ichikawa,MasashiShirakura.High-speed 200Gbytes data recorder utilizing the 512Mbits SDRAM and compact PCI bus[C]//22nd AIAA International Communications Satellite Systems Conference&Exhibit 2004(ICSSC).Monterey,California:AIAA,2004:185-189.

[8]劉東華,李秋娜.通用高速數據存儲系統設計與實現[J].遙測遙控,2007,28(1):15-19.

[9]范曉星.高速大容量固態存儲系統設計與實現[D].西安:西安電子科技大學,2014.

[10]任敏.基于FPGA的雙通道的機載數據存儲系統設計[D].太原:中北大學,2015.

[11]吳磊,郭超平,申世濤,等.基于CY7C68013與FPGA的便攜式數據采集系統[J].計算機應用,2012,32(Z1):164-166.