基于FPGA的風電機組振動監測系統設計

龍 磊,鄧艾東

(東南大學火電機組振動國家工程研究中心,江蘇 南京 210096)

0 引言

風力發電機組單機容量向兆瓦級以上的發展,對風力發電設備的可靠性和安全性提出了更高的要求。大型風電機組工作環境惡劣,風機傳動系統故障率高。目前,通常采用定期檢修方式對其進行維護。但由于機組自帶的運行監控設備不足,很難準確掌握風電機組傳動系統的運行狀況。這往往導致系統部件發生損壞時無法及時排除故障,大大降低了設備的利用率[1-2]。振動信號在眾多特征信息中能夠有效判斷風機傳動系統的運行狀態[3-5]。配備完善的振動狀態監測系統,對于及時發現傳動系統故障、合理安排檢修及提高機組的經濟效益具有重要意義。

本文以風機傳動系統為監測對象,設計了一種以ARM為主控制器、FPGA為從控制器的風電機組振動監測系統。利用FPGA對數據的高速處理能力和增強型直接內存存取(enhanced direct menory access,EDMA)的高速數據傳輸能力,解決了風電監測系統對采集數據的實時獲取和保持數據準確性的問題。本文重點介紹了FPGA邏輯控制模塊。

1 系統總體設計方案

本文研究的風機傳動監測系統主要分為兩個部分。第一部分主要實現數據的采集、預處理、傳輸、存儲等功能,包括模擬信號處理、FPGA電路邏輯控制及ARM嵌入式平臺等模塊。第二部分為應用層軟件程序。本系統采用基于TCP/IP的C/S軟件體系結構:整個硬件平臺完成對數據的采集、服務請求和數據時/頻分析;上位機作為客戶端,對采樣速率、周期、點數、通道等參數進行控制;應用層軟件和上位機之間的通信選用TCP/IP通信協議。系統總體框架如圖1所示。

圖1 系統總體框架示意圖

2 系統硬件設計

2.1 模擬信號預處理

本系統將風機傳動系統的振動信號作為監測參數,并行采集傳輸8通道振動信號。系統可支持渦流、速度、加速度3種類型傳感器的接入。每個通道都包括間隙電壓、位移、速度、加速度等信號的調理電路。系統能根據傳感器的類型自動選擇相應的預處理電路[6]。為了提高信噪比,信號采用差分輸入。當采用電渦流傳感器時,信號接入前要進行分壓處理,然后對信號進行差分放大,經低通濾波后獲得間隙直流電壓信號,以判斷渦流傳感器的靜態安裝位置。接入加速度傳感器時,先通過8階抗混疊低通濾波器和2階高通濾波器,獲得加速度信號;再分別通過一次積分和二次積分得到速度和位移信號。每次積分前都需要進行隔直處理,以免發生積分偏置。

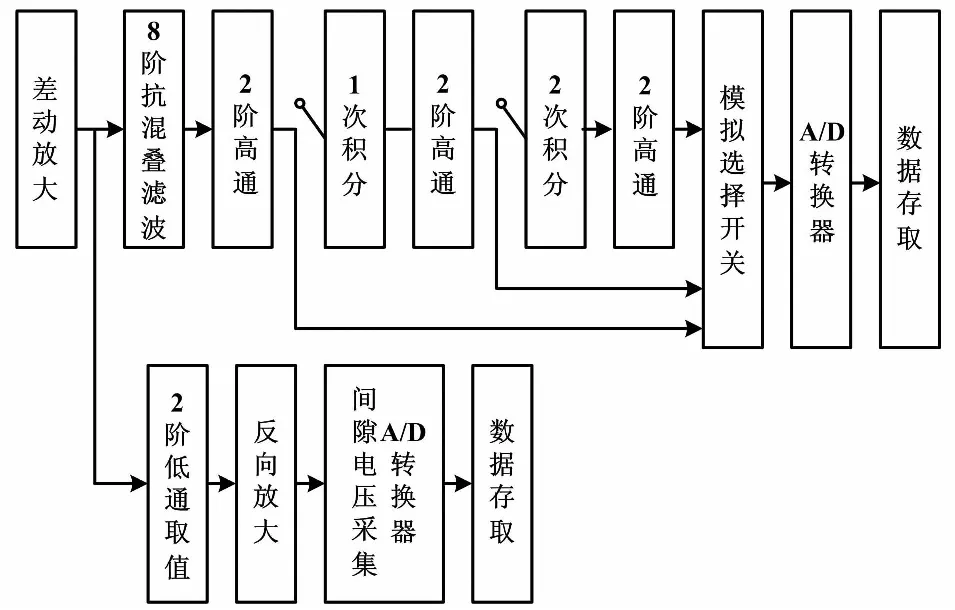

每個通道輸入信號經過預處理后,得到振動加速度、速度和位移信號。信號被接入模擬選擇開關DG409DY-E3。通過FPGA控制模擬選擇開關選擇信號,并將信號送入8通道16位高速A/D轉換器AD7606進行轉換,從而實現了8通道輸入信號的并行采樣。渦流傳感器間隙電壓是慢變信號,采用普通A/D轉換器即可。1個通道的振動信號預處理框圖如圖2所示。

圖2 振動信號預處理框圖

傳動系統低速軸或高速軸的轉速可通過測速齒輪來測量。轉速脈沖接入FPGA進行數字倍頻后,可實現振動信號濾波中心頻率的自跟蹤和振動信號A/D轉換頻率的自適應。

2.2 FPGA模塊設計

圖3 FPGA功能實現框圖

數字鎖相環模塊的主要功能是實現N倍頻,即使輸出信號的頻率Fout是輸入信號Fin的N倍。數字鎖相環是一個相位反饋控制系統,其輸入信號通常為脈沖信號,通過與提取的參考相位比較,使最后得到的分頻與所需的頻率十分接近[8-9]。通過FPGA內部的數字鎖相倍頻器,產生振動信號A/D轉換的觸發信號和抗混疊濾波器Max291的時鐘頻率。將輸入頻率為f的轉速脈沖信號作為數字倍頻器的輸入,通過數字倍頻器自動輸出128f(或其他需要的倍頻)脈沖,并將其作為A/D觸發信號,再由A/D轉換器對8通道振動信號進行同步采樣。由于數字倍頻器能提供滿足精度要求的轉速脈沖倍頻信號,從而保證了精確的整周期采樣。8路采集通道分別采樣1 024點后自動緩存數據,由軟件輸出控制指令,從緩存器讀取采樣數據。同時,將該轉速脈沖信號作為FPGA中另一個數字倍頻器的輸入,并輸出所需的倍頻信號作為濾波器芯片Max291的時鐘頻率,從而實現濾波中心頻率隨轉速頻率變化的自動跟蹤功能。

DAC7512模塊主要實現對FPGA時鐘的分頻、數據的同步讀寫。MCP3208的功能是對采集信號進行A/D轉換。AD7606模塊主要模擬8路信號,并在采樣完成后通過FPGA的控制,將轉換的數字量存儲到RAM緩存中,供上層及時讀取。本系統中,AD7606采用并行數據模式,ncs上升沿將使總線變為高阻態;設模擬輸入為±5 V,轉換時間為4 μs,采集保持時間為 1 μs,最大吞吐速率為200 Kb/s。AD7606的首要任務是設置采樣觸發信號和Max291濾波器時鐘信號。其代碼為如下。

convst<=conv_x when regs_rw(0)(3)=‘1’else cony;

max291_clk(0)<=conv_e when regs_rw(0)(6)=‘1’else max291_clk_i;

max291_clk(1)<=conv_e when regs_rw(0)(6)=‘1’else max291_clk_i;

max291_clk(2)<=conv_e when regs_rw(0)(6)=‘1’else max291_clk_i;

max291_clk(3)<=conv_e when regs_rw(0)(6)=‘1’else max291_clk_i;

本文開展農業資源承載力分析主要運用農林牧漁業總產值、糧食總產量、農林牧漁業總產值、農業用水量、總供水量5個評價指標,其數據主要來源于2002—2017年內蒙古統計年鑒、2010—2016年巴彥淖爾市水資源公報。

max291_clk(4)<=conv_e when regs_rw(0)(6)=‘1’else max291_clk_i;

max291_clk(5)<=conv_e when regs_rw(0)(6)=‘1’else max291_clk_i;

max291_clk(6)<=conv_e when regs_rw(0)(6)=‘1’else max291_clk_i;

max291_clk(7)<=conv_e when regs_rw(0)(6)=‘1’else max291_clk_i;

采樣觸發信號分為外部采樣時鐘信號conv_x和內部采樣時鐘信號con_y。寄存器reg_rw(0)(3)存儲了AD7606采樣信號的具體采樣方式:1代表外部采樣,0代表內部采樣。振動信號采集方式分為有轉速和無轉速兩種,其初始狀態由軟件設置。運行中,系統可以自動、有效判斷轉速信號失效狀態。當有轉速信號時,為防止頻譜泄漏,必須進行周期采樣(連續采樣1 024點),即以外部采樣觸發方式(conv_x)輸出A/D觸發信號并控制數據的存儲。當無轉速或轉速失效時,系統自動從有轉速采集切換到無轉速采集狀態。此時為軟件觸發方式,并由軟件產生A/D轉換觸發信號,由用戶設定采樣頻率,以等時間間隔采集信號。

2.3 ARM與FPGA的數據傳輸

FPGA與通用存儲控制器(general purpose memory controller,GPMC)的連通關系如圖4所示。

圖4 FPGA與GPMC連通關系圖

在本系統中,FPGA與ARM主芯片之間采用EDMA方式進行數據傳輸。EDMA主要用于控制存儲器與存儲器、存儲器與外設、外設與外設之間的數據傳輸。其工作流程為:向CPU發出請求,使控制器獲得總線控制權;CPU繼續執行內部操作,EDMA控制器輔助數據傳輸,數據傳輸完成后向CPU發出中斷信號,并將總線控制權交還給CPU[10]。ARM嵌入式平臺作為本系統的主控單元,其主要功能是完成對A/D采樣的數據讀取,以及實現FPGA與上位機之間的通信。本系統嵌入式平臺選用成都英創的ESM335X系列和開源的嵌入式Linux系統。ESM335X基于ARM Cortex-A8,具有豐富的外設、工業接口、可編程實時單元和工業通信子系統[11]。為實現不同功能,FPGA增設了相應參數寄存器。ARM通過其內部通用存儲控制器GPMC端口實現對FPGA相關寄存器的讀寫,包括FPGA的數據采集速率、倍頻等參數的設置。

3 系統軟件設計

本系統采用C/S體系結構,軟件設計平臺為Linux操作系統,編程軟件為Eclipse IDE for C/C++,選用C語言作為編程語言。系統軟件的主要功能是采集振動信號,實現與上位機的通信,并將數據傳送給上位機。當上位機向應用層軟件發送數據時,應用層軟件對上位機指令進行監測,有利于接收處理信號。應用層軟件與上位機之間采用TCP/IP通信協議,通過Linux中的套接字(Socket)通信。套接字包含3部分:將數據發送到目的端的IP地址、傳輸層協議和數據傳送使用的端口號[12-14]。結合這3個參數,同時綁定一個Socket,就能實現應用層與傳輸層之間的數據通信。具體創建套接字,設置IP地址、協議和端口號的程序代碼如下。

if((listenfd=socket(AF_INET,SOCK_STREAM,0))==

-1)

{

perror(">>>create socket error ");

exit(-2);

}

int opt=SO_REUSEADDR;

setsockopt(listenfd,SOL_SOCKET,SO_REUSEADDR,&opt,sizeof(opt));

//reuse address in bind

bzero(&server,sizeof(server));

server.sin_family=AF_INET;

//Use TCP

server.sin_port=htons(PORT);

server.sin_addr.s_addr=htonl(INADDR_ANY);

采用創建子進程的方式,對上位機指令進行實時監測。應用層總體實現流程如圖5所示。

圖5 應用層總體實現流程圖

4 結束語

本文將振動信號作為監測參數,采用ARM和FPGA作為硬件核心,構建了風電機組傳動鏈振動狀態監測系統。

系統軟件層作為客戶端,實現了傳感器類型、采樣速率、采樣周期等相關參數的控制以及與上位機的通信功能;系統硬件部分則作為下位機,對振動信號進行采集、處理、存儲與傳輸。利用FPGA強大的邏輯和數據處理能力,實現了振動信號全自動采集、振動信號濾波中心頻率的自跟蹤與A/D轉換速率的自適應。通過EDMA,實現了FPGA與ARM之間的數據高速傳輸,使得本系統在具備大量數據處理能力的同時,保證了數據的穩定和準確性,可滿足大型風電機組振動狀態實時監測和分析的需求。

參考文獻:

[1] 王效,劉曉光.基于ARM的風電齒輪箱振動監測系統設計[J].發電技術,2013,34(2):16-19.

[2] 程啟明,程尹曼,王映斐,等.風力發電系統技術的發展綜述[J].自動化儀表,2012,33(1):1-8.

[3] 李勇,胡育文,黃文新,等.變速運行的定子雙繞組感應電機發電系統控制技術研究[J].中國電機工程學報,2008,28(20):124-131.

[4] 夏長亮,張茂華,王迎發,等.永磁無刷直流電機直接轉矩控制[J].中國電機工程學報,2008,27(3):25-35.

[5] 楊建剛.旋轉機械振動分析與工程應用[M].北京:中國電力出版社,2007.

[6] 路遙,江漢紅,芮萬智.基于ARM的風電機組遠程監測系統的設計[J].船電技術,2015,66(2):9-12.

[7] 王慧中,沈燕妮.基于DSP+ARM的風電機組狀態監測系統研究[J].電氣自動化,2011,33(6):26-28.

[8] 韓宏宇.基于FPGA的風電監測系統數據采集單元設計[D].北京:北京化工大學,2011.

[9] 張夏疆,田新啟.CPLD數字倍頻原理在旋轉機械振動信號采集中的應用[J].工業控制計算機,2009,22(5):9-10.

[10]但永平,彭洪濤,王東云,等.EDMA在圖像數據快速傳輸中的應用[J].液晶與顯示,2013,3(1):99-104.

[11]TI.AM335X:ARM Cortex-A8微處理器開發方案[J].世界電子元器件,2014(3):19-21.

[12]韋東山.嵌入式Linux應用開發完全手冊[M].北京:人民郵電大學,2008.

[13]ROBERT L.Linux內核設計與實現[M].陳莉君,康華,譯.北京:機械工業出版社,2011.

[14]JONATHAN C,ALESSANDRO R,GRGE K H.Linux設備驅動程序[M].北京:中國電力出版社,2006.