基于FPGA和UDP/IP協議的千兆網絡圖傳系統①

韓劍南, 胡遼林

(西安理工大學 機械與精密儀器工程學院,西安 710048)

圖像處理、機器視覺等技術是當今工程領域的熱門課題,圖像傳輸系統的高速化、網絡化已經成為這個方向的一個重要組成部分,也被視為國內外相關領域的焦點[1]. 隨著攝像頭硬件性能的提升,圖像的像素量也大幅提高. 圖像傳輸設備的高速化和集成化已經成為主流發展方向.

針對網絡數據傳輸的硬件系統,現在主流的方案都源自不同的嵌入式平臺進行搭建. 各自硬件方案都有各自的優缺點,而達到速度、效率和移植性三者之間的平衡才是以太網傳輸系統設計的關鍵. 千兆以太網傳輸硬件系統[2-5]主要有:

(1)基于進階精簡指令集機器(Advanced RISC Machines,ARM)的硬件平臺. 該平臺需要ARM的芯片配上千兆網卡,運行在Linux系統下. 此硬件平臺有使用C語言編程,易于移植在同類芯片,指令集兼容性好等優點. 但其缺點也很突出,因為引入網卡,所以需要編寫驅動文件,不同網卡驅動不兼容,維護成本高,操作復雜.

(2)基于數字信號處理(Digital Signal Processing,DSP)芯片的硬件平臺. 對于網絡而言,DSP內也有集成的以太網接口芯片. 在編寫程序時,可以調用庫文件實現以太網的通信,所以DSP平臺相較ARM平臺來說開發更容易. 但是,該平臺軟件開發的庫文件冗余,裁剪和自定義難度大,系統設計靈活性不高. 同時因為DSP采用串行指令流和中斷機制,也產生了系統執行效率不高的問題.

(3)基于現場可編程門陣列(Field Programmable Gate Array,FPGA)的硬件平臺. FPGA具有邏輯資源多,集成度高,處理速度快,執行效率高,編程靈活等特點. 針對網絡應用,常使用FPGA和物理層(Physical Layer,PHY)芯片的這種硬件組合. PHY芯片處于OSI模型的物理層,是一種與外部信號相連的接口芯片. 主要作用是定義了數據傳輸所需要的電平標準、時鐘基準和數據編碼等信息,并向數據鏈路層提供接口標準. 該系統不用調用庫函數或者使用串行指令,不需要驅動的編寫. 通過分模塊編寫Verilog代碼,完成介質訪問控制層(Media Access Control,MAC)配置和PHY芯片的配置,相對靈活地實現用戶數據報協議/因特網互聯協議(User Datagram Protocol/Internet Protocol,UDP/IP)協議.

針對這種非壓縮、大數據量的特點,本文設計了一種基于FPGA硬件數據自定義UDP/IP協議的千兆網絡圖傳系統的解決方案. UDP/IP協議主要用在同步通信或者強調實時性的通信中,該協議是面向無連接的通信,所以任何時刻都能發送數據[6-8]. 而且,因為它處理過程很簡單,所以適合進行高速處理. 利用FPGA的高速性、靈活性、硬件資源豐富等特點,實現硬件UDP/IP協議棧,達到高速傳輸的目的.

1 系統總體框架設計

系統選用Xilinx公司XC6SLX45T芯片作為硬件開發平臺,并外接VSC8601芯片、ADV7513芯片和三代雙倍數據速率(Double Data Rate 3,DDR3)SDRAM芯片. VSC8601芯片作為千兆以太網的PHY芯片,用于規定以太網物理層電平標準等. ADV7513芯片作為高清晰度多媒體接口(High Definition Multimedia Interface,HDMI)輸出圖像信息. DDR3 SDRAM主要用于緩存大量圖像信息. 由于DUP/IP協議模塊使用125 MHz的時鐘,接收數據和發送數據各使用4根數據線發送DDR數據,所以傳輸速度可以達到千兆級別.

系統設計原理,如圖1所示. PC機將圖像信息以UDP協議封裝的形式,通過雙絞線發送到以太網PHY芯片. 由于以太網傳輸數據采用吉比特介質獨立接口(Reduced Gigabit Media Independent Interface,RGMII)進行傳輸數據,所以FPGA與PHY芯片之間通信,需要在FPGA端編寫雙倍數據速率(Double Data Rate,DDR)數據和單倍數據速率(Single Data Rate,SDR)數據之間的轉換模塊. SDR數據經過UDP/IP協議模塊,將圖像信息存入DDR3控制模塊. 當一幅圖像存儲完后,會產生一個標志信息,UDP/IP協議模塊會將圖像信息封裝起來,按照UDP/IP協議的格式,發給PHY芯片. PHY芯片通過雙絞線將數據發給PC機. 同時圖像顯示控制模塊也會不停讀取DDR3 SDRAM中的圖像信息,通過HDMI接口芯片顯示在顯示器上.

圖1 系統設計原理

2 功能模塊設計

2.1 UDP/IP協議模塊

系統根據UDP/IP協議定義以下用于傳輸圖像的UDP/IP協議,如圖2所示. 圖中第一行為UDP/IP協議報頭格式,屬于國際標準格式[9]. 在UDP/IP數據內容中,用戶可以自定義協議,用來傳輸用戶的數據,如圖2中第二行和第三行. 發送數據時,需要先發送一個數據頭包,然后再發送數據信息. 由于UDP協議規定,每個UDP報文長度不得超過1500個字節,而一個像素占3個字節,400個像素即1200個字節. 現定義一個數據包最多攜帶400個像素信息,所以傳輸一幅1024×768個像素的圖像的一行(1024個像素點),需要分3個數據包發送.

當UDP/IP協議模塊接收到圖像信息時,需要先將PHY芯片發來的信息通過時序邏輯,將數據的時序穩定. PHY芯片的時鐘需要經過一個數字時鐘管理(Digital Clock Manager,DCM)延遲90度相位,這樣能夠提高時鐘采集數據的穩定性[10,11]. 將穩定后的數據經過循環冗余校驗(Cyclic Redundancy Check 32,CRC32)解碼模塊后,通過像素提取模塊將像素信息提取出來[12],將像素信息經過DDR3控制模塊寫入DDR3. 當一幅圖像存儲完后,DDR3控制模塊會產生一個標志,成幀模塊會將像素打包成UDP協議幀,在經過校驗和算法模塊添加校驗和,最后通過CRC32編碼生成完整的UDP報文. 此時UDP報文是SDR數據,需要經過變換成DDR數據發送給PHY芯片,最后PC機接收到數據,完成圖像傳輸.

2.2 DDR3控制模塊

針對DDR3 SDRAM來說,Xilinx公司XC6SLX45T芯片中內置內存控制塊(Memory Controller Block,MCB)硬核,MCB是用來控制DDR3 SDRAM. 而用戶需要編寫一個控制MCB的模塊,實現控制MCB模塊,間接控制DDR3 SDRAM[13,14],其控制結構如圖3所示.

命令先入先出隊列(First Input First Output,FIFO)用于接收DDR3 SDRAM的讀寫指令,每當MCB模塊接收到讀或寫指令后,便會將數據FIFO中的數據讀走或寫入,存入或讀取DDR3 SDRAM. 控制MCB模塊的Modelsim仿真波形如圖4所示. MCB模塊設置為突發長度為64.

2.3 圖像顯示控制模塊

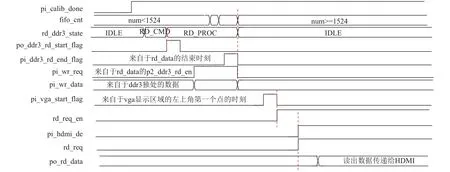

當DDR3 SDRAM芯片上電,該芯片需要初始化. 之后會產生一個標志信號. 只要該標志信號拉高,則圖像顯示模塊一直循環從DDR3開始讀數據. 由于MCB讀出的時鐘頻率是125 MHz,而720 P的圖像顯示時鐘頻率是65 MHz,所以需要FIFO進行跨時鐘域. 而控制FIFO讀數據到HDMI需要設定一個閾值,實驗設定的閾值是1524個數據,當FIFO內數據超過該閾值則進行讀數據到HDMI,并且MCB只有在FIFO內數據小于該閾值時,才向FIFO內寫數據. 其讀寫時序如圖5.

圖4 Modelsim仿真波形

圖5 圖像數據FIFO時序

3 系統測試

系統的硬件測試平臺如圖6所示,左顯示器用于HDMI顯示PC機發來的圖像,右顯示器用于操作PC機軟件,PC端的軟件可以顯示FPGA發來的圖像預覽圖,如圖7所示. 系統將硬件開發平臺用雙絞線與計算機直接相連,先將圖像通過PC機發送給FPGA,FPGA收到該圖像后,將圖像通過HDMI顯示到顯示器上,同時將數據重新打包,將圖像信息以UDP協議封裝成數據包,通過網線發送到計算機上,計算機收到后,軟件顯示收到的圖像預覽圖.

圖8是使用Wireshark軟件抓取網絡數據包,用該軟件可以捕獲到FPGA發送給PC機的UDP協議封裝的圖像數據. 可以從圖8中看出,計算機收到的數據符合UDP/IP協議報文格式,數據信息為頭包+數據包方式傳輸,并且一行圖像分成了三包數據發送.

圖9是使用ChipScope軟件抓取的FPGA內部信號的時序圖,ChipScope不同于Modelsim仿真軟件,它顯示的時序邏輯并不是仿真波形,而是開發板中的實際波形. 從圖9可以看出FPGA發出的數據包格式正確,硬件系統功能正常.

圖6 硬件測試平臺

圖10是使用Wireshark軟件獲取的以太網吞吐量,可以看出傳輸速度是90124包/s. 一個數據包是1200個字節,一個字節是8 bit. 經過簡單計算可以得到傳輸速度是865.19 Mbit/s. 由于數據包之間會有包間隔時間,所以不能真正達到1024 Mbit/s的速度.

4 結論

本系統以FPGA和PHY芯片作為硬件平臺,硬件實現UDP/IP協議棧封裝圖像信息. 系統設計靈活、體積小、速度快,能夠滿足高速傳輸圖像的要求. 由于系統MAC層協議是Verilog編程實現,所以調整方便、成本低、接口簡單. 實驗測試結果表明,系統傳輸數據穩定,傳輸速度可達865.19 Mbit/s,易于維護,便于移植,為高清圖像傳輸提供了一種良好的解決方案,應用前景廣泛.

1俞鵬煒,任勇,馮鵬,等. 基于FPGA 的千兆以太網CMOS圖像數據傳輸系統設計. 國外電子測量技術,2016,35(11): 76-81. [doi: 10.3969/j.issn.1002-8978.2016.11.018]

2付高原,郭臣,潘進勇,等. 基于FPGA的UDP點對點傳輸協議實現. 電子設計工程,2017,25(2): 181-184.

3姜興家,劉布民,何春梅,等. 一種基于FPGA實現的視頻流可靠傳輸方案. 物聯網技術,2014,4(2): 44-46.

4王宇聰,韓啟祥,蔡惠智. 聲納信號處理中UDP協議數據傳輸研究與設計. 現代電子技術,2012,35(1): 78-79,84.

5侯義合,張冬冬,丁雷. 基于FPGA+MAC+PHY的千兆以太網數傳系統設計. 科學技術與工程,2014,14(19):275-279. [doi: 10.3969/j.issn.1671-1815.2014.19.053]

6顧穎彥. 反射內存網實時通信技術的研究. 計算機工程,2002,28(7): 143-144,257.

7李勛,劉文怡. 基于FPGA的以太網接口設計與實現. 自動化與儀表,2014,29(5): 57-60.

8肖衛國,爾聯潔,謝廷毅,等. 基于共享內存機制微機實時網的數據傳輸實時性研究. 系統仿真學報,2004,16(8):1717-1720.

9沈瀟波,聶玉鑫. 基于UDP協議的數據橋接單元設計. 聲學與電子工程,2012,(1): 27-29.

10Zhao LD. Using UDP datagram to realize a distributed control mode at high-speed data communication. Physics Procedia,2012,(25): 886-891. [doi: 10.1016/j.phpro. 2012.03.173]

11高富強,夏禹,戴正國,等. 基于UDP的工業CT數據傳輸系統. 核電子學與探測技術,2012,32(3): 311-315,347.

12陳杰華. 基于FPGA的IP數據報的提取模塊的設計. 福建電腦,2010,26(2): 125-126.

13范璐,顧國華,陳錢. 基于多路UDP的紅外圖像采集. 數據采集與處理,2012,27(S1): 186-189.

14胡冠敏,徐志軍,許廣杰. 基于FPGA的硬件協議棧精簡實現. 軍事通信技術,2011,32(3): 61-65.