檢測PLL穩(wěn)定的方法

楊衛(wèi)平

(珠海格力電器股份有限公司,廣東 珠海 519070)

1 PLL簡介

鎖相環(huán)(Phase Locked Loop,PLL)是一種反饋控制電路,主要用于產(chǎn)生時鐘。鎖相環(huán)的特點是:利用外部輸入的參考信號控制環(huán)路內(nèi)部振蕩信號的頻率和相位。因鎖相環(huán)可以實現(xiàn)輸出信號頻率對輸入信號頻率的自動跟蹤,所以鎖相環(huán)通常用于閉環(huán)跟蹤電路。按照架構(gòu)來分,鎖相環(huán)可分為模擬鎖相環(huán)、 數(shù)字鎖相環(huán)、數(shù)模混合型鎖相環(huán)。

模擬PLL中所有電路由模擬電路實現(xiàn),主要包括鑒相器(Phase Detector,PD)、環(huán)路濾波器(Loop Filter,LF)和壓控振蕩器(Voltage Controlled Oscillator,VCO)3部分。一般情況下,模擬鎖相環(huán)精度較高,起振和穩(wěn)定的時間較短,適用于對時鐘性能要求較高的場景。

數(shù)字PLL中所有電路由數(shù)字電路實現(xiàn),結(jié)構(gòu)包括鑒相器、低通濾波器(Low Pass Filter,LPF)、數(shù)字振蕩器(Digital Controlled Oscillator,DCO)與分頻器(Dividor,DIV),其中LPF輸出控制字(Control Word,CW)對DCO進行控制,如圖1所示。隨著數(shù)字電路的發(fā)展,數(shù)字鎖相環(huán)不僅吸收了數(shù)字電路可靠性高、體積小、價格低等優(yōu)點,還解決了模擬鎖相環(huán)的直流零點漂移、器件飽和及易受電源和環(huán)境溫度變化等缺點,此外還具有對離散樣值的實時處理能力,已成為鎖相技術(shù)發(fā)展的方向。

數(shù)模混合鎖相環(huán)則由數(shù)字電路與模擬電路混合實現(xiàn)。例如LPF與VCO由模擬電路實現(xiàn),而PD與DIV由數(shù)字電路實現(xiàn)。

圖1 數(shù)字PLL結(jié)構(gòu)

2 PLL穩(wěn)定檢測方法分析

PLL是時鐘的供給源,一般只有當PLL穩(wěn)定后才能輸出使用,不然可能導致應用邏輯混亂,因此PLL是否穩(wěn)定對判斷十分重要。判斷PLL穩(wěn)定的方法有多種,根據(jù)較常見的電路,通常可以有如下幾種。

2.1 直接計數(shù)法

PLL設計一般有RESET(復位)或POWER DOWN(斷電)的控制功能。當PLL從復位或斷電的狀態(tài)轉(zhuǎn)到工作狀態(tài)時,由PLL輸出時鐘CLK_OUT或外部輸入的參考時鐘REF_CLK作為計數(shù)器時鐘開始計數(shù),當計數(shù)器達到門限即認為PLL振蕩已經(jīng)穩(wěn)定。這樣做的好處是算法簡單,但不同條件下PLL電路達到穩(wěn)定的計數(shù)門限不好把握:如果門限取太小,則可能出現(xiàn)虛假的PLL穩(wěn)定結(jié)論;如果門限太大,則等待時間較長,影響系統(tǒng)使用;甚至出現(xiàn)嚴重的誤判,那就是PLL根本就不會穩(wěn)定,但計數(shù)器滿后,誤報PLL穩(wěn)定。因此直接計數(shù)法具有較大的局限性,就算計數(shù)器門限可配,也只適用于一定會穩(wěn)定并且穩(wěn)定時間有確定范圍的PLL。

2.2 借助UP/DOWN判斷法

PLL電路中包含PD模塊,一般PD模塊會輸出UP/DOWN兩個信號,UP=1表示REF_CLK比DIV_CLK相位領先,DOWN=1表示REF_CLK比DIV_CLK相位落后,或者根據(jù)實際電路反過來。從PLL起振到穩(wěn)定,一般UP/DOWN有如下規(guī)律。

(1)隨著PLL起振,UP=1/DOWN=0,如果PLL能穩(wěn)定,則UP=1寬度會逐步減小;(2)到某時刻,UP由1->0,DOWN由0->1,并且DOWN=1寬度會逐步增大然后逐步減小;(3)到某時刻,DOWN由1->0,UP由0->1,并且UP=1寬度會逐步增大然后逐步減小;(4)按2,3特點循環(huán),但UP/DOWN交替變化逐漸頻繁并且UP/DOWN最大寬度會逐步變小;(5)如果有外界因素干擾,UP/DOWN會重復2,3,4過程。因?qū)嶋H硬件電路存在延時,UP/DOWN可能存在短暫同時為0或1的情況。

根據(jù)UP/DOWN的以上規(guī)律,設計電路判斷UP/DOWN的變化趨勢,當達到某條件時可以認為PLL達到穩(wěn)定狀態(tài),例如:UP/DOWN交替變化達到一定次數(shù),或者UP/DOWN最大脈沖寬度小于設定的某門限值等。具體電路不一樣,但電路原理與總體框圖類似。

相比直接計數(shù)法,借助UP/DOWN判斷PLL穩(wěn)定的方法更加準確,確保PLL已經(jīng)達到穩(wěn)定狀態(tài),并且反映PLL穩(wěn)定狀態(tài)也較及時。但復雜應用環(huán)境,UP/DOWN判斷算法可能會比較復雜。

3 本文PLL穩(wěn)定檢測方法

本文提出一種基于CW規(guī)律檢測PLL是否穩(wěn)定的方法。一般數(shù)字PLL中,LPF輸出CW來控制DCO,因此CW可以從PLL電路直接獲取。一般的SoC設計中都會包含ADC(模數(shù)轉(zhuǎn)換模塊),利用該模塊,可以將模擬PLL或混合型PLL中LF輸出的模擬控制信號數(shù)字化得到CW,用于PLL穩(wěn)定的判斷。因此,基于CW檢測法在數(shù)字PLL、模擬PLL和混合型PLL均可應用。

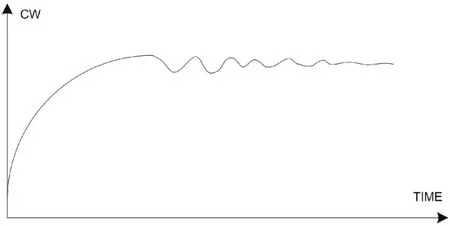

如果PLL能穩(wěn)定,一般CW的變化趨勢如圖2所示。PLL開始工作之后,CW會隨之增大(或減小,取決于實際電路),趨于穩(wěn)定時會出現(xiàn)振蕩,但會逐步收斂并最終趨于穩(wěn)定。因此,CW的振蕩變化就成了PLL穩(wěn)定的判斷因素。

圖2 CW變化趨勢

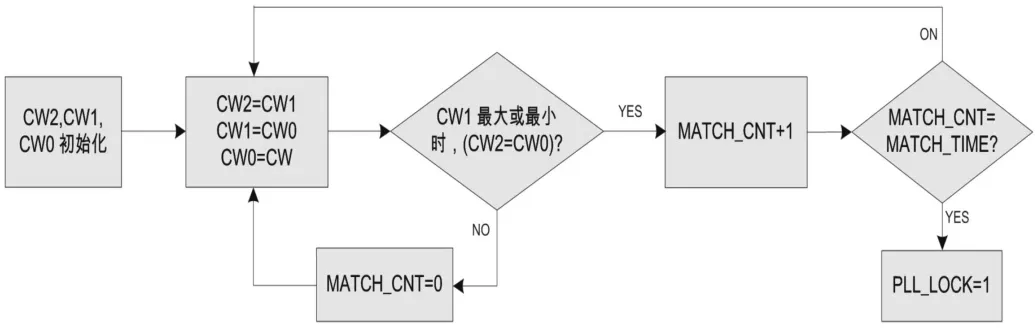

基于CW的這一規(guī)律,本文設計一種PLL穩(wěn)定檢測電路。電路輸入信號主要有參考始終REF_CLK、復位信號RESET、配置信號CONFIG以及CW信號,輸出信號為PLL_LOCK. 定義3個數(shù)字信號CW0,CW1與CW2,用于記錄連續(xù)的3個CW。定義數(shù)字信號MATCH_CNT,用于記錄滿足條件的次數(shù),條件是CW1處于最高點(CW1>CW2且CW1>CW0)或最低點(CW1<CW2且CW1<CW0)時CW2=CW0。定義數(shù)字信號MATCH_TIME,用于表示要求達到條件的次數(shù),條件是CW1處于最高點或最低點時CW2=CW0。電路主要包括4個模塊。

(1)初始化模塊INIT_REG.INIT_REG模塊獲取配置的信息,包括CW0~CW2的初始值、MATCH_TIME值。

(2)CW獲取與比較模塊LATCH&COMPARE.LATCH&COMPARE模塊獲取連續(xù)的CW0~CW2,并進行比較判斷,看是否滿足條件,即CW1處于最高點(CW1>CW2且CW1>CW0)或最低點(CW1<CW2且CW1<CW0)時CW2=CW0.

(3)匹配記錄模塊MATH_CNT_GEN. MATH_CNT_GEN模塊對MATH_CNT進行判斷并記錄。

(4)穩(wěn)定判斷模塊LOCK_JUDGE. LOCK_JUDGE模塊判斷MATH_CNT值是否達到MATCH_TIME要求,并輸出PLL_LOCK狀態(tài)。其中MATCH_TIME值是可配置的,值越大表示穩(wěn)定判斷越嚴格。

完整的PLL穩(wěn)定判斷流程如圖3所示。對CW0~CW2賦予3個極限初值,隨著PLL起振,在REF_CLK的上升沿或下降沿時,CW0~CW2不斷被賦予連續(xù)3個時刻的CW.CW1處于最高點或最低點時,若出現(xiàn)CW2=CW0的情況,則將MATCH_CNT的值加1,不然將MATCH_CNT清0。若MATCH_CNT達到要求次數(shù)MATCH_TIME,則表示PLL達到穩(wěn)定狀態(tài),輸出PLL_LOCK=1.

圖3 PLL穩(wěn)定判斷流程

4 實際仿真結(jié)果及分析

運用本文推薦基于CW檢測PLL穩(wěn)定的方法與電路,在數(shù)字PLL穩(wěn)定進行判斷,效果如圖4所示。在圖中,隨著CW變化,當CW1處于最高點時并出現(xiàn)CW2=CW0的情況,則將MATCH_CNT的值加1,很快MATCH_CNT值達到MATCH_TIME,PLL_LOCK=1。另外,仿真過程中發(fā)現(xiàn),MATCH_TIME越大,由于條件更嚴格,PLL_LOCK=1時間變長。由仿真結(jié)果可見,PLL穩(wěn)定結(jié)果準確并且用時較短。

5 結(jié)語

本文提出基于CW檢測PLL穩(wěn)定的方法相比直接計數(shù)法與借助UP/DOWN判斷法,判斷結(jié)果準確,算法簡單,應用于任何含有PLL的芯片或電路中,特別適用于數(shù)字PLL、系統(tǒng)中同時含有ADC電路的模擬PLL或混合PLL。

圖4 PLL穩(wěn)定判斷仿真

[參考文獻]

[1]DEN DULK R C.Digital PLL lock-detection circuit[J].Electronics Letters,1988(24):14.

[2]VOLODYMYR K,PAVAN K HANUMOLU,K et al.Moon school of the EECS,a digital PLL with a stochastic time-to-digital converter[D].Oregon:Oregon State University,2006.

[3]STENSBY J.A new lock detector for phase-lock receivers[J].Symposium System Theory,2001(1):215-219.

[4]文武,魏慧婷,文治平,等.一種基于全數(shù)字動態(tài)加速鎖定技術(shù)的PLL頻率綜合器[P].2014-04-23.