近閾值非預充靜態隨機存儲器

蔡江錚, 黑 勇, 袁 甲, 陳黎明

(1. 中國科學院微電子研究所 智能感知中心,北京 100029;2. 中國科學院大學 微電子學院,北京100029)

近閾值非預充靜態隨機存儲器

蔡江錚1,2, 黑 勇1,2, 袁 甲1,2, 陳黎明1,2

(1. 中國科學院微電子研究所 智能感知中心,北京 100029;2. 中國科學院大學 微電子學院,北京100029)

為了降低靜態隨機存儲器在處理聲音和視頻數據時的功耗,提出一款新型的非預充單元.相比常規6管和8管單元,其讀操作消除了預充機制,抑制了無效的翻轉,因此功耗得到顯著優化.本單元通過多閾值技術,在保證低電壓區域讀噪聲容限的同時也加強了數據讀出的能力.而且通過引入切斷反饋環的機制,有效地提升了單元寫能力.此外,在存儲陣列中應用半斯密特反相器,大幅地提升了靜態隨機存儲器讀操作的性能.基于SMIC 130 nm 工藝,分別實現容量為 6 kbit 的非預充和常規8管靜態隨機存儲器測試芯片.測試和仿真數據表明,這種新型存儲器相比常規8管存儲器在功耗的抑制上具有顯著優勢,可以作為低功耗應用的良好選擇.

靜態隨機存儲器;非預充;聲音和視頻;低功耗

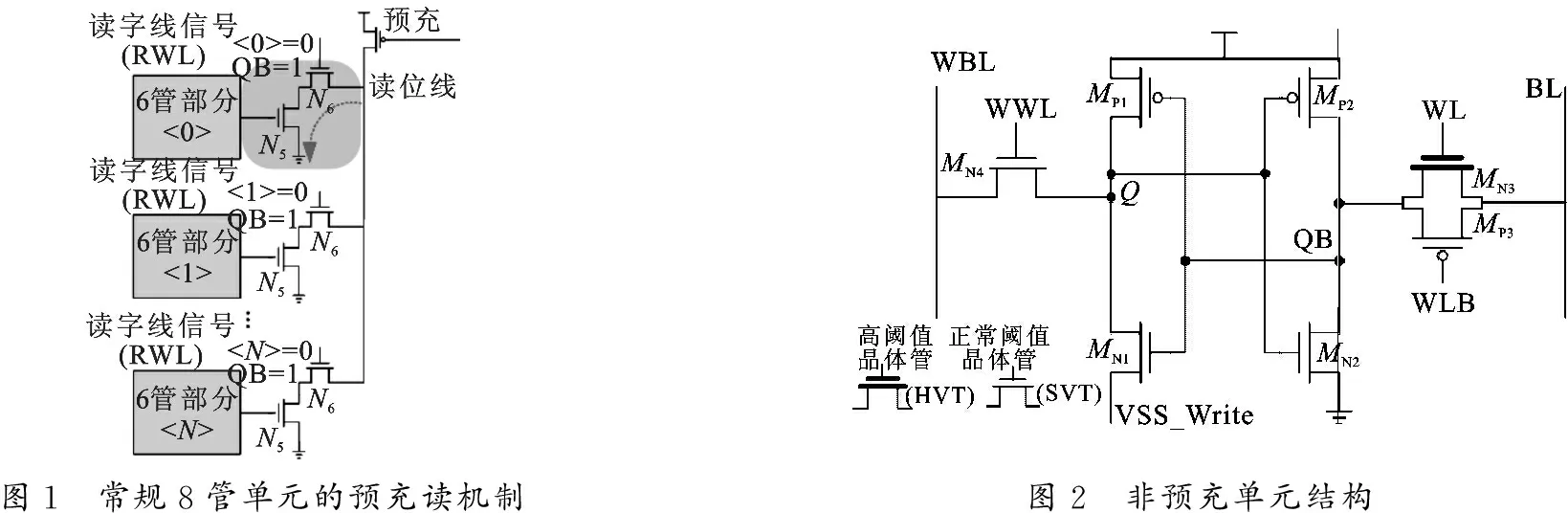

隨著醫療電子、可穿戴設備和物聯網等低功耗應用的快速發展,功耗取代性能逐步成為芯片設計中最核心的指標[1].靜態隨機存儲器(Static Random Access Memory,SRAM)占據了芯片相當大比例的功耗,因此靜態隨機存儲器功耗的降低成為芯片功耗優化的關鍵所在.近亞閾值技術作為最有效的手段之一,被廣泛應用于靜態隨機存儲器的低功耗設計中[1-7].在近亞閾值區,經典6管靜態隨機存儲器受制于穩定性和漏電等問題不能正常工作,因此8管靜態隨機存儲器成為低功耗芯片的首選[3].為了進一步降低靜態隨機存儲器的讀寫功耗,在某些特定應用場景中,研究者不斷發掘存儲在靜態隨機存儲器中的諸如聲音和視頻等特定數據的特點進行電路設計從而獲得功耗優化.文獻[8]基于視頻數據的特點,混合使用8管和6管單元,使得靜態隨機存儲器工作在更低的電壓下.文獻[9]也從視頻數據的特點出發,將數據進行編碼,同時將寫位線設定為最小翻轉的情況,從而降低視頻數據寫入的功耗.但是這些方法都會引入額外的電路開銷.而且,基于常規8管單元設計的靜態隨機存儲器都采用如圖1所示的預充機制實現讀操作:在準備階段,預充信號為低電平,讀位線被預充到高電平;然后在判定階段,字線信號打開,讀位線的狀態由單元內部數據決定.然而,預充機制的存在使靜態隨機存儲器在處理聲音和視頻數據時產生無效功耗[10].聲音和視頻中存在大量相同數據,導致靜態隨機存儲器中不同單元的存儲內容相同,因此當讀取存儲內容時,會獲得連續的“0”或“1”數據.連續“0”數據的讀出在靜態隨機存儲器中會引起不必要的翻轉.文獻[11]通過將大多數的“0”數據轉變為“1”數據的方式達到節省功耗的目的.然而,這種方法并不能完全解決連續讀“0”帶來的功耗開銷問題.基于以上問題,筆者提出非預充的單元結構,通過消除預充機制實現對聲音和視頻數據的低功耗處理.

圖1 常規8管單元的預充讀機制圖2 非預充單元結構

1 非預充單元結構

非預充單元的結構如圖2所示.晶體管MP1,MP2,MN1和MN2組成背靠背反相器,實現數據保持功能;MP3和MN3組成傳輸門,實現數據讀寫傳導功能;MN4為寫操作晶體管,只在寫操作時有效,實現寫能力的提升.在讀操作時,互補字線信號寫線信號(WL)和寫字線反相信號(WLB)被同時使能,而寫字線信號(WWL)處于無效狀態,此時單元右側單向開啟,內部反相數據(QB)通過傳輸門決定位線的最終狀態.因此,位線(BL)不需要被提前預充至高電平,預充機制可以被消除.在寫操作時,字線信號WWL,WL,WLB全部被使能,單元兩側全部開啟,寫位線信號(WBL)和位線(BL)接收寫驅動電路的輸入數據,實現數據的寫入.但是為了確保單元讀操作時在近閾值區的抗干擾能力,其傳輸門的傳導能力不能設計過強,因此位線(BL)不能輕易改寫內部數據,導致寫能力被弱化.為了增強寫能力,在單元中引入了切斷反饋環的方式.在寫操作時,其中一個反相器的地(VSSWrite)被懸空,所以位線(BL)能相對輕松地改寫內部數據.與此同時,當反饋環被切斷時,晶體管MN4能迅速改變右側的反相器的狀態,從而進一步加強寫能力.

2 功耗的優化

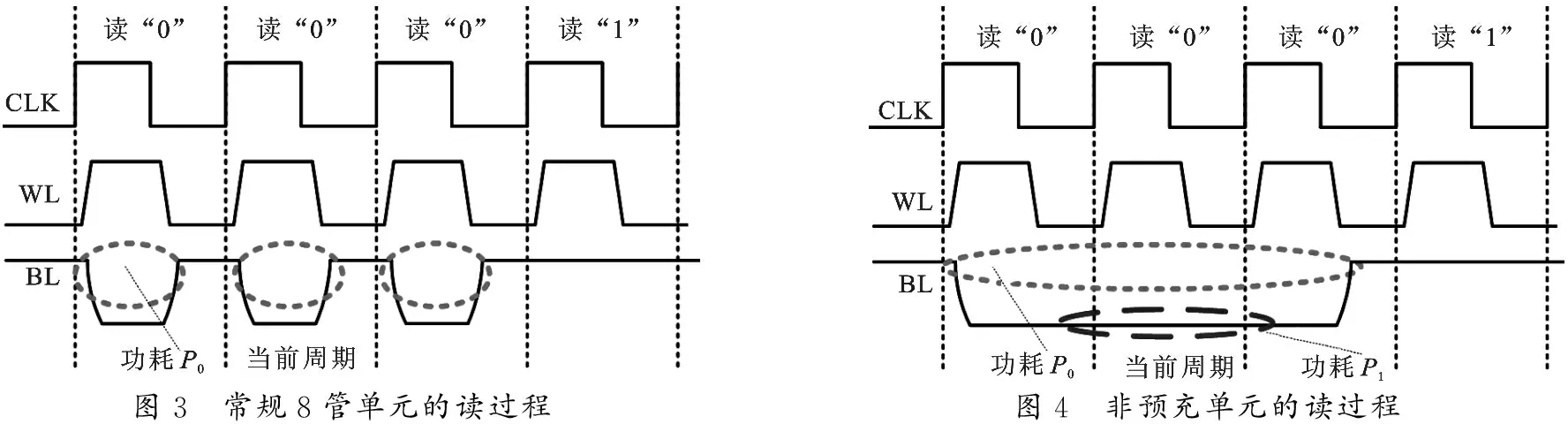

基于前述分析,常規單元結構受制于預充機制,在處理連續“0”數據時存在無效的翻轉,具體的過程如圖3所示.在讀取連續“0”的情境中,前一個周期完成后,位線會被重新預充到高電平,然后當前周期再開始新的一輪位線放電過程.實質上,由于相鄰周期讀取的數據是一致的,這個不斷翻轉的過程是無意義的.這種不必要的翻轉一直持續到讀“1”時刻的來臨.為了解決這個問題,非預充單元消除了無效翻轉,讀操作的邏輯如圖4所示.在第1次讀取“0”數據時,位線進行一次翻轉,此后每次“0”的讀取都不再進行翻轉,一直持續到“1”的讀取才又一次進行翻轉.因此,連續“0”數據的讀取只需要一次充放電的開銷.隨著讀“0”時間的增加,整體功耗的優化就會很顯著.

定量對比不同單元間的功耗,將常規單元讀操作時位線在每個周期(T)中一次充電和放電過程中產生的功耗設定為P0,則N個讀“0”周期消耗的總能量是NTP0.對于非預充單元而言,N個周期中位線只有一次充電和放電的過程,等效為常規單元一個周期的進程,其余N-1 個周期位線不進行任何翻轉.同時,在翻轉周期中非預充單元產生的功耗與常規8管單元近似,都為P0.假定不翻轉周期的功耗為P1,則非預充單元在N個周期中總能量的消耗為TP0+ (N-1)TP1.由于P1遠遠小于P0,所以非預充單元的能量消耗可以近似為常規單元的 1/N.隨著讀“0”周期數的增多,非預充單元相比常規單元在功耗開銷方面優勢越來越顯著.

圖3 常規8管單元的讀過程圖4 非預充單元的讀過程

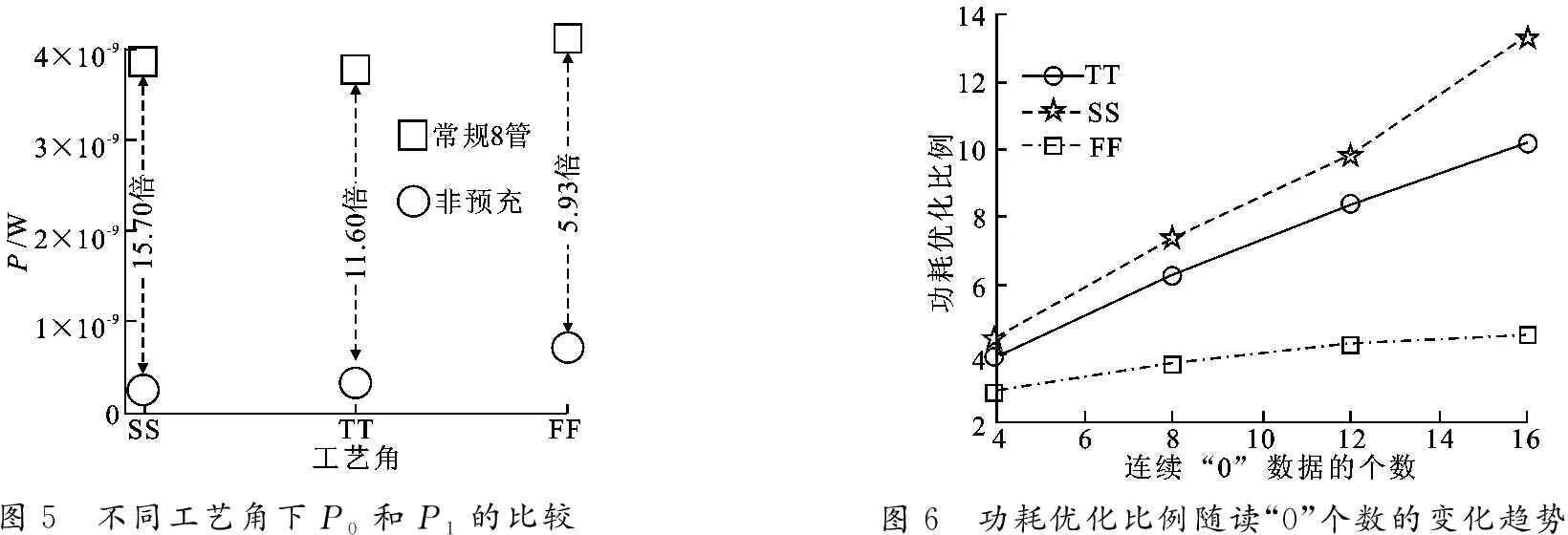

在0.5 V電壓下,使常規8管單元的讀位線在每次讀操作時都進行翻轉,仿真其翻轉功耗P0;使非預充單元的位線不翻轉,仿真其靜態功耗P1.在不同工藝角下,非預充單元的功耗都顯著降低,如圖5所示.

圖5 不同工藝角下P0和P1的比較圖6 功耗優化比例隨讀“0”個數的變化趨勢

圖5是對單次讀操作的仿真.如果按照圖4所示的實際情況工作: 假設存在N個讀“0”周期,分別對8管和非預充單元進行功耗分析,并以8管單元功耗和非預充單元功耗的比值來衡量優化比例,則這段時間內的功耗優化如圖6所示.隨著N的增大,每個工藝角下的功耗優化效果都呈增強趨勢.當然,優化效果也不能無限增長,它受兩個因素制約: 首先受應用中“0”數據多少決定; 其次還受靜態隨機存儲器陣列中掛接的單元數目的影響.當陣列中單元數目確定后,即使應用中存在的“0”的個數大于單元數,功耗的優化比例也只能被限定在固定的范圍內.此外,由于預充機制被消除,靜態隨機存儲器可以省去預充電路,從而降低功耗.而且由于預充電路的節省,時鐘電路的負載和尺寸也可以被優化,進而使功耗進一步降低.

3 讀操作分析

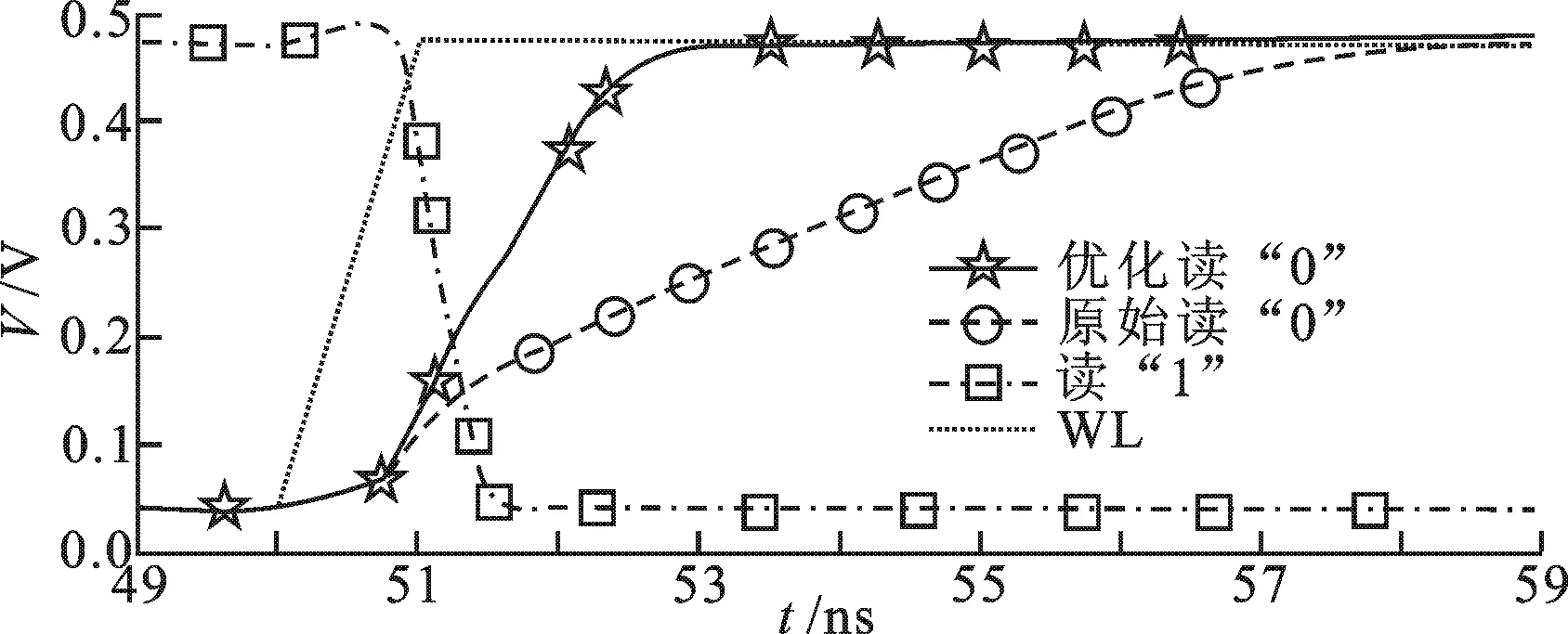

圖7 非預充單元讀能力

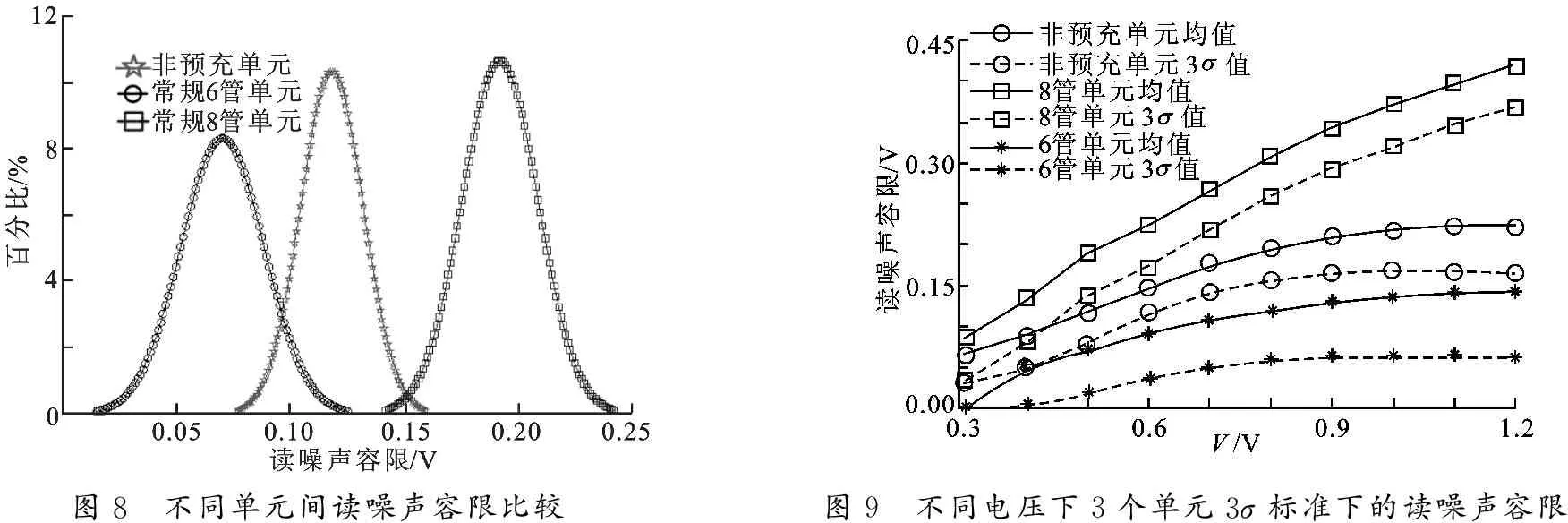

然而,非預充單元無法隔離讀寫操作,讀操作時外界噪聲仍然可以通過傳輸門進入單元內部,從而影響已有數據的穩定性,因此相比8管結構,其讀噪聲容限存在劣勢[12].為了緩解這種劣勢,非預充單元通過兩種方式加強讀噪聲容限:加大單元中背靠背反相器的尺寸,保證即使在外界噪聲被引入的狀況下,數據還能穩定保持.但是,這會犧牲部分寫能力.減小噪聲耦合路徑的強度,采用高閾值技術弱化傳輸門的導通能力.當傳輸門由高閾值晶體管組成時,此時路徑抑制噪聲的效果最佳.但是這也減弱了內部數據改變位線狀態的能力,影響讀出效果.圖6展示了單個非預充單元的讀出能力,其中原始讀“0”操作表示傳輸門晶體管都為高閾值晶體管時的讀“0”的能力,優化讀“0”操作表示傳輸門是混合閾值時的讀能力情況.由圖7可知,在原始讀狀態中,非預充單元讀“1” (Q=1,QB為“0”)的能力遠強于讀“0” (Q=0,QB為“1”)的能力.若傳輸門全部采用高閾值晶體管,則雖然抑制噪聲進入單元內部的效果變強,但同時也使得內部數據傳輸到位線的能力大大減弱,因此針對讀“1”與讀“0”的情況,進行混合閾值的使用.在優化過程中,將傳輸門中的N溝道金屬氧化物半導體(N-channel Metal Oxide Semiconductor,NMOS)采用高閾值晶體管,P溝道金屬氧化物半導體(P-channel Metal Oxide Semiconductor,PMOS)采用正常閾值晶體管.優化后的讀“0”操作的變化時間相比原始操作更短,提升了讀操作的性能.這既保證了單元對位線的改寫能力,同時又弱化了噪聲傳輸路徑,有效地提升了讀操作的穩定性.此外,由于非預充單元是單端結構,外部噪聲耦合進入單元內部的路徑只有一條,與常規6管單元相比,引入噪聲的概率降低,噪聲容限相對提高.但是與常規8管單元相比,非預充單元還是會引入噪聲的,故讀噪聲容限仍然有一定的惡化.圖8表示在 0.5 V 電壓下,常規6管結構、非預充單元和常規8管結構在 10 000 次蒙特卡羅仿真中的讀噪聲容限.

圖8 不同單元間讀噪聲容限比較圖9 不同電壓下3個單元3σ標準下的讀噪聲容限

非預充單元的讀噪聲容限是0.12 V,相比常規8管結構和6管結構分別降低了36%和提升了71%.此外,以上的噪聲容限都是基于最惡劣的靜態情況進行分析的,在實際應用中情況會有所緩和,讀操作的穩定性還會進一步增強.由于聲音和視頻數據中存在大量連續的“0”和“1”,所以位線跳變頻率較低,從而引入的噪聲相對較少,這有利于讀噪聲容限的提升.而且,當位線狀態與單元內部數據一致時,單元的讀噪聲容限可以達到與常規8管結構相似的能力,這種情況在此類應用中出現的概率很高.所以,非預充單元的讀噪聲容限在 0.5 V 的電壓下是非常樂觀的.為了進一步說明不同電壓下3個單元噪聲容限的情況,用3σ標準進行評判,如圖9所示.隨電壓下降,常規8管和非預充單元讀噪聲容限充足,而常規6管單元惡化嚴重.

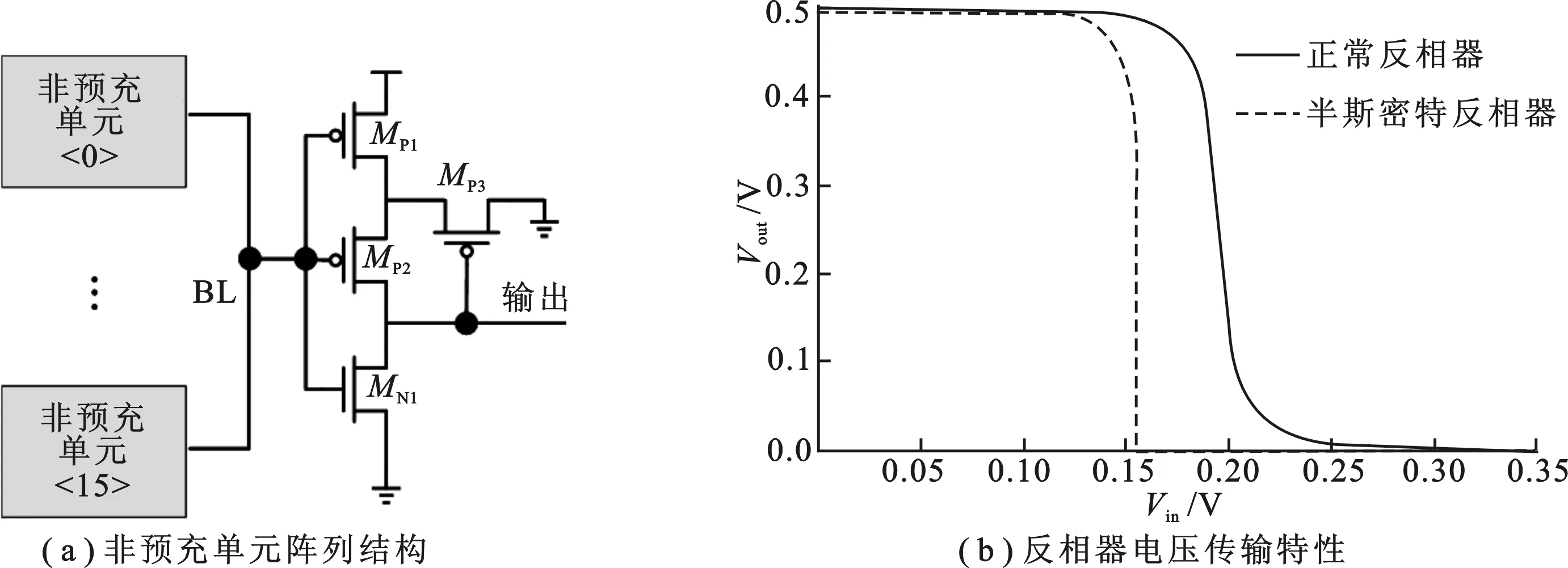

圖10 非預充單元的陣列結構及反相器電壓傳輸特性曲線

與此同時,非預充單元改變位線狀態的能力不僅受到傳輸門和背靠背反相器強度的影響,也受到位線負載的制約.因此,在組成陣列時,每根位線上連接的單元數受到限制.而且,由于單元讀“1”能力強于讀“0”能力,可以將連接位線的反相器進行特殊設計用以平衡讀出能力.反相器的電壓傳輸特性曲線可以被設計得更偏向低電平,從而有利于“0”數據的讀取.整個陣列結構如圖10(a)所示,每根位線連接16個非預充單元.而反相器采用半斯密特反相器,與普通反相器相比,電壓傳輸特性線向低電平的偏移更加顯著,如圖10(b)所示.因此“0”數據讀出時,位線的充電過程會被快速感知,增強了讀能力.

4 寫操作分析

在單元尺寸設計中,讀噪聲容限的提升是首要目的,相應地,寫噪聲容限被弱化.為了加強寫能力,采用切斷背靠背反相器反饋環的機制,如圖2所示.在寫操作時,左側反相器的地可以浮動,從而打斷反饋環使內部數據更容易被改寫.同時多個單元共用VSSWrite信號,可以有效地降低電路開銷.為了保證寫入數據的正確性,VSSWrite信號需要比字線信號提前.在 0.5 V 電壓下,最壞的寫情況出現在SNFP工藝角中.此時,如果VSSWrite不浮動,則寫噪聲容限只有 6 mV,意味著在最壞情況中,單元不能有效操作在 0.5 V 電壓下.當采用優化的寫機制后,有效地提升了寫能力,使得單元在 0.5 V 電壓下正常工作.

5 流片與測試

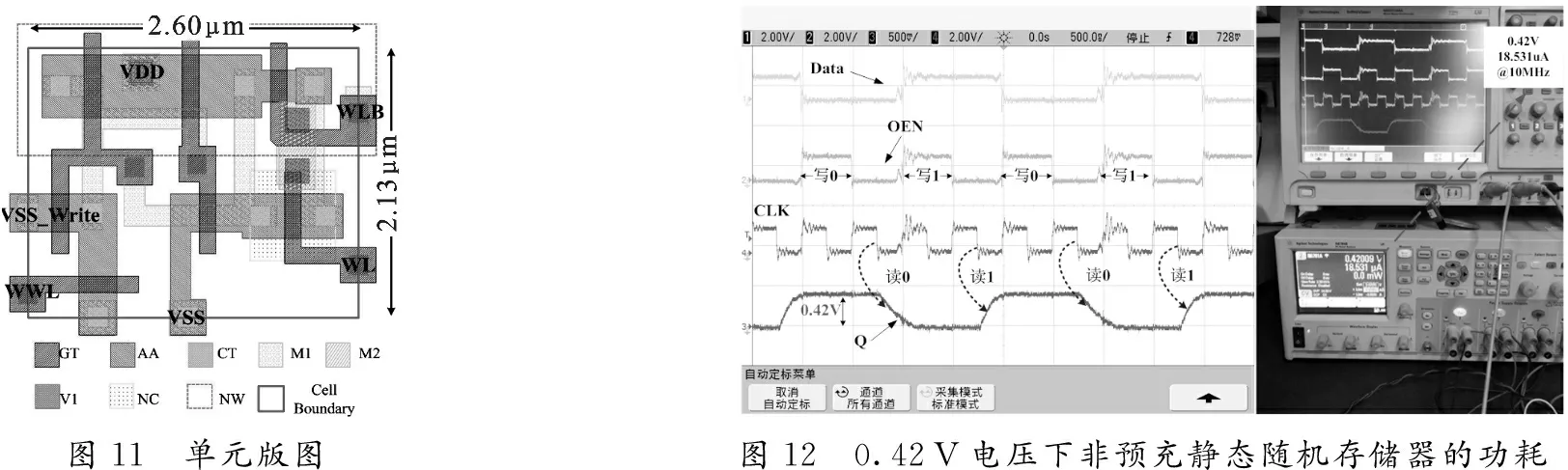

基于中芯國際集成電路制造(上海)公司(Semiconductor Manufacturing International Corporation,SMIC) 130 nm 工藝,設計了容量為 6 kbit 的非預充靜態隨機存儲器,單元版圖如圖11所示,面積為 5.53 μm2,而工藝廠商提供的6管單元,面積為 3.014 μm2,因此本單元面積增加83%.這是因為非預充單元控制信號較多,而且還使用正常設計規則檢查(DRC規則),而工藝廠商的單元使用特殊設計規則檢查.因此,如果去除規則的差別,則面積的增長會有所緩和.

圖11 單元版圖圖12 0.42V電壓下非預充靜態隨機存儲器的功耗

筆者還制造了相同容量的常規8管靜態隨機存儲器作為比對.在室溫下,非預充靜態隨機存儲器的最低工作電壓為 0.42 V,當它處理“0”和“1”不斷變化的數據時,其位線在不斷地翻轉,此時的電流為 18.6 μA,如圖12所示.從圖12的波形中能看出,讀“0”操作相比讀“1”操作的能力弱.但是,非預充靜態隨機存儲器讀“0”和讀“1”時消耗的電流相等,而與之對比的常規8管靜態隨機存儲器讀“0”的電流比讀“1”高19%左右,所以非預充靜態隨機存儲器對讀“0”操作有19%左右的功耗優化.

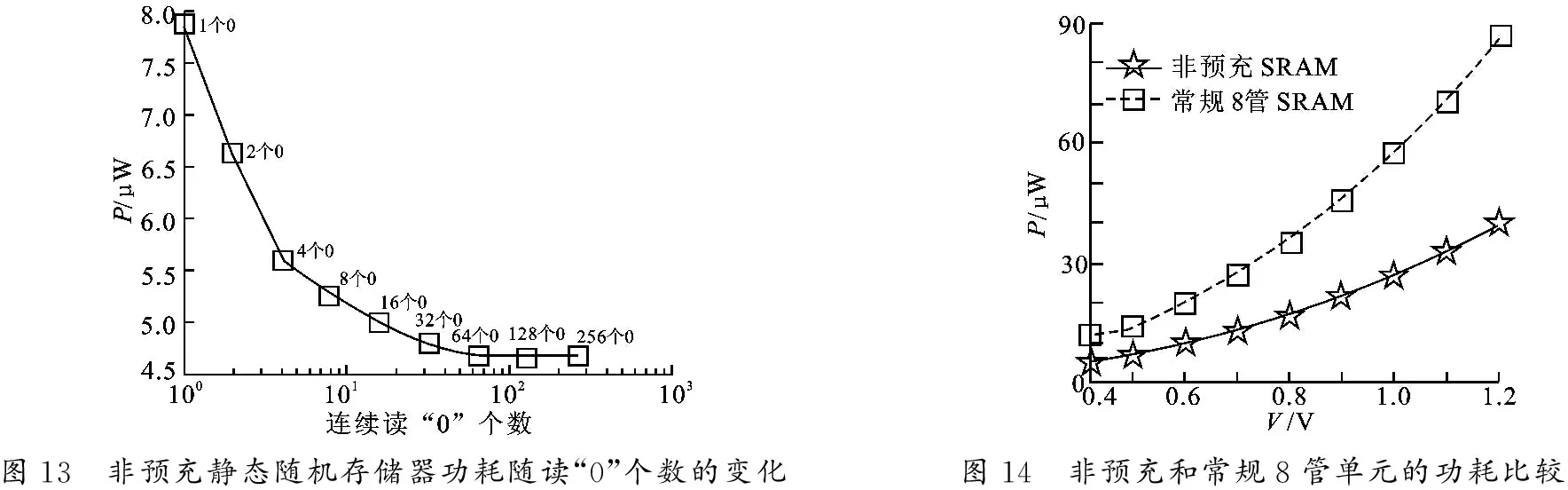

隨著讀“0”的個數增多,非預充靜態隨機存儲器的功耗逐漸降低,最終在標準測試算法(Memory Scan算法)的作用下,測試激勵中具有256個連續的“0”數據,非預充靜態隨機存儲器的功耗不斷降低,如圖13所示.

圖13 非預充靜態隨機存儲器功耗隨讀“0”個數的變化圖14 非預充和常規8管單元的功耗比較

但是,隨著連續“0”個數增多到一定程度的數量后,整體功耗不再優化.首先是因為位線長度為16個,所以優化效果不能無限增長; 其次是因為連續讀“0”的操作導致讀寫電路的功耗在整體功耗中的占比下降,此時其余電路的功耗占據主要地位,所以更多的“0”也不再會明顯地降低功耗了.但是,非預充靜態隨機存儲器消除預充機制后,其全局和局部預充電路也可以被隨之消除,與此同時,預充電路的消除也可以導致時鐘負載的降低,因此時鐘電路尺寸也可以得到進一步優化,進而使得在Memory Scan算法下,非預充靜態隨機存儲器是常規8管靜態隨機存儲器功耗的48%左右,如圖14所示.

6 結 束 語

通過發掘特定數據的特點,筆者提出非預充靜態隨機存儲器單元,消除預充機制來降低功耗.測試和仿真結果表明,非預充單元在功耗優化方面相比常規8管單元更具競爭力.同時,多閾值技術和半斯密特反相器的引入,不僅保證了單元在低電壓區域的穩定性,同時也加強了單元的讀出能力.此外,通過切斷反饋環的方式有效地提升了單元的寫能力.在SMIC 130 nm 工藝下, 非預充靜態隨機存儲器能夠穩定工作在 0.42~ 1.20 V 的電壓范圍內,功耗僅為常規8管靜態隨機存儲器的48%左右.

參考文獻:

[1] CAI J Z, ZHANGA S M, YUAN J, et al. 320 mV, 6 kb Subthreshold 10T SRAM Employing Voltage Lowering Techniques[J]. Journal of Semiconductors, 2015, 36 (6): 065007.

[2] DO A T, LEE Z C, WANG B, et al. 0.2 V 8T SRAM with PVT-aware Bitline Sensing and Column-based Data Randomization[J]. IEEE Journal of Solid-State Circuits, 2016, 51(6): 1487-1498.

[3] KIM T H, LIU J, KIM C H, et al. A Voltage Scalable 0.26 V, 64 kb 8T SRAM withVminLowering Techniques and Deep Sleep Mode[J]. IEEE Journal of Solide-State Circuit, 2009, 44(6):1785-1795.

[4] LU C Y, CHUANG C T, JOU S J, et al. A 0.325 V, 600-kHz, 40-nm 72-kb 9T Subthreshold SRAM with Aligned Boosted Write Wordline and Negative Write Bitline Write-assist[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2015, 23(5): 958-962.

[5] ATIAS L, TEMAN A, GITERMAN R, et al. A Low-voltage Radiation-hardened 13T SRAM Bitcell for Ultralow Power Space Applications[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2016, 24(8):2622-2633.

[6] WEN L, CHENG X, ZHOU K, et al. Bit-interleaving-enabled 8T SRAM with Shared Data-aware Write and Reference-based Sense Amplifier[J]. IEEE Transactions on Circuits and Systems Ⅱ: Express Briefs, 2016, 63(7): 643-647.

[7] WANG B, NGUYEN T Q, DO A T, et al. Design of an Ultra-low Voltage 9T SRAM with Equalized Bitline Leakage and CAM-assisted Energy Efficiency Improvement[J]. IEEE Transactions on Circuits and Systems Ⅰ: Regular Papers, 2015, 62 (2):441-448.

[8] CHANG I J, MOHAPATRA D, ROY K. A Priority-based 6T/8T Hybrid SRAM Architecture for Aggressive Voltage Scaling in Video Applications[J]. IEEE Transactions on Circuits and Systems for Video Technology, 2011, 21(2): 101-112.

[9] DO A T, ZEINOLABEDIN S M A, KIM T T. A 0.3 pJ/Access 8T Data-aware SRAM Utilizing Column-based Data Encoding for Ultra-low Power Applications[C]//Proceedings of the 2016 IEEE Asian Solid-State Circuits Conference. Piscataway: IEEE, 2017:173-176.

[10] NOGUCHI H, IGUCHI Y, FUJIWARA H, et al. A 10T Non-precharge Two-port SRAM for 74% Power Reduction in Video Processing[C]//Proceedings of the IEEE Computer Society Annual Symposium on VLSI: Emerging VLSI Technologies and Architectures. Piscataway: IEEE, 2007:107-112.

[11] FUJIWARA H, NII K, NOGUCHI H, et al. Novel Video Memory Reduces 45% of Bitline Power Using Majority Logic and Data-bit Reordering[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2008, 16(6): 620-627.

[12] CHIEN Y C CHIANG I H, WANG J S. Sub-threshold SRAM Bit Cell pnn forVDDminand Power Reduction[J]. Electronics Letters, 2014, 50(20): 1427-1429.

Near-thresholdnon-prechargedSRAM

CAIJiangzheng1,2,HEIYong1,2,YUANJia1,2,CHENLiming1,2

(1. Smart Sensing R&D Centre, Institute of Microelectronics of Chinese Academy of Sciences, Beijing 100029, China; 2. School of Microelectronics, Univ. of Chinese Academy of Sciences, Beijing 100029, China)

In order to save the power consumed by the static random access memory when it deals with voice or video data, a novel memory cell is proposed which eliminates the precharge mechanism in the read operation, thus suppressing the invalid power compared with the conventional 6T and 8T cell. Furthermore, multiple threshold technology is employed in the cell, which not only guarantees the read static noise margin, but also enhances read ability. In addition, a Schmitt trigger based inverter is also applied in the cell array and hence it improves the read speed. Two memories including the proposed one and the conventional one are fabricated in 130 nm process, respectively. Test results indicate that the proposed memory is excellent in reducing power consumption compared with the conventional 8T memory, and hence it becomes a suitable choice for the low power chips.

static random access memory; non-precharged; voice and video; low power

2017-02-14

時間:2017-06-29

中國科學院先導專項資助項目(XDA06020401); 國家自然科學基金資助項目(61306039)

蔡江錚(1989-),男,中國科學院微電子研究所博士研究生, E-mail:caijiangzheng@ime.ac.cn.

http://kns.cnki.net/kcms/detail/61.1076.TN.20170629.1735.038.html

10.3969/j.issn.1001-2400.2018.01.019

TN43

A

1001-2400(2018)01-0106-06

(編輯: 郭 華)