IGBT暫態實時仿真模型

馬海心 劉 健

(陸軍裝甲兵學院兵器與控制系,北京100072)

0 引言

絕緣柵雙極晶體管(IGBT)廣泛應用于600V及以上,10A以下的變流系統,如交流電機、變頻器、開關電源、軌道交通等領域。IGBT的工作狀態包括穩態和暫態,暫態過程關系到開關頻率、開關損耗、電磁特性等性能。現有仿真軟件往往將IGBT開關過程視為理想過程,不能很好地體現IGBT的暫態過程[1-2]。有的軟件模型考慮暫態過程,但實時性很差[3]。為了更好地體現IGBT的暫態過程,本文基于FPGA建立實時仿真模型。

FPGA是面向硬件電路編程的芯片,采用并行運算方式,時鐘周期可以達到納秒級。IGBT的暫態過程一般為數百納秒,進行暫態模型仿真,要求仿真步長達到納秒級,FPGA的特點符合要求[4]。本文采用Xilinx公司Spartan系列的XC3S500E芯片,該芯片時鐘頻率為50MHz,時鐘周期20ns,系統門數為50萬。該芯片豐富的硬件資源,并行化數據處理方式,靈活的接口配置,能夠滿足IGBT暫態實時仿真模型的設計要求。

1 IGBT暫態模型

在對IGBT暫態仿真模型的研究中,我們往往不關注其內部的物理特性,而只關注其外特性,因此構建IGBT功能模型[5-6]。通過對暫態過程進行分析,為下一步在FPGA中軟件實現奠定了基礎。

1.1 IGBT開通過程

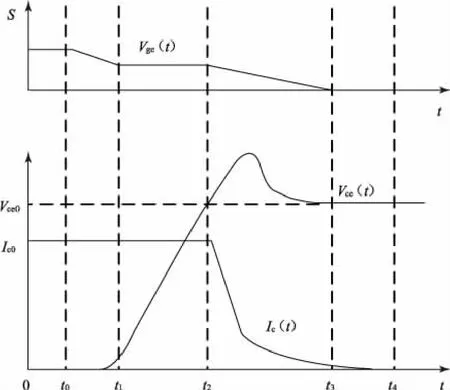

IGBT的開通過程如圖1所示。t0~t5為各個階段劃分節點,S為表示開關信號,Vge為柵極與射極電壓,Vce0為集電極與發射極在IGBT截止穩態下電壓,Vces為集電極與發射極在導通下電壓,Ic為集電極電流,Ic0為集電極在導通穩態下電流,Vth為IGBT開啟電壓。

圖1 IGBT開通過程

IGBT開通過程劃分為4個階段,對于各個階段IGBT的狀態分析如下:

階段Ⅰ(t0~t1):在驅動電源作用下,柵-射極電壓Vge開始上升,在t1時刻到達開啟電壓Vth。這個時間段內,IGBT尚未導通,集電極電流Ic為零,集-射電壓Vce為直流母線電壓Vce0。

階段Ⅱ(t1~t2):當電壓Vge繼續上升,大于開啟電壓Vth后,IGBT開始導通,集電極電流Ic逐漸增加,集-射電壓Vce隨之下降,直到t2時刻,電壓Vce變化率為零。

階段Ⅲ(t2~t3):由于米勒效應,Vce保持為平臺電壓Vcep不變,集電極電流Ic繼續增大到最大值,變化率逐漸降低為零。

階段Ⅳ(t3~t5):集電極電流Ic從最大值開始下降,在t4時刻到達導通狀態的負載電流Ic0;結電容Cgc開始放電,電壓Vce逐漸下降至零。IGBT在t5時刻進入導通飽和狀態。

1.2 IGBT關斷過程

IGBT關斷過程分為4個階段,如圖2所示。

圖2 IGBT關斷過程

各階段IGBT狀態分析如下:

階段Ⅰ(t0~t1):在t0時刻,IGBT尚處于完全導通狀態。從t0到t1時刻,柵-射極電壓Vge開始下降,電壓Vce從Vces上升至0.1Vce0,而集電極電流Ic保持負載電流不變。

階段Ⅱ(t1~t2):此階段延續階段Ⅰ的變化趨勢,Vce從0.1Vce0繼續增加至Vce0,電壓Vge進入米勒平臺;集電極電流Ic依然為負載電流,但已經進入臨界飽和階段。

階段Ⅲ(t2~t3):t2時刻開始,集電極電流Ic迅速下降,電壓Vce超越母線電壓Vce0繼續上升,形成一個電壓尖峰,并逐漸回落至Vce0。而在t3時刻,電流Ic降為0.1Ic0。

階段Ⅳ(t3~t4):t3~t4時刻,電壓Vce維持為直流母線電壓Vce0,IGBT已經關斷,只剩下拖尾電流Ic到t4時刻衰減至零,至此關斷過程完全結束。

2 軟件實現

為了便于在FPGA中實現IGBT開關的暫態模型,需要建立相應的軟件模型。由于IGBT開關過程只有幾百納秒,為了滿足仿真快速性的要求,采用了查表法在FPGA中建立模型,方法是在Matlab中對IGBT暫態過程進行仿真,提取暫態數據,保存在FPGA相應的緩存器中,仿真時根據時序信號再依次取出,并經過一系列加法器、乘法器,得到模型輸出[7-8]。

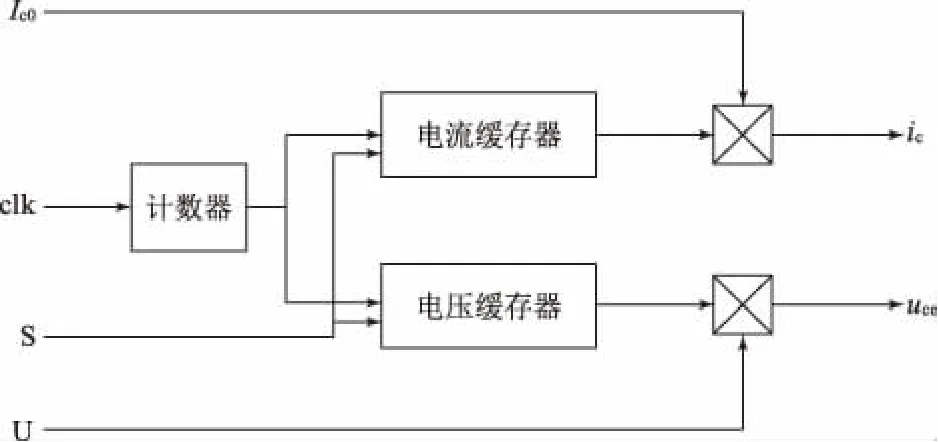

軟件模型的原理圖如圖3所示。圖中clk為時序信號,周期為20ns,FPGA中加法器和乘法器運算只需要一到兩個時鐘周期,整個模型的實時性滿足設計要求。S是開通暫態信號,S為“0”時,表示進入開通暫態;S為“1”時,表示進入關斷暫態。

圖3 軟件模型原理圖

3 實驗驗證

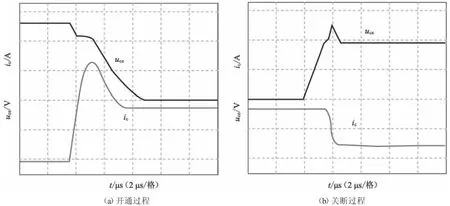

本設計IGBT采用英飛凌(Infineon)公司的FF1400R17IP4,模型數據采用工作電壓750V,集電極導通穩態電流500A時開關暫態的數據。為了方便仿真模型測試,在FPGA中產生周期為10ms的開關信號,以驅動模型運行。為了方便對模型的觀測,FPGA中的模型采用并行數據輸出,再經過外部DA轉換電路,輸出模擬信號,可以用示波器進行觀測。圖4是利用示波器檢測的模型輸出波形,與圖1、圖2對比可以發現,模型輸出電壓、電流能夠反映暫態過程的變化規律,并且實時性好。

圖4 暫態模型測試結果

4 結語

為了建立IGBT暫態的實時仿真模型,反映開關暫態的詳細信息,本文分析了IGBT的暫態過程,采用查表法在FPGA中建立軟件模型,并通過實驗驗證模型的有效性。實驗結果與設計相符合,在滿足實時性的條件下,較準確地反映了開關過程中電壓、電流尖峰,驗證了采用FPGA建立IGBT實時仿真模型的可行性,為研究IGBT暫態特性提供了一種兼顧準確度和實時性的仿真方案。