多ADC并行實時采樣方法研究

宋問遠

(中國電子科技大學自動化工程學院儀器科學與技術系,四川成都, 611731)

0 引言

通常來講,模擬波形的數字測量涉及最重要的環節之一就是對波形的采樣,其效果的好壞直接影響后續的波形重構過程和最終波形顯示。而對于波形采樣,核心環節就是模擬信號到數字量的轉換,因此,如何良好設計模-數轉換電路、實現高速準確采樣在波形的數字測量技術中至關重要。

實時采樣是在觸發信號到來后的一個周期內,連續進行采樣,一次捕獲完這個周期內信號全部波形數據的一種采樣方式。傳統的寬帶數字示波器常利用并行比較式ADC或并串比較式ADC組成高速的模-數轉換器來完成非實時的采樣,其電路設計復雜,速度慢,量化誤差大,且不能實時跟蹤波形。本文探討如何采用高速ADC芯片,分別通過延遲信號采樣和并行時間交替采樣兩種方法完成波形的實時采樣及顯示,并借助Multisim電路仿真軟件搭建電路并仿真采樣結果。

1 多ADC并行采樣原理與實現手段

1.1 多ADC并行采樣原理

將N片ADC并列在一起,用同一時鐘頻率0f驅動其工作,但每片ADC開始采樣的時間與前一片保持固定的時間差0/T N,或者信號被每片ADC采樣的位置保持固定的相位差,從而使信號輸進ADC組后在一個時鐘周期內被完全分相成N部分,進而使得采樣率從單片ADC的0f提升至N片ADC的等效采樣率0Nf。

基于這一設想,有兩種方法可以達到ADC間隔性工作的目的,分別是延遲輸入信號到達每片ADC的時間和產生時鐘間隔延遲每片ADC開始工作的時間,即信號分相和時鐘分相。

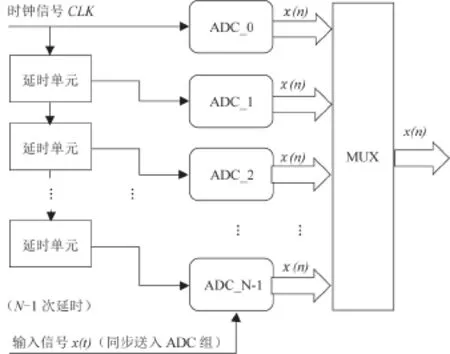

1.2 基于延遲線的延時采樣

在由N片ADC組成的采樣系統中,先將待采信號直接送入采樣通道,讓其依次通過(N-1)個精準延時單元,每個單元延時量為0/T N,即信號被均等分相成N部分。再將頻率為0f的時鐘信號同時送給N片ADC驅動其同步開始工作,對被分相后的輸入信號進行采樣。這樣,信號到達每個ADC的時刻都不相同,整個采樣系統在一個時鐘周期內可以等間隔地采到N個點,等效采樣率為N0f。

圖1 基于延遲線的多ADC并行采樣系統

1.3 并行時間交替采樣

與延時采樣原理不同的是,交替采樣將待采信號同時送入ADC組,而讓時鐘信號通過固定間隔0/T N后依次使能各ADC,從而使每片ADC在信號的不同時刻對信號進行采樣。顯然,根據運動的相對性,交替采樣和延時采樣效果相同,都可以將單片ADC的采樣率0f通過并行提升至N0f。

圖2 多ADC并行時間交替采樣系統

2 Multisim電路仿真設計及采樣結果

2.1 電路設計

2.1.1 延時采樣電路設計

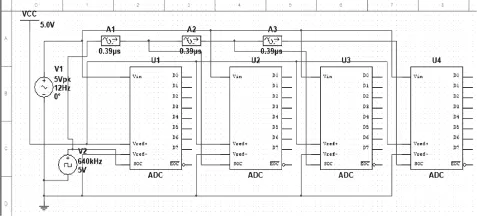

圖3 基于Multisim的信號延時采樣電路圖

圖4 基于Multisim的并行時間交替采樣

鑒于電腦軟件在空間與資源上的局限性,本仿真選擇采用4片通用8位ADC組成采樣系統,且延時單元為理想延時單元。在實際的工程運用中,ADC的選型極為重要,應從分辨率、轉換速度、精度等多方面進行考慮。總的來說,ADC可分為直接比較型和間接比較型兩大類。直接比較型,就是將輸入的采樣模擬量直接與作為標準的基準電壓相比較,得到可按數字編碼的離散量或直接得到數字量;而對于間接比較型,輸入的采樣模擬量不是直接與基準電壓比較,而是將兩者都變成中間物理量再進行比較,然后將比較得到的時間(t)或頻率(f)進行數字編碼。[1]

在本設計中,ADC的直流供電電壓為5V,被測信號為頻率12Hz、峰峰值10V的正弦波,時鐘信號頻率為640kHz。由于一個時鐘周期內要有4片ADC依次采樣,一個延時單元延時量應為時鐘周期的1/4,約0.39μs。

2.1.2 交替采樣電路設計

電路元件參數與延時采樣一致,不同的是交替采樣中被延遲的是時鐘信號。在實際工程運用中,這個時間間隔不一定用延遲時鐘的方法來實現,一般可以通過程序來控制時鐘信號進入各ADC的時間。

2.2 采樣信息的處理與波形顯示

在數字存儲示波器(Digital Storage Oscilloscope,DSO)中,經采樣系統模-數轉換后的波形數字量在觸發信號的配合下被存入存儲器。當存儲器存儲滿了后,系統則停止采集,然后從存儲器中讀出存儲的采樣數據,處理器對讀出的數據進行一系列運算和處理后,最后將處理好的數據轉換為與顯示屏對應的波形圖像,送到顯示器進行顯示。[2]

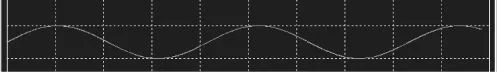

基于并行時間間隔交替采樣的方法,在Multisim中處理并顯示波形的原理為:在每個時鐘周期內,4片ADC共采集到4個不同步的波形數據,將其按采樣先后順序從高位到低位依次送入多路復用器,再經數-模轉換送入示波器進行顯示,顯示的順序應該既是實時采樣的順序,也是信號的時序。圖5、圖6分別為原始信號和采樣處理后的信號波形,可以看出,在Multisim本身無法進一步對波形進行抽樣、插值等實際DSO中必不可少的波形重構環節的情況下,單純的采樣信號就已具備了良好的顯示效果。

3 結語

本文通過對多ADC并行采樣原理的研究,探討了兩種在波形的數字測量中實現高速率實時采樣的方法——基于延遲線的延時采樣和并行時間交替采樣,并借助電路仿真軟件Multisim分別搭建了相應電路,完成了從信號采樣到波形顯示的過程,驗證了利用多ADC并行采樣的模式實現實時采樣的可行性。該模式可以克服傳統高速采集系統成本高、速度慢、對ADC芯片要求過高等缺陷,而基于該模式的實時采樣也更加容易跟蹤一些復雜任意的波形,豐富了波形數字測量技術可測的信號類型,提高了測量的整體質量。

圖5 原始信號波形

圖6 高速多ADC并行采樣信號波形