一種基于FPGA平臺的靜態高清圖像編碼系統

王 珺, 張 靚, 郭冬梅, 翁孚達

(上海無線電設備研究所,上海200090)

0 引言

原始的視覺圖像信息形式上是連續的模擬量,隨著現代計算機技術和電子技術的發展,將圖像信息投影在二維平面上,并進行離散采樣,得到以數字形式存儲和傳輸的數字圖像。由于圖像信息是高維信息(二維或二維以上),圖像信號的內容復雜,數字化后的數據量非常大,這成為圖像信息采集、存儲和信息處理的主要障礙[1]。例如,一幅分辨率為1 024×768的24位真彩色圖像的數據量約為2 MB,一張容量為4.7 GB的DVD光盤,僅能存放約2 400幅這樣的靜止圖像。那么,當水平和垂直分辨率都達到65 535的時候,一幅圖像的數據量就將達到12.9 GB,按每次處理30幅計算,需要處理的數據量達到387 GB,如果需要按照周期處理,其數據量之巨大難以想象。如此龐大的數據量對圖像的存儲和傳輸都是非常大的困難,在存儲容量和通信帶寬一定的情況下,必須對圖像進行壓縮編碼。

在圖像編碼領域,高性能的壓縮算法一直是人們不懈追求的目標,特別是在低比特率壓縮時具有低存儲量、低功耗、實時的高性能編碼算法是近幾年的研究熱點。高效圖像壓縮方法的硬件實現是圖像壓縮編碼走向應用領域的關鍵一步,其中的JPEG 2000標準是目前靜止圖像壓縮的標準中最新的也是性能最為優越的算法之一。本文基于Xilinx高性能FPGA開發平臺,實現了一種嵌入式靜態高清圖像編碼系統,以滿足大分辨率以及超大分辨率靜態高清圖像壓縮的需求。

1 系統方案

JPEG 2000技術是開發靜態圖像壓縮技術的首選。JPEG 2000壓縮算法采用離散小波變換,自適應算術編碼和優化截斷的嵌入式編碼方式,具有高壓縮比、有損壓縮和無損壓縮、感興趣區域壓縮等特點[2]。數字圖像編碼系統的硬件平臺結構如圖1所示。硬件系統主要由兩部分組成,DVI接口的FMC子卡以及Xilinx公司的VC707評估板。

DVI接口的FMC子卡具備兩路DVI接口,一路接收,一路發送,子卡采用TI公司的DVI接口芯片TFP401 A,實現解碼和編碼功能,完成并行的圖像數據和DVI接口之間的轉換,并將輸入和輸出的并行圖像數據通過FMC接口和VC707評估板相連接。

VC707評估板是Xilinx公司基于V7系列高性能FPGA的評估板,板卡采用PCIE全長板型設計,具備8x PCIE總線能力,能夠和主機通過PCIE總線完成高性能數據交互。評估板板載1 GB,64bits位寬的高性能DDR3動態存儲器模組,同時具備千兆以太網和HDMI視頻輸出接口,性能強大,適合進行各種基于FPGA的算法和接口邏輯開發驗證。圖像壓縮編碼的主要功能是在VC707評估板的FPGA上通過邏輯編程實現。除了JPEG 2000編碼模塊外,還需要其他配套的IP,比如DDR3模塊、圖像處理模塊、千兆以太網模塊等,以及相關的驅動開發,將這些模塊整合在一起,成為一個完整的圖像壓縮編碼系統。根據功能劃分,FPGA內部邏輯設計框圖如圖2所示。

FPGA是系統實現對高對比度圖像進行編碼的運算核心,FPGA內部邏輯主要包含DVI輸入模塊、數據編碼IP核模塊、DDR3 IP核模塊和千兆以太網IP核模塊。

2 系統處理流程

嵌入式數據編碼處理系統把外部的圖像信號經由子板采集后,由DVI接口模塊處理后傳送給數據編碼IP核模塊進行符合JPEG 2000標準的數據壓縮處理,并通過DDR3外部存儲空間寄存處理數據,然后將壓縮后的圖像數據通過千兆以太網傳輸到主機指定位置存儲,并通過千兆以太網主機調試程序對以太網進行配置,用戶可以使用相關開源軟件查看壓縮結果。嵌入式數據編碼處理系統的處理流程圖,如圖3所示。

(1)輸入原始圖像數據

通過DVI圖像轉換芯片TFP401A實現原始圖像采集,得到原始圖像的數字RGB信號,將數字化后的圖像數據按照期望的尺寸進行預處理,以標準格式的圖像數據流傳輸至下一級處理模塊,用于后續壓縮處理。數字RGB信號并不適用于圖像信號處理領域,需要先將RGB信號轉換為另一種圖像信號YCrCb格式,以滿足壓縮核對圖像輸入數據的格式要求。

(2)圖像數據壓縮編碼

圖像數據壓縮是整個靜態高清圖像編碼系統的核心,采用ALMA公司商用的JPEG2000壓縮核JPEG2K-E完成圖像數據壓縮編碼。在邏輯系統完成時鐘和復位邏輯后,對IP核進行相應的配置,配置內容存儲在FPGA的RAM配置文件中,通過修改這個文件可以修改相應的配置信息,完成IP核配置后就可以將圖像數據流接入壓縮核進行計算。

(3)圖像數據緩存處理

緩存數據可以集中數據進行計算,也可以避免計算產生的延時而導致數據的丟失。先將接收圖像數據信號緩存到DDR3存儲器中,從DDR3存儲器中將圖像數據順序的讀出,再以圖像數據流的形式傳遞給后級模塊。JPEG2K-E內核具備獨立數據讀取和寫入通道的外部內存接口,這使得JPEG2K-E能夠不受內存類型的局限,內存接口簡單靈活。采用Xilinx公司的MIG 7 Series IP核,進行模塊化設計,實現DDR3的數據存儲和讀取。

(4)圖像數據結果輸出

圖像數據壓縮結果通過千兆以太網輸出,采用Xilinx的IP核Tri Mode Ethernet MAC和1G/2.5G Ethernet PCS/PMA or SGMII實現千兆以太網的邏輯接口設計。針對千兆以太網的邏輯接口設計有寄存器模塊和數據傳輸模塊,其中寄存器模塊用來完成千兆以太網的配置,主要是配置源地址、目的地址以及傳輸數據長度等工作參數,最終完成將壓縮結果通過千兆以太網傳輸到主機的功能。通過主機調試程序,將壓縮后的圖像數據通過千兆以太網傳輸到主機指定位置存儲,并生成圖像文件,用戶可以使用相關開源軟件查看壓縮結果。

3 關鍵模塊簡介

圖像編碼處理以FPGA作為系統主處理器,完成圖像轉換的各種處理工作。主要負責接收主機傳送的圖像數據,解析主機傳送的控制命令,并實現相關的圖像處理和轉換工作。

3.1 DVI輸入模塊

圖像數據采集模塊從DVI接口采集圖像信號,將采集到的信號由圖像轉換芯片轉換為數字RGB信號后送給后續模塊進行預處理。TFP401A是TI公司PanelBus平板顯示產品系列中的一種TDMS信號接收芯片,應用于高速數字圖像應用場合。

TFP401A支持SXGA(1280×1024,80 Hz),像素時鐘可達112 MHz;支持24位(224=16.7 M)真彩色(1pixel/clock或2pixel/clock);采用4倍過采樣技術,抖動抑制可以達到1 pixel/clock;有同步信號抖動抑制功能[3]。

TFP401A輸出的數字RGB信號不能直接用于圖像信號處理領域,需要先將其轉換為另一種圖像信號YCr Cb格式。從RGB到YUV的色度空間的轉換為浮點運算,Xilinx公司的XC7VX485T內嵌DSP Slice,可以實現乘/除法運算,在軟件開發環境VIVADO@2016.4中,提供了RGB2YCbCr色度空間轉換的IP核,大大減少了開發時間。

3.2 數據編碼IP核模塊

數據編碼IP核模塊整個是整個嵌入式數據編碼處理系統的核心處理模塊,是完整、高性能、符合JPEG 2000(ISO/IEC 15444-1)標準的圖像編碼IP核,應用于圖像和高帶寬圖像壓縮。在外接內存控制器及內存芯片后,即可獨立完成的圖像的無損壓縮編碼功能。具體來說,其內核具有如下功能:層級移位、離散小波變換、熵編碼、失真度量與截斷長度計算、碼率控制等。該模塊接收有效像素數據后,根據設定的壓縮率,輸出符合標準協議的輸出流,完成圖像壓縮編碼,輸入圖像分辨率最大支持65 535*65 535。

該模塊通過訪問112個16位寄存器控制IP核的操作,這些寄存器配置所有的編碼選項。通過“命令寄存器”可以用來復位該IP核模塊,或者進入低功耗狀態。在編碼過程中,首先對輸入圖像進行預處理,分成小塊的圖像分量和基本的編碼單元塊。然后對每個編碼單元塊進行小波變換,將變換后的結果進行熵編碼處理。最后按照一定的碼流格式封裝數據,輸出壓縮結果。

3.3 DDR3 IP核模塊

在高速圖像處理領域,存在對數據進行高速大容量、實時性強和高帶寬的處理要求,對數據處理的速度、實時性、穩定性以及功耗等要求都越來越高。目前,在能夠同時滿足高帶寬和大容量要求的存儲器方案中,比較成熟的有DDR,DDR2以及DDR3等,其中DDR3具有更高的帶寬和更低的功耗。DDR3控制儲存模塊完成圖像數據與DDR3通信前的緩存工作,以便根據圖像在處理過程的需要,完成數據編碼IP核模塊與DDR3存儲器的讀寫工作,配合系統完成圖像編碼功能。

DDR3控制器的設計采用了Xilinx公司的IP核MIG_v2.4和用戶接口模塊的設計方法。設計中采用的內存核心頻率為200 MHz,DDR3的內存總線位數為64位,DDR3一次可以預讀取8位,根據內存帶寬=內存核心頻率×內存總線位數×倍增系數/8[4],在不考慮刷新和激活等操作所占用的帶寬下,DDR3的內存帶寬為12.8 GB/s,傳輸速率為1 600 MB/s,可以滿足數據壓縮編碼IP核對內存的存儲帶寬、存儲容量和存儲速率的要求。

3.4 千兆以太網IP核模塊

Xilinx公司的VC707評估板已經嵌入了PHY層芯片,型號為Marvell公司的M88E1111,MAC層以及MAC層與PHY層的SGMII接口均可以直接調用IP核來完成,開發周期短,正確性高。

采用Xilinx的IP核Tri Mode Ethernet MAC和1G/2.5G Ethernet PCS/PMA or SGMII實現千兆以太網的邏輯接口設計。針對千兆以太網的邏輯接口設計有寄存器配置模塊和數據輸出控制模塊,其中寄存器配置模塊用來配置源地址、目的地址以及傳輸長度等工作參數。數據輸出控制模塊主要是緩存獲取的圖像壓縮數據,按照UDP協議封裝數據包,完成數據發送。

在FPGA端發送數據時,采用乒乓FIFO可以明顯減小幀間隔。利用Wireshark觀測,當使用乒乓FIFO的情況下系統在連續發送數據時,主機每秒接收的有效數據吞吐量為812Mbps。測試結果表明,基于千兆以太網的數據傳輸可以滿足靜態高清圖像編碼系統的要求。

4 測試結果

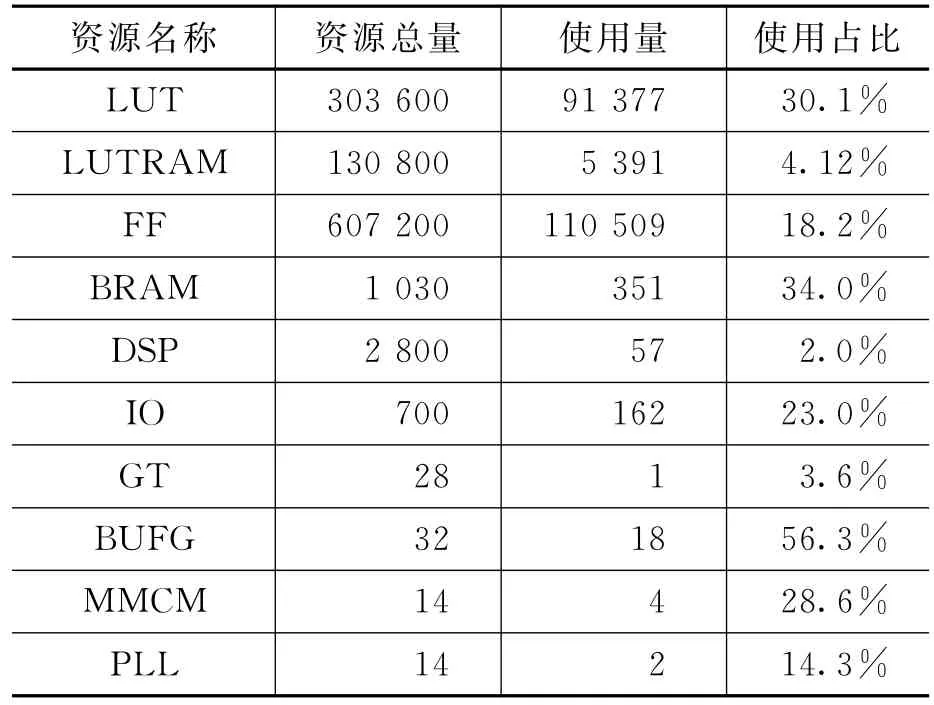

本文中實現的編碼系統以Xilinx公司的VC707評估板為硬件驗證平臺,系統綜合后的資源使用情況如表1所示。其中FF(觸發器)的使用率為18.2%,4-LUTs(四輸入查找表)的使用率為30.1%,從邏輯資源利用率來看,XC7VX485T完全能夠滿足本文所設計系統的資源消耗,并為后續升級留有資源空間。

在對整個系統進行測試時,原始圖像的分辨率為1 920×1 080,首先將經DVI采集模塊轉換后的RGB格式數據加載到圖像編碼系統;進行圖像壓縮編碼,最后將圖像壓縮結果通過千兆以太網上傳至計算機,保存為JPEG 2000格式的文件。通過實驗測試,本系統能夠實現圖像的壓縮比達到50∶1,編碼功能正確,圖像無失真。

表1 系統資源占用情況表

5 結論

本文提出了一種基于高性能FPGA的嵌入式靜態高清圖像編碼系統的設計方案,采用美國Alma公司商用JPEG2K-E IP壓縮處理技術,可實現分辨率1 920×1 080@30fps的靜態高清圖像實時壓縮編碼,采用DDR3實現數據的緩存功能,通過千兆以太網與主機完成結果數據的傳輸和存儲。實際測試結果表明,各項技術指標可以滿足靜態高清圖像壓縮編碼、傳輸和存儲的技術要求。