基于EDA技術的數字電路綜合實驗分析

西北工業大學 呂宗锠

此次研究在原電路實驗問題基礎之上提出利用EDA技術優化設計數字電路,全面提升學生對數字電路綜合應用的實驗思路。此次所研究的數字頻率計屬于MSI器件綜合應用實驗結果,按照該種試驗設計思路制定系統設計方案:基于EDA設計數字電路綜合實驗,使學生能夠更加深刻地理解和掌握課程內容,提升其學習積極性和參與度,可以應用理論知識指導實踐。

在電子信息專業課程中數字電路屬于基礎課程。數字電路實驗能夠幫助學生深入理解和掌握數字電路知識以及理論方法。現階段,我國大部分高校所開展的數字電路實驗均采用74系列器件,該種試驗器具可以幫助學生理解和掌握電路知識,然而此種試驗方法也存在弊端,無法有效聯系各個實驗之間的關系,保持學生不能掌握系統性數字電路知識,對實際應用造成影響。其次,由于受到教學內容以及課程學時的影響,導致高校所實施的數字電路實驗教學大多都是驗證性教學為主。

1 MAX+PlusⅡ軟件

該軟件主要是在微軟環境下所研制開發的可編程邏輯器件設計軟件。此種設計軟件簡單易學,容易掌握,可以推廣應用在高校教學當中。設計人員使用自身所掌握的設計方式進行軟件設計。MAX+PlusⅡ可以自動將設計方案轉化為對應,通過該軟件所包含的編程編輯功能,芯片功能以及仿真設計功能全面優化設計數字電路系統。除此之外,該軟件還能夠提供多種模型庫和器件庫,在實施電路設計教學期間能夠有利于學生掌握電路原理圖設計方法。其次,MAX+PlusⅡ軟件在數字電路分析和仿真功能方面也具有顯著優勢,可以通過時序以及邏輯功能仿真功能對數字電路進行分析,結合EDA試驗開發系統和電纜可以將設計電路上傳到EDA開發系統上,對硬件的各項性能進行測試和驗證。

2 數字頻率計實驗系統設計分析

2.1 方案設計

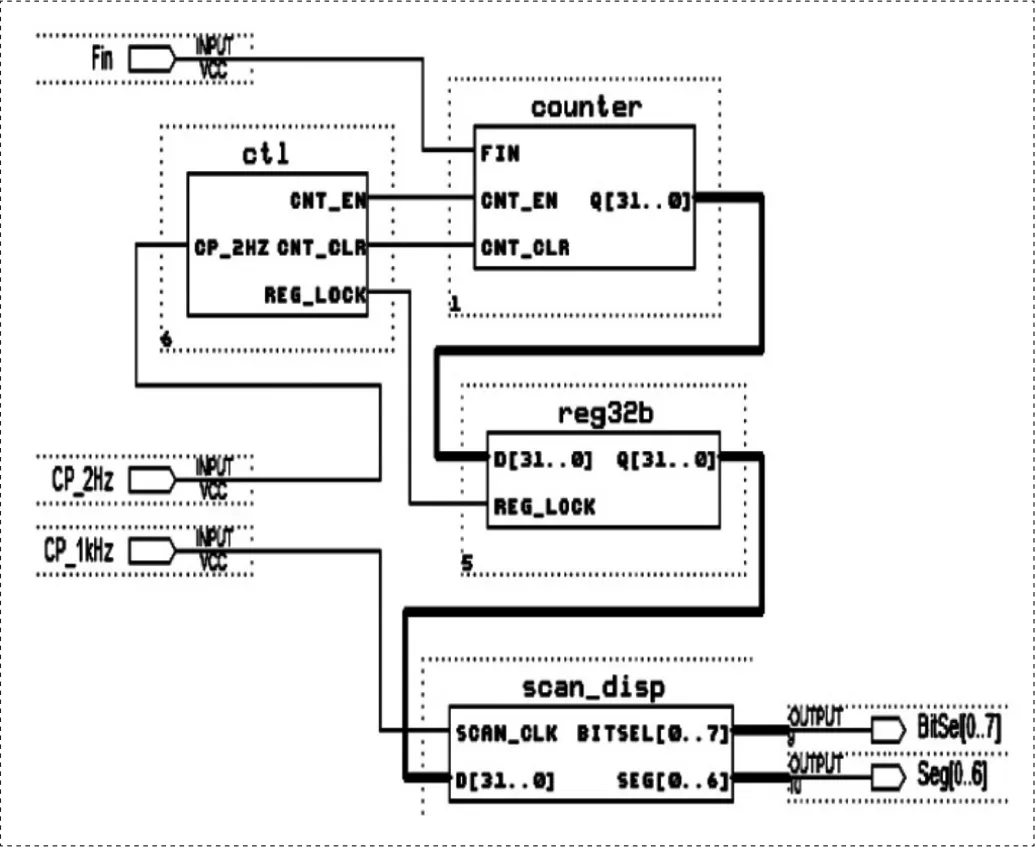

在此次實驗設計當中所應用的待測信號主要來源于信號發生器,信號幅度處于±5V波動范圍,包括矩形波,三角波和正弦波。待測信號的頻率范圍在(0.1-10MHz),所以在設計期間需要使用門電器和集成器件對數字頻率計進行設計,有效測量信號,并且可以在數碼管上以動態掃描方式顯示檢測結果,使用計數法作為頻率測量方法。按照設計要求可以將實驗系統電路劃分為脈沖發生電路、測頻控制和計數電路等,除此之外還包含動態化掃描模塊,圖1為實驗系統結構框圖和各模塊間的關系。信號整形電路的作用在于將各類波形的新華轉化為相同頻率的矩形波,這樣就能夠使時鐘脈沖信息更好地應用在計數電路中。脈沖發生電路可以提供實驗系統所需的不同頻率脈沖信號。測評控制電路的頻率能夠對控制信號進行測量,例如存儲電路信號、計數能力以及清零信號等。存儲電路和計數電路在測評控制電路控制下能夠對待測信號進行計數,可以將結果存儲到寄存器中。動態化掃描模塊可以將存儲技術結果發送到數碼管實現顯示。

為了全面展現出EDA技術實驗條件,全面縮短芯片使用時間以及設計時間。在圖1中,虛線框內部所包含的各個模塊均能夠通過實驗開發系統實現相關功能。學生可以利用信號整形和脈沖發生電路進行芯片搭建,這樣可以確保實驗內容具有較高的綜合性,并且強化學生的實際操作能力和知識應用能力。

圖1 數字頻率計結構框圖

2.2 實驗系統

(1)信號整形電路模塊。按照設計要求選擇三種待測信號波形。所以在對信號進行計數之前需要轉換波形。此次實驗系統主要采用施密特觸發器芯片變換待測信號,在變換后能夠得到矩形脈沖信號,此時就可以將其作為計數電路的輸入時鐘信號。

(2)測評控制電路模塊。數字頻率計試驗中測量頻率的方法主要為計數法。因此該模塊在實際應用期間需要自行產生脈沖信號,脈寬為1s,之后能夠在計數電路充當計數進行控制。當完成計數之后,需要在寄存器中存儲各類結果,這樣能夠保障數據顯示穩定性。自此之后可能會產生新的鎖存信號。其次,在存儲計數結果之后需要通過清零信號將計數結果清零,以便下次測量和顯示。

(3)脈沖發生電路模塊:該電路模塊屬于一種頻率信號,能夠為系統生產過程中提供必要信號,因此主要包含動態掃描電路的掃描頻率和時基信號。脈沖發生電組成部分包括若干阻容元件,晶振,二進制分頻器等。由于脈沖發生電路模塊所需時基信號為2Hz,因此對時鐘精度具有較高的要求。晶體振蕩器在應用期間的優勢主要表現在頻率穩定性方面,脈沖電路在應用期間所需的振蕩器會出現相應的信號。在經過多級分頻之后會導致信號在不同管腳輸出時鐘信號。

(4)計數電路模塊。該電路模塊能夠計量調整之后的待測信號,因此該模塊的組成主要包括十進制加法計數器,應用同步級聯方式。測評控制電路輸出信號可以對計數的開始和暫停進行控制。在存儲計數結果之后,測評控制電路會產生清零信號,此時可以全部清零所有計數器,為下次計數做好準備。

(5)鎖存電路模塊。該電路模塊的作用在于存儲計數電路的結果,其所具備的清零信號觸發器能夠同時并聯多個時鐘,之后由測頻對電路輸出信號進行驅動控制。計數后測評控制電路會輸出多個計數器結果,并將其存儲在寄存器當中。

(6)數字頻率計整體電路。在完成電路模塊設計之后,需要根據框圖對電路進行設計組裝,在設計路模塊之后,按照相應的組成框圖組裝設計電路,可以得到圖2所示的整體電路圖。在該電路圖中,虛線框中主要包括存儲電路,計數電路,測評控制電路和動態掃描顯示電路等。

圖2 數字頻率計整體電路圖

3 硬件驗證和軟件仿真

3.1 軟件仿真

MAX+PlusⅡ軟件的分析能力和仿真能力都比較強大。在設計期間首先需要優化設計功能模塊,之后利用MAX+PlusⅡ仿真工具對所設計的電路進行邏輯仿真,驗證設計準確性。與傳統設計技術相比,此種仿真功能也屬于EDA技術的重要優勢。按照圖3動態掃描顯示電路仿真波形圖可以看出,此次設計的電路能夠實現預期所設定的功能,并且模塊仿真與此設計比較類似。

圖3 動態掃描顯示電路仿真波形圖

3.2 硬件驗證

在對整體電路和不同模塊實施仿真驗證后,可以通過引腳鎖定電路輸出和輸入端口;利用下載電纜優化設計電路,將優化結果上傳到EDA試驗開發系統上。該系統在接收到信號發生器所傳輸的脈沖電路時基待測信號,就可以對設計電路硬件功能實施驗證。在驗證過程中能夠發現,該數字頻率計能夠實現穩定運行,并且滿足預期效果。

4 結束語

綜上所述,利用EDA技術開展數字電器綜合試驗屬于現代化數字電路實驗方法。在教學期間所應用的數字電路綜合實驗模式需要充分發揮出EDA技術作用,利用數字電路課程設計實驗過程,包括設計方法和單元電路。所以,此種模式可以在較大程度上使學生應用所學知識解決。實際問題,幫助學生深入了解和掌握電路設計方法和操作步驟,全面提升學生實際操作能力。