P基于I2S接口的FPGA的音頻數據傳輸

林 嘉 陳素瓊 蘇凱雄

?

P基于I2S接口的FPGA的音頻數據傳輸

林 嘉 陳素瓊 蘇凱雄

(福州大學物理與信息工程學院,福州 350108)

4K原始數據轉換成4路3G-SDI,需對音、視頻進行分別處理。本文設計了一種I2S音頻數據處理電路,以I2S協議為基礎,使用HV2芯片和FPGA開發板,實現I2S音頻數據的傳輸,解決跨時鐘域傳輸數據的問題。利用CTS生成器改善電源抑制,降低輸出抖動和噪聲性能。仿真測試表明音頻數據能夠被完整的傳輸。

I2S協議;FPGA;HV2芯片;跨時鐘域;CTS生成器

4K電視[1]畫面質量明顯提升,已經成為當今電視的主流發展方向。電影電視工程師學會(SMPTE)定義了4K視頻傳輸的SDI接口。

原始的4K音頻數據無法直接被SDI接口[2]利用。本文基于SMPTE協議[3],利用FGPA開發板[4]進行數據轉換和處理,再插入視頻數據流中。I2S協議[5]能夠將數據信號和時鐘信號分開傳輸,避免了時差誘發的失真,故采用I2S協議制作音頻接口。

1 I2S協議

I2S(inter-IC sound bus)是飛利浦公司為數字音頻設備之間的音頻數據傳輸制定的一種總線標準,既規定了硬件接口規范,也規定了數字音頻數據的格式。

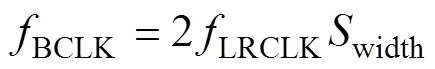

如圖1所示,對應數字音頻的每一位數據,BCLK(串行時鐘)都有1個脈沖。LRCLK(幀時鐘)是應用于變更左右聲道數據的時鐘,其頻率等于采樣頻率。LRCLK必須與BCLK保持同步,兩者的關系為

式中,是采樣位數。在I2S接口中傳輸的有效數據稱為SDATA(串行數據),通常用二進制補碼表示。

2 I2S接口硬件設計

利用HV2芯片接收并處理音頻數據。HV2芯片是由socionext研發的影像接口轉換器,主要用于2~4K視頻數據的轉換,并能處理與傳輸I2S音頻數據[6]。HV2處理后的I2S音頻數據對應于不同的聲道進行音頻數據傳輸,再由FPGA的I2S模塊接收。

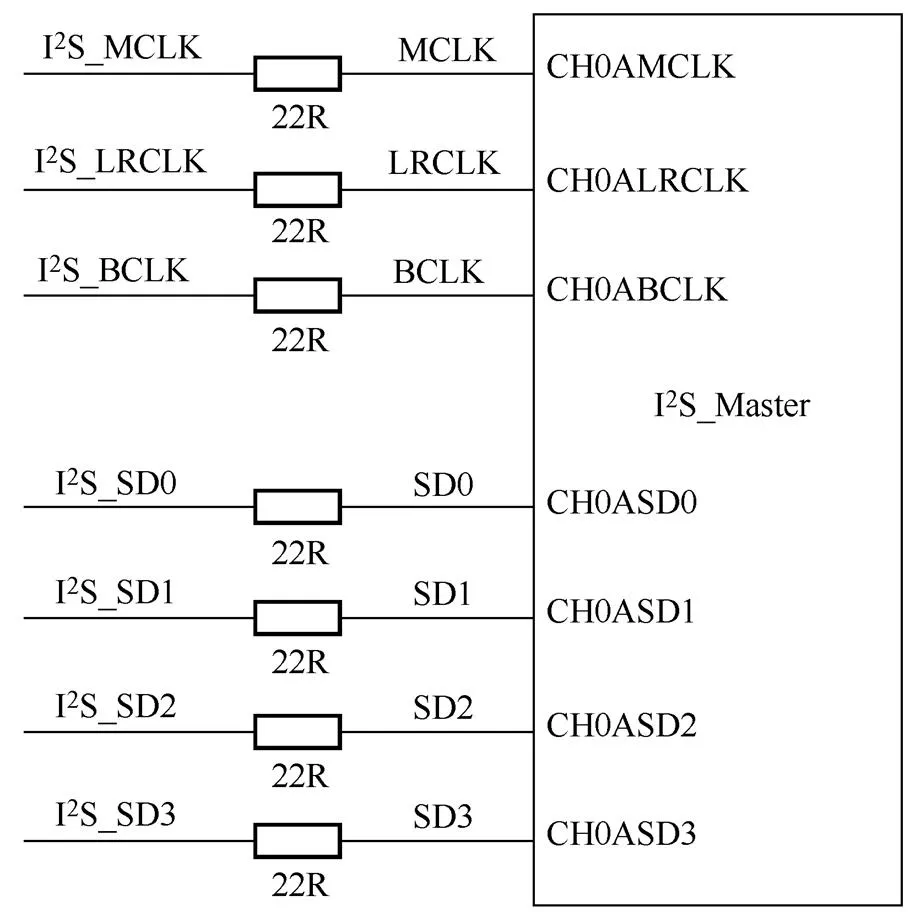

本文將HV2的采樣時鐘設定為48kHz,同時規定LRCLK的高電平表示傳輸的是左聲道,低電平表示傳輸右聲道,并設定傳輸數據的最大數據位寬為32bit。實際測試中只接收到24bit數據。根據I2S協議,在數據傳輸過程中,若LRCLK的單次脈沖寬度不能將需要傳輸的全部bit數據完整傳輸,則截斷低位的bit數據,而在完整的bit數據傳輸完成之后,LRCLK的周期還沒有結束,則系統會在低位處自動補齊。故在配置輸出時設置位寬32bit,可避免將尾部的bit數據截斷,從而傳輸完整的bit數據。SDATA數據線上的有效數據也是24bit。時鐘頻率是由HV2中的晶振產生并控制,LRCLK為48kHz,而BCLK為3.072MHz。如圖2所示,4路串行數據線I2S_SD0、I2S_SD1、I2S_SD2和I2S_SD3分別對應著不同方位的聲道,從而傳輸7.1立體聲音頻。

圖2 I2S電路設計圖

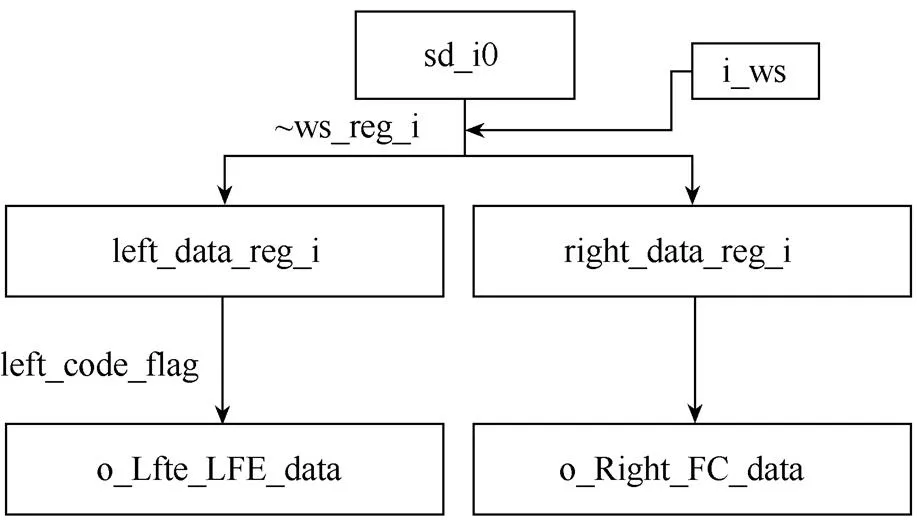

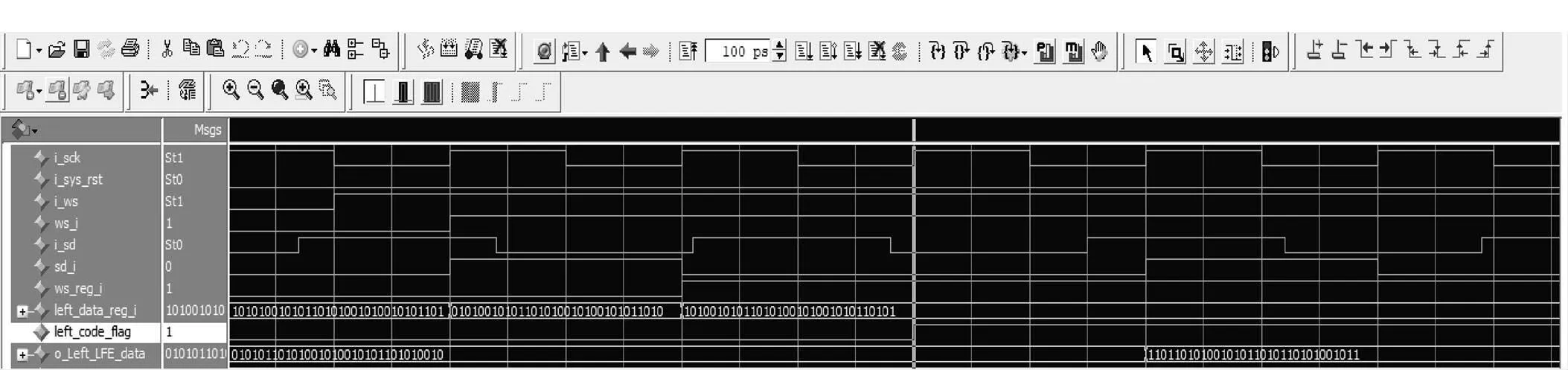

如圖3所示,傳輸sd_i0的數據,經過i_ws左右聲道選擇,并經過數據拼接和補碼轉換最終得到o_Left_LFE_data和o_Right_FC_data。ws_reg_i和left_code_flag是標志位,根據其狀態判斷當前是否需要進行數據拼接和補碼轉換。

圖3 I2S數據的傳輸

3 在FPGA中傳輸音頻數據

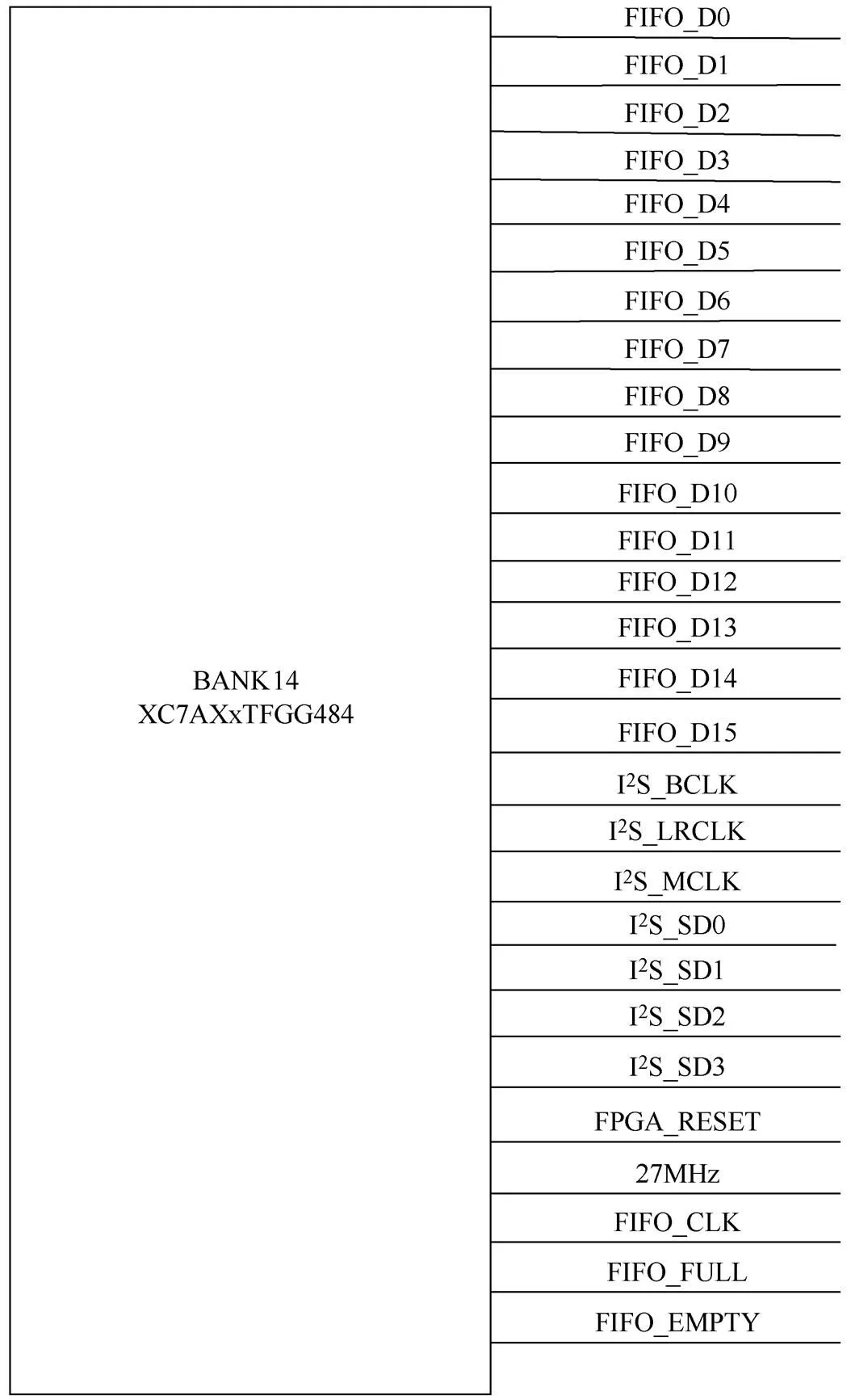

本文所用的FPGA開發板是代號為XC7A50T- 3FGG484的芯片(以下簡稱“X3芯片”),能夠實現音視頻的接收、發送等功能內嵌I2S模塊。X3芯片的核心邏輯功能電壓是2.5V,I/O端口的電壓是3.3V,滿足HV2數字端口的所規定電平的要求。如圖4所示,圖中既標識了I2S接口的引腳信息,也標記了FIFO的引腳信息。FIFO_D0至FIFO_D15、FIFO_FULL和FIFO_EMPTY用于測試異步FIFO跨時鐘域的空滿狀態,根據不同狀態將進行不同的 反饋。

圖4 FPGA的硬件連接圖

設計中FPGA的音頻接收模塊,其內部時鐘是27MHz,而HV2的內部時鐘為3.072MHz,導致接收和發送處于不同的時鐘域,使得這些域中的動作間沒有關聯性,無法完成同步,系統循環進入亞穩態[7]。為減少亞穩態的影響,應對跨時鐘域問題的進行處理。異步FIFO[8]能實現大量數據的跨時鐘域傳輸,并保證較高的數據傳輸速度。

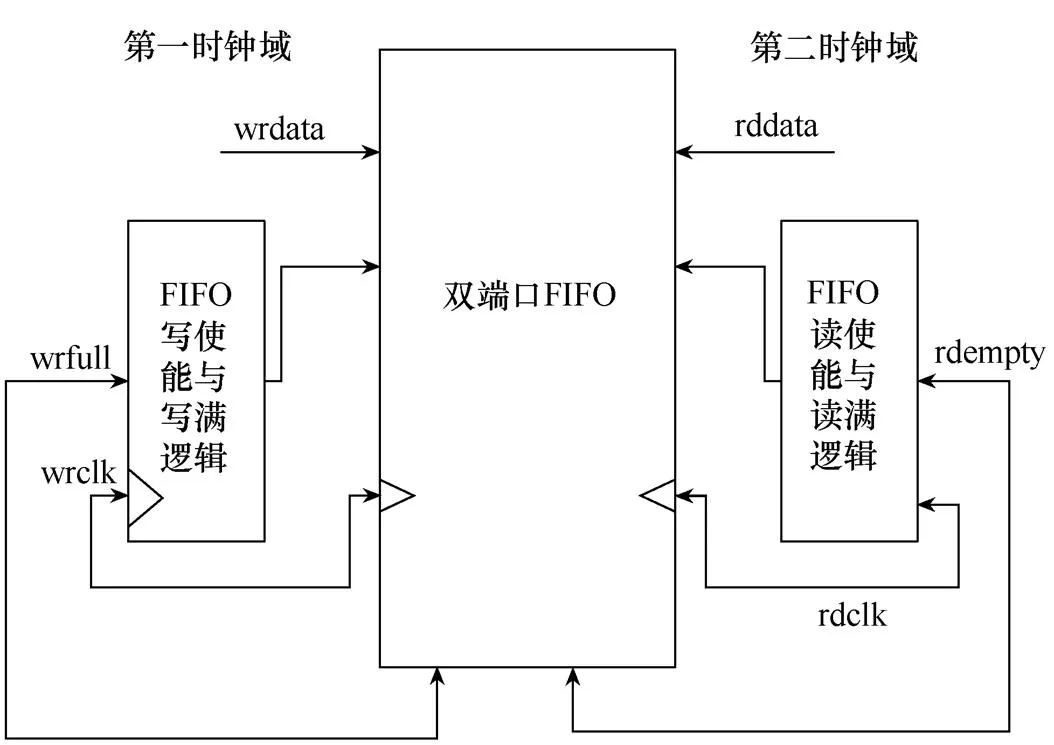

如圖5所示,本設計中采用雙端口存儲器RAM[9]來緩存系統數據,并設定其數據寬度為32bit,深度為1024bit。讀、寫控制端分別控制wrdata(寫入)信號與rddata(讀出)信號,利用wrfull(寫滿)和rdempty(讀空)標志轉換這兩個不同時鐘域的運行狀態。在異步FIFO的設計中,關鍵環節之一是檢測并判斷緩存器是否產生wrfull或者rdempty信號。不同的時鐘域提供不同的時鐘信號,當寫控制器接收到寫請求信號時,相應的wrcontrol(寫控制)信號隨之產生,此時指針也指向將寫入數據的地址。在數據寫入的過程中,不斷檢測FIFO緩存器是否已經寫滿。若未寫滿,則繼續傳輸數據;否則產生wrfull信號反饋給FIFO緩存器。當讀控制器接收到讀請求信號時,相應的rdcontrol(讀控制)信號隨之產生,此時指針指向將讀出數據的地址。在數據不斷讀出的過程中,檢測FIFO緩存器是否已經讀空。若未讀空,則繼續讀出數據;否則產生rdempty信號反饋給FIFO緩存器。

圖5 異步FIFO結構框圖

格雷碼具有循環特性和單步特性,當用其表示一個連續變化的數值時,僅有一個位會翻轉,因此大幅度的降低位翻轉的頻率,從而保證傳輸的穩定性,減少傳輸誤碼率,故在實際操作中指針地址使用格雷碼表示。正是利用了這一特點,使得能減少亞穩態的產生概率[10]。

為說明如何得到寫滿和讀空信號,以位寬為8bit,深度為16bit為例,如圖6所示。此處要設置addr(地址信號)為5bit,當讀地址指針的速度高于寫地址指針時,則兩個指針會在某一時刻指向同一個值,意味著已經讀空數據,將產生rdempty信號,此時w_addr=r_addr。而當寫地址指針循環一次并追上讀地址指針時,此時w_addr[4]與r_addr[4]相反,w_addr[3:0]=r_addr[3:0],表示已寫滿數據,產生wrfull信號。wrfull信號有效并反饋給系統時,系統將停止寫入數據;rdempty信號有效并反饋給系統時,系統將停止讀取FIFO的數據,如此就能夠保證數據的正確穩定的傳輸。

圖6 讀空寫滿標志信號的產生

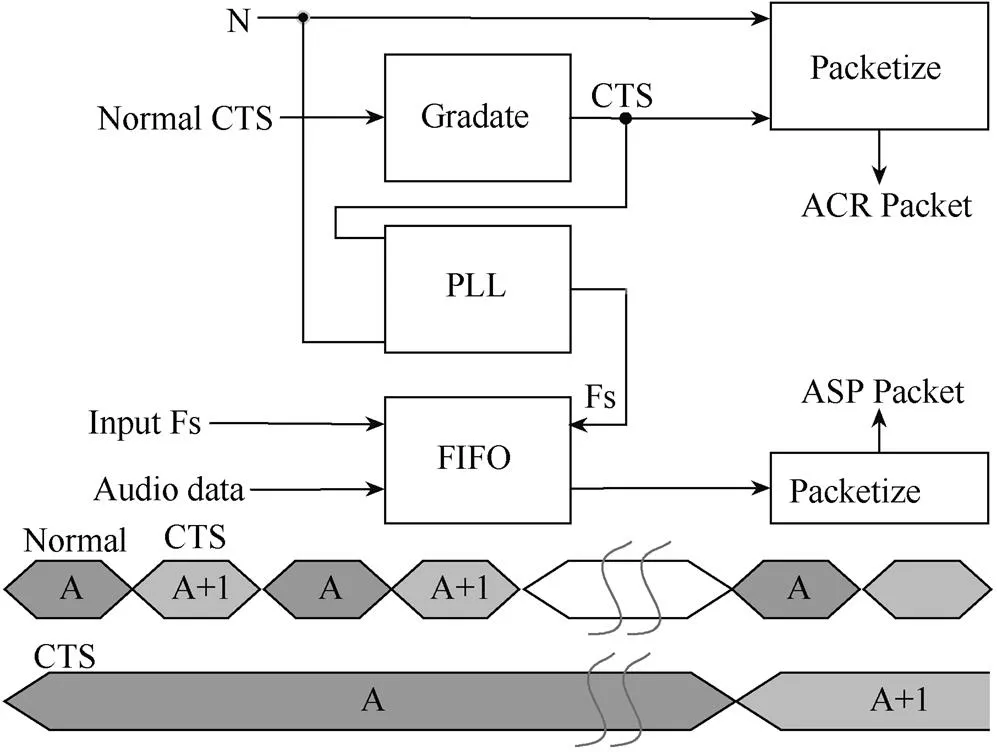

在傳輸音頻數據時,為了能改善電源抑制,降低輸出抖動和噪聲性能,加入了一個CTS(cycle time stamp)生成器。在LSI(大規模集成電路)上有發射器TX Pure CTS和接收器RX Pure CTS。通過調節TX ACR(audio clock regeneration)分組和RX ACR分組的CTS的變化來減少音頻時鐘抖動。

如圖7所示。原始的CTS經過發生器產生新的CTS,并封包成ACRPacket。CTS與NormalCTS有明顯區別,CTS的變化周期變長,減少音頻時鐘抖動。ACR數據包是音頻時鐘再生數據包,這是控制FIFO傳輸之后的時鐘域的標準時鐘。而輸入的Fs(參考信號)用于調節鎖相環內部振蕩信號的頻率和相位,并將信號傳入FIFO中,使音頻數據封包成為ASP(audio sample packet)。封包輸出的ASP將與HBASP(high bitrate audio stream packet)共同組成完整的音頻數據包[11]。

圖7 TX Pure CTS發生器的框圖和信號圖

4 仿真結果

音頻模塊的仿真是調用了vivado的庫并在modelsim中實現的。仿真過程中,i_sck的周期為20000ps,i_sd的周期為34000ps。而從圖8中可知,對應每個i_sck的上升沿所采樣的i_sd數據都能準確的獲取,所得到的數據對應于sd_i數據。說明I2S接口可以準確的接到收HV2傳來的音頻數據。當ws_reg_i為低電平時,left_data_reg_i從10101001010110101001010010101101到010100101 01101010010100101011010再到1010010101101010 0101001010110101,每一次數據采樣之后,二進制編碼均舍棄最高位bit,在最末位拼接所采樣的bit,可知數據能夠正確拼接。當left_code_flag為高電平時,o_Left_LFE_data為11011010100101011010110 101001011,與10100101011010100101001010110101對比,除首位與末尾,其余均是取相反數,即說明能正確得到補碼。

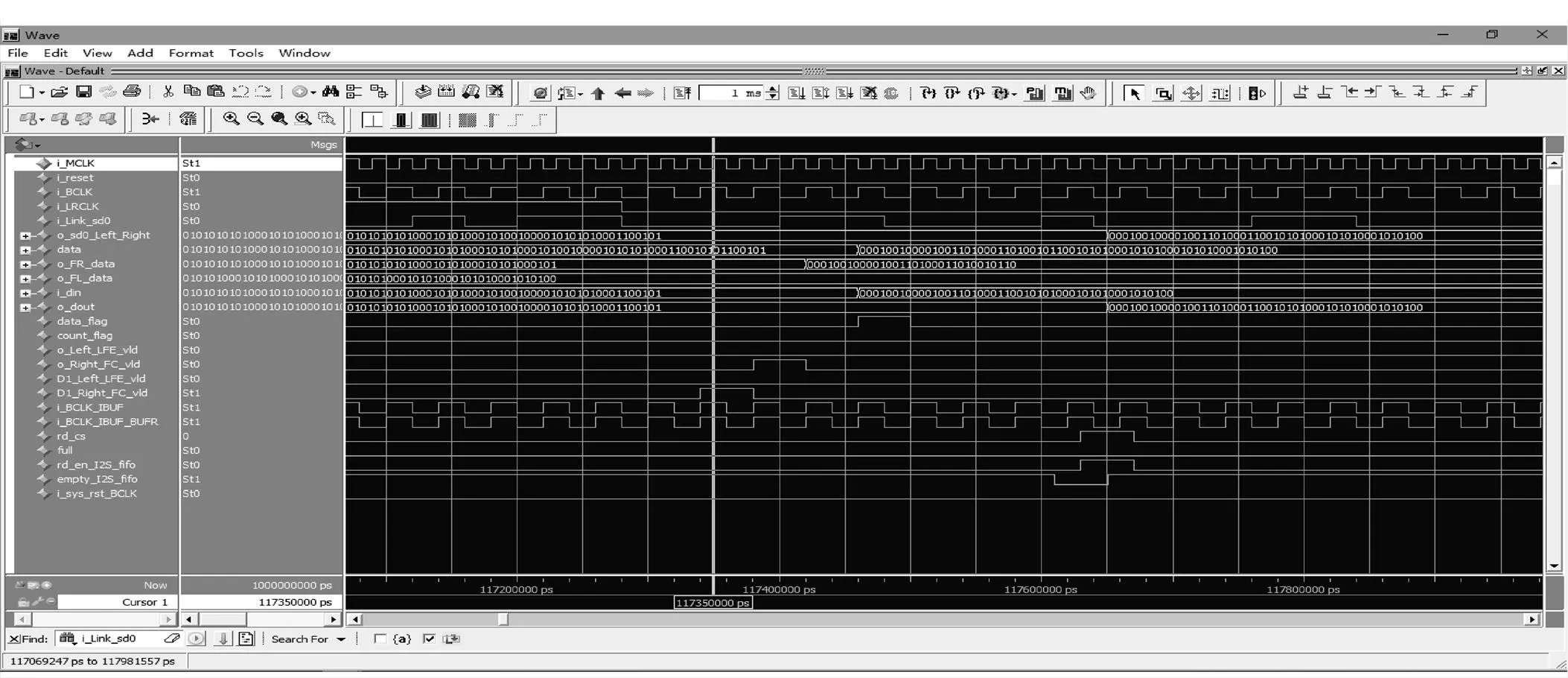

用發送和接收文本文件的方法驗證數據是否發送正確。如圖9所示,o_FR_data傳輸32bit左聲道數據,而o_FL_data傳輸32bit右聲道數據,兩者均是攜帶24bit有效數據并在其后拼接8bit無效數據。data則是左右聲道串行之后形成64bit數據用于傳輸。而o_sd0_Left_Right是左右聲道各截斷了末尾的8個位數之后的拼接數據,輸出o_sd0_Left_Right,便能得到完整的有效數據。

圖8 I2S接口接收數據仿真圖

圖9 FPGA中發送數據的仿真圖

5 結論

本文為了解決I2S音頻數據的傳輸、跨時鐘域問題,同時改善電源抑制、降低輸出抖動和噪聲性能。選擇HV2芯片、X3芯片和CTS生成器,以支撐本文所涉及的硬件設計部分。對如何利用I2S接口在兩個芯片間進行音頻數據的傳輸以及如何解決跨時鐘域的數據傳輸給出了基本的方案和流程。仿真驗證了數據能正確穩定地傳輸。用于本次實驗的設備也將投入市場,實用價值和參考價值都將得以體現。

[1] 張翔. 4k電視技術應用及發展研究[J]. 信息通信, 2016(7): 302-304.

[2] 張悅. 高清SDI顯示單元的設計與實現[D]. 成都: 電子科技大學, 2017.

[3] 賈宏君, 李曉宇. 2016年SMPTE電視技術標準化跟蹤研究[J]. 廣播與電視技術, 2017, 44(3): 155-160.

[4] 張圣超, 佘洪波. 基于FPGA的增量式編碼器接口電路的設計[J]. 電氣技術, 2014, 15(1): 38-41.

[5] 趙海亮, 李琦. 一種I2S音頻數據處理電路的FPGA設計[J]. 桂林電子科技大學學報, 2016, 36(6): 461- 465.

[6] SMPTE. Image Format and Ancillary Data Mapping for the Quad Link 3Gb/s Serial Interface: ST 425-5: 2015[S].

[7] 王利祥. FPGA設計中跨時鐘域的問題與方法[J]. 電子技術與軟件工程, 2017(24): 97.

[8] Ball, Stuart. Embedded Microprocessor Systems: Real World Design[M]. Butterworth-Heinemann, 1996.

[9] 李盛杰, 張碚, 顧穎. 雙端口靜態存儲器測試方法研究[J]. 計算機與數字工程, 2015, 43(1): 83-86, 112.

[10] 金大超, 冷建偉. 異步時鐘域信號同步的實現[J]. 天津理工大學學報, 2017, 33(3): 40-44.

[11] 齊娜, 鄒峰. HD-SDI嵌入音頻數據分析[J]. 廣播電視信息, 2014(12): 49-51.

Audio data transmission of FPGA based on I2S interface

Lin Jia Chen Suqiong Su Kaixiong

(College of Physics and Information Engineering, Fuzhou University, Fuzhou 350108)

In the experiment of converting 4K raw data into 4 channels of 3G-SDI, audio and video should be processed separately. An I2S audio data processing circuit is designed. Based on the I2S protocol, an HV2 chip and an FPGA development board are used to implement the transmission of I2S audio data, and the problem of transmitting data across clock domains is solved. Use the CTS generator to improve power supply rejection and reduce output jitter and noise performance. Simulation tests show that audio data can be transmitted completely.

I2S protocol; FPGA; HV2 chip; cross clock domain; CTS generator

2018-06-05

林 嘉(1992-),男,福建省寧德市古田縣人,碩士研究生,主要從事視頻編碼、通信技術的研究工作。

福建省省部級重大項目(2015H6014)