基于FPGA的多通道FIFO存儲控制器的設計與實現

呂達 張加宏 李敏 冒曉莉 楊天民 謝麗君

關鍵詞: FIFO; 有限狀態機; Verilog HDL; ModelSim; FPGA; 存儲控制器; 輪詢時間; 資源利用率

中圖分類號: TN830.3; TP302; TP332 ? ? ? ? ? ? ? 文獻標識碼: A ? ? ? ? ? ? ?文章編號: 1004?373X(2019)04?0001?04

Design and implementation of multi?channel FIFO memory controller based on FPGA

L? Da1, ZHANG Jiahong1,2,3, LI Min1,3, MAO Xiaoli1,3, YANG Tianmin1, XIE Lijun1

(1. School of Electronics and Information Engineering, Nanjing University of Information Science & Technology, Nanjing 210044, China; 2. Jiangsu Collaborative Innovation Center of Atmospheric Environment and Equipment Technology, Nanjing University of Information Science & Technology, Nanjing 210044, China;

3. Jiangsu Key Laboratory of Meteorological Observation and Information Processing, Nanjing University of Information Science & Technology, Nanjing 210044, China)

Abstract: A multi?channel FIFO memory controller is designed to solve the conflict problem occurring when multiple functional modules access the same memory unit simultaneously. The work principle of the controller and the architecture design of the system are given. The finite state machine (FSM) and Verilog HDL language are used to design various modules. The pre?simulation and post?simulation are completed by using the ModelSim. The board unloading function verification is completed on the Xilinx FPGA platform. The practical results show that the memory controller can maximize the memory access efficiency on the premise of ensuring no access conflicts occur, provide an easy?to?use user interface, and easily define parameters such as the number of channels and the polling time of each channel according to the specific application, thereby achieving the highest resource utilization rate.

Keywords: FIFO; finite state machine; Verilog HDL; ModelSim; FPGA; memory controller; polling time; resource utilization rate

0 ?引 ?言

FPGA在對實時性要求高而且數據流量大或者算法復雜度高的應用場合中使用越來越廣泛[1]。而FPGA的應用一般都會涉及對外部存儲單元數據存儲和讀取問題,所以設計一款接口簡單易用、訪問效率高、性能穩定的存儲控制器至關重要[2?4]。目前存儲控制器廣泛采用LocalLink接口總線。該接口總線由寫入數據線、讀取數據線、地址線、指令線和握手信號線組成。其中握手信號線包括local_ready和local_valid。local_ready用于通知外部模塊該控制器處于空閑狀態,此時外部模塊可對該控制器發送讀/寫請求。local_valid用于通知外部模塊數據可用,此時外部模塊可從讀取數據線上取走數據[5]。采用LocalLink接口總線的存儲控制器擁有設計難度低、使用簡單等優點的同時也存在以下不足:首先,不支持多個外部功能模塊同時訪問同一個控制器下掛載的存儲單元,外部多個功能模塊必須分時使用同一控制器,這就給外部功能模塊之間的協調帶來了困難,甚至造成存儲訪問沖突;其次,握手過程需占用時鐘周期,這就導致了存儲器訪問效率低下問題;最后,由于不帶數據緩沖,該存儲控制器只能應用在數據流量相對穩定的場合。

本文設計帶FIFO的多通道存儲控制器,使得多個外部功能模塊通過不同通道可以互不干擾地訪問同一存儲器單元[6]。外部模塊可以在任何時候將指令、數據和地址寫入FIFO或者從FIFO中讀取數據,而不需要等待該控制器空閑,也無需等待數據可用,提高了存儲器訪問效率。通過設置FIFO深度以滿足不同的突發訪問要求。對于數據流量相對穩定的應用,可設置較小的FIFO深度以節省FPGA資源,而對于短時間內存儲器訪問量大的應用,則設置較大的FIFO深度,以防止數據遺漏。本文以ST公司的M25P64 NORFLASH為例,詳細闡述了帶FIFO的多通道存儲控制器設計過程。前仿真和后仿真使用Micron公司提供的M25P64仿真模型,最后在基于Xilinx公司的FPGA芯片XC6SLX45和在線邏輯分析儀ChipScope下板驗證和測試。

1 ?系統設計

1.1 ?架構設計

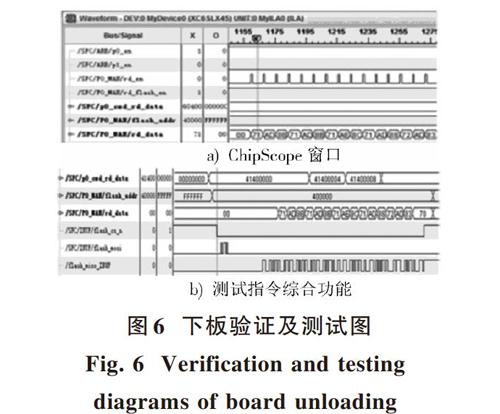

本文設計的帶FIFO的多通道存儲控制器以SPI接口NORFLASH為示例,主要論述各通道仲裁和管理機制以及設計方法,而不是針對SPI接口NORFLASH的讀/寫過程展開敘述。圖1是帶FIFO的四通道存儲控制器系統架構簡圖。其中通道0和通道1只支持讀指令,通道2和通道3只支持寫指令和擦除指令。

圖1中PLL是鎖相環模塊,其不僅負責提供該控制器的系統時鐘,還負責提供外部存儲器時鐘flash_clk、FIFO時鐘fifo_clk以及外部存儲器數據捕獲時鐘cap_clk。各時鐘為同頻率異相位關系,具體各時鐘的相位關系在后仿真中初步確定,在下板驗證中最終確定。仲裁器的作用是決定各通道是否使能、控制多路器和清零輪詢計數。輪詢計數器用于記錄每個通道輪詢時間。指令FIFO用于存放指令數據。讀FIFO用于緩存控制器已經從外部存儲讀取到的數據。寫FIFO用于緩存用戶將要寫入外部存儲器的數據。讀管理器和寫管理器分別負責各自通道指令譯碼、執行操作和信號反饋等。

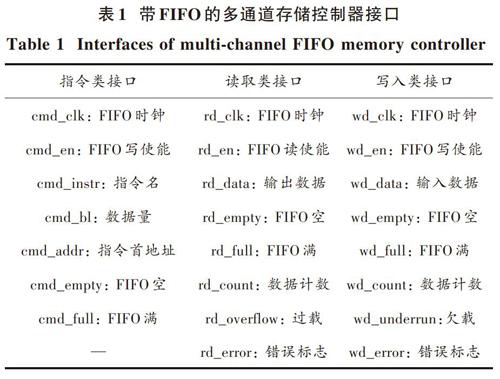

本文設計的存儲控制器接口簡單而高效。表1列出了該控制器的接口總線,通道0和通道1包括所有指令類接口和讀取類接口,通道2和通道3包括所有指令類接口和寫入類接口。

1.2 ?仲裁器設計

仲裁機制采用時間片輪轉方式,具體過程如下所述:首先,仲裁器在將輪詢計數器清零后使能通道0管理器并設置對應多路器;然后,通道0管理器開始執行操作,當通道0管理器檢測到輪詢計數器計數值超出預設值,也即時間片消耗完,向仲裁器發送完成信號;最后,仲裁器收到通道0完成信號后,關閉通道0,并將輪詢計數器清零后使能下一個通道,依次循環,達到各通道合理訪問外部存儲單元的目的。

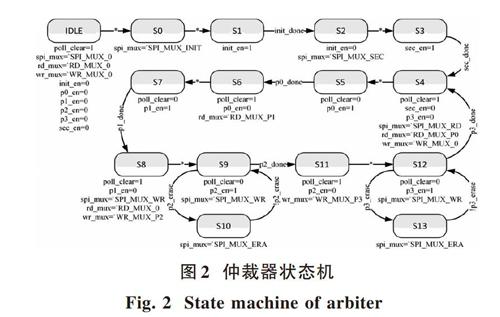

仲裁器的作用是協調各個通道對外部存儲單元的訪問請求,不但控制多路器和各通道管理器,還負責控制初始化模塊和安全模塊。仲裁器狀態機如圖2所示,存儲控制器系統復位后,由IDLE狀態進入S0狀態,將多路器選擇為初始化模塊,隨后進入S1狀態,使能初始化模塊并獲得外部存儲芯片ID。當初始化完成后進入S2狀態,將多路器選擇為安全模塊,隨后進入S3狀態,使能安全模塊,安全模塊根據初始化模塊獲得的ID進行安全校驗。安全校驗不通過仲裁器鎖死在S3狀態,否則進入S4狀態,S4狀態中將多路器選擇為讀模塊并清零輪詢計數器,隨后進入S5狀態,使能通道0管理器。當收到通道0管理器反饋的完成信號后,進入S6狀態,關閉通道0管理器并清零輪詢計數器,隨后進入S7狀態,使能通道1管理器。如此依次執行通道1、通道2和通道3操作,當收到通道3管理器反饋的完成信號后,再次進入S4狀態。

1.3 ?讀管理器和寫管理器設計

讀管理器和寫管理器除了具備指令譯碼,執行操作和信號反饋等基本功能外,為了滿足更苛刻的輪詢時間要求和優化執行效率,還具備指令拆分和指令綜合功能。指令拆分功能表述如下:當某一條指令需要讀取的數據較多,執行時間超過一個輪詢時間片時,為了不占用其他通道的輪詢時間,必須暫停該條指令,為其他通道讓出使用權。指令綜合功能表述如下:為了提高讀取數據的效率,將多條地址連續的讀指令合并成一條讀指令,而節省重復發送指令碼、訪問地址的時間。

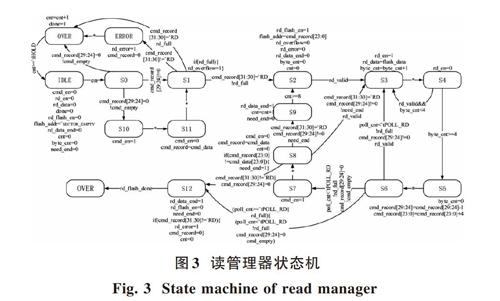

讀管理器的狀態機如圖3所示,在S0狀態中判斷cmd_record[29:24]數據量是否為0。數據量為0表示在上一次輪詢該通道時遺留下未完成的指令,此時跳轉到S1狀態;如果不為0且指令FIFO不為空,則進入S10,如果數據量為0而指令FIFO為空則進入OVER狀態。S10和S11是從指令FIFO中讀取新指令的過程,完成后同樣進入S1狀態。S1狀態中首先判斷指令名是否合法,如果不合法進入ERROR狀態,合法則判斷讀FIFO是否已經被寫滿,寫滿將rd_overflow拉高并進入OVER狀態,未寫滿進入S2狀態。S2~S5狀態是讀取4 B數據并更新cmd_record的過程,完成S5后進入S6狀態。在S6狀態中首先檢查輪詢計數器是否大于等于預設值或者讀FIFO是否為空,如果計數器大于預設值或者讀FIFO為空,則進入S12狀態,否則判斷cmd_record[29:24]數據量是否為0,不為0則進入S3狀態繼續讀取數據,為0檢測指令FIFO是否為空,為空同樣進入S12狀態,否則進入S7狀態。S7,S8完成從指令FIFO中讀取新的指令操作,如果地址連續則不需要結束本次讀操作而直接從S8進入S3狀態繼續進行讀操作,否則進入S9狀態結束本次讀操作并進行新的讀操作。S12中主要完成關閉讀模塊操作,之后進入OVER狀態,OVER狀態將done拉高。寫管理器的狀態機設計與讀管理器類似,不再贅述。

2 ?仿真和分析

2.1 ?前仿真

帶FIFO的多通道存儲控制器在Xilinx ISE 14.7環境下開發。以Micron公司提供的M25P64模型在ModelSim中進行行為級仿真。帶FIFO的多通道存儲控制器將對外部存儲單元的操作轉化成對FIFO的操作,FIFO由Xilinx FIFO生成器IP核構造。為了盡可能消除毛刺,提高系統穩定性,本文設計中所有的多路器都采用時序邏輯觸發的方式[7?9]。

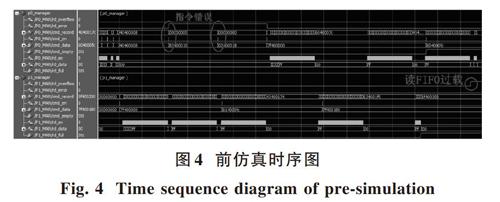

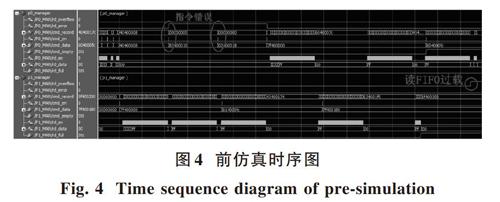

前仿真時序如圖4所示,p0通道和p1通道可以不沖突地輪流讀取數據。在此過程中人為設置了錯誤的指令名和FIFO過載等非正常狀態,而從仿真的時序圖中也不難發現這些非正常狀態均能得到預期的反饋。

2.2 ?后仿真

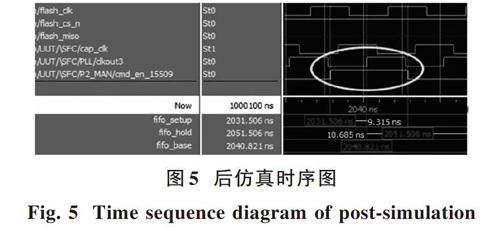

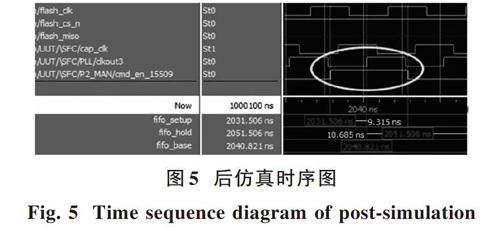

綜合并布局布線后仿真可以全面地包含器件延時、連線延時以及時鐘毛刺等信息,不但可以全面地驗證所設計的模塊功能是否滿足設計要求,還能保證穩定性要求。本文設計中后仿真要解決的核心問題是窗口問題,即將時鐘信號的采樣邊沿調整到有效窗口的中心位置。

圖5是fifo_clk后仿真時序圖,系統時鐘設置為50 MHz。如圖5中橢圓標示處,fifo_clk上升沿處于有效窗口中心位置,此時,能保證最優的建立時間和保持時間。flash_clk,cap_clk時鐘調節過程同fifo_clk。

經過后仿真時鐘相位調節,Micron公司提供的M25P64仿真模型和Xilinx庫均無報錯,因而滿足時序要求。

3 ?下板驗證及測試

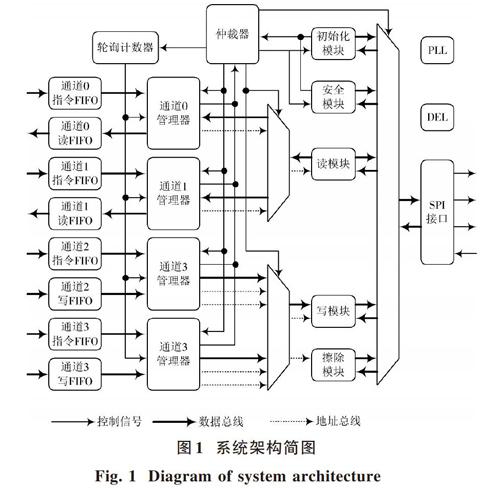

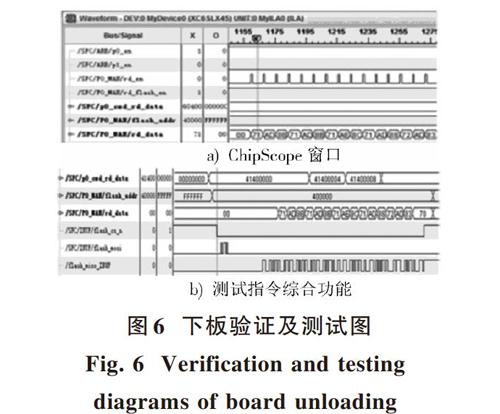

ChipScope是ISE開發環境中的一個工具,集成了關鍵邏輯分析器和其他測試和測量組件,用于測試Xilinx FPGA芯片內部的目標設計[10?11]。本文設計的帶FIFO的多通道存儲控制器在Xilinx公司的FPGA芯片XC6SLX45中進行驗證和測試。該設計主要資源使用情況如下:使用邏輯片資源657,占9%;使用1個PLL資源,占25%;使用6 KB嵌入式RAM資源,占2%。

圖6a)為ChipScope窗口。從ChipScope中觀察到本文設計的存儲控制器能從外部存儲單元中讀取數據。圖6b)為測試指令綜合功能。寫入3條地址連續的讀/寫指令,如圖6b)中p0_cmd_rd_data所示,3條指令被綜合成一條讀指令,如圖6b)中flash_addr所示。綜上所述,本文設計與實現的帶FIFO的多通道存儲控制器達到了預期功能,具有較強的實用性。

4 ?結 ?語

本文以實際應用為出發點,實現帶FIFO的多通道存儲控制器,使得多個外部模塊能夠高效而又無沖突訪問同一外部存取單元。本文設計不局限于SPI接口NORFLASH,其他類型存儲單元只要改變對應接口模塊和讀/寫模塊即可,因而具有良好的可移植性和通用性。本文設計具備高度的可配置性,用戶可以根據具體應用自由定義通道數量、各通道功能、各通道輪詢時間、FIFO深度等,以達到最高資源利用效率。

參考文獻

[1] LIU B L, LIU B Q, PAN L, et al. Research and design of video acquisition system based on FPGA [J]. Applied mechanics and materials, 2014, 644: 3472?3475.

[2] 李明明,王全忠,郭偉,等.一種NOR FLASH控制器驗證平臺的研究[J].現代電子技術,2015,38(10):162?165.

LI Mingming, WANG Quanzhong, GUO Wei, et al. Research on a verification platform for NOR FLASH controller [J]. Modern electronics technique, 2015, 38(10): 162?165.

[3] 呂波,張涌,黃侃,等.基于FPGA的四口RAM設計與實現[J].儀表技術與傳感器,2017(1):34?37.

L? Bo, ZHANG Yong, HUANG Kan, et al. Design and implementation of quad?port RAM based on FPGA [J]. Instrument technique and sensor, 2017(1): 34?37.

[4] 吳長瑞,徐建清,蔣景紅.基于Kintex?7 FPGA的DDR3 SDRAM接口應用研究[J].現代電子技術,2017,40(24):21?24.

WU Changrui, XU Jianqing, JIANG Jinghong. Application of DDR3 SDRAM interface based on Kintex?7 FPGA [J]. Modern electronics technique, 2017, 40(24): 21?24.

[5] MAHMOODI M R, SAYEDI S M. A low cost high speed FPGA?based image processing framework [J]. International journal of modern education and computer science, 2016, 8(3): 11?21.

[6] GONG Z P, CHEN T F, ZOU F, et al. Implementation of multi?channel FIFO in one blockRAM with parallel access to one port [J]. Journal of computers, 2014, 9(5): 1193?1200.

[7] 張松,李筠.FPGA的模塊化設計方法[J].電子測量與儀器學報,2014,28(5):560?565.

ZHANG Song, LI Jun. Modular design of FPGA design methodology [J]. Journal of electronic measurement and instrumentation, 2014, 28(5): 560?565.

(上接第4頁)

[8] 關珊珊,周潔敏.基于Xilinx FPGA的SPI FLASH控制器設計與驗證[J].電子器件,2012,35(2):216?220.

GUAN Shanshan, ZHOU Jiemin. Design and verification of SPI FLASH controller based on Xilinx FPGA [J]. Chinese journal of electron devices,2012,35(2):216?220.

[9] 黃宏智,周欽強,黃飛龍.新型自動氣象站NAND FLASH存儲系統的設計與實現[J].電子測量技術,2016,39(12):132?135.

HUANG Hongzhi, ZHOU Qinqiang, HUANG Feilong. Design and realization of the storage system for new automatic weather station based on NAND FLASH [J]. Electronic measurement technology, 2016, 39(12): 132?135.

[10] Xilinx. Product guide: LogiCORE IP FIFO generator v9.3 [EB/OL]. (2012?12?18) [2017?10?25]. https://www.xilinx.com/support/documentation/ip_documentation/fifo_generator/v9_3/pg057?fifo?generator.pdf.

[11] Xilinx. User guide: ChipScope pro software and cores [EB/OL]. (2012?10?16)[2017?10?26]. https://www.xilinx.com/support/documentation/sw_manuals/xilinx14_7/chipscope_pro_sw_cores_ug029.pdf.