基于FPGA+A/D相控陣天氣雷達脈沖壓縮技術實現

摘要:在相控陣天氣雷達中運用脈沖壓縮技術既能提高距離分辨力,又能獲得最大作用距離的優勢。設計了基于FPGA+AD的脈沖壓縮處理系統方案,通過使用寬窄脈沖不同載頻的模式同時完成近距離和遠距離的探測,降低了雷達探測盲區,并在數據處理中使用高速時鐘進行匹配濾波運算,分時復用硬件資源,提高了FPGA硬件資源的使用率,達到了設計目的。

關鍵詞:脈沖壓縮;FPGA

引言

在普通脈沖雷達中,雷達信號的時寬帶寬積是常數,在大氣探測中存在不能同時提高作用距離和距離分辨力的矛盾。解決這一矛盾的辦法可以在發射時采用寬脈沖增加平均功率,保證最大作用距離,在接收時采用窄脈沖獲得較好的距離分辨力,由于采用脈沖壓縮技術的天氣雷達可實現對氣象目標的三維快速掃描,捕捉氣象目標的時間變化過程,近年來脈沖壓縮技術在天氣雷達中得到了廣泛應用。基于FPGA+A/D的脈沖壓縮處理技術,FFT處理為核心部分,速度大多受限于運算中間結果的讀寫操作和旋轉因子的讀取,如何在硬件資源有限的情況下,有效利用FFT運算結構是提高運算速度的關鍵。

1脈壓系統方案設計

1.1脈沖壓縮系統總體設計

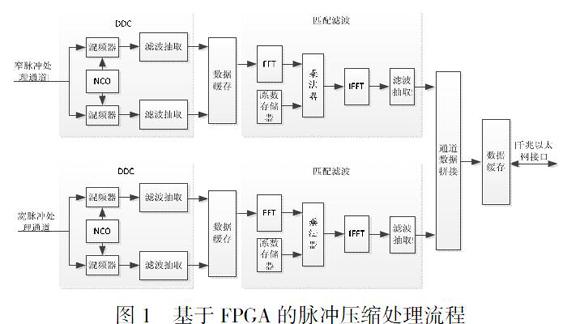

相控陣天氣雷達脈沖壓縮處理系統包含1路時鐘管理、4片高速雙通道16位ADC、1路高性能DDS、1片xc7k325tffg900、1路SFP千兆網光纖傳輸通道、2片DC-DC器件組成6路電源轉換模塊以及其他外圍接口電路組成。系統工作時,FPGA中數字下變頻分8路獨立通道,下變頻處理后數據率降低,此時可采用分時復用的方式,在FPGA內部設計一個匹配濾波處理通道,然后多通道分時復用,降低硬件資源消耗。

1.2系統實現

眾所周知,在大時寬帶寬積的脈沖壓縮系統中,發射時寬與探測盲區存在矛盾的問題。而實際系統中,往往要求探測威力與探測盲區同時最優,此時,通過雙脈沖的工作模式,可達到探測威力與探測盲區之間的最佳平衡。

采用不同發射載頻的雙脈沖工作模式可消除兩組脈沖之間的相互干擾,接收處理時,寬窄脈沖僅接收對應發射頻率的回波信號,兩組脈沖間完全不會引入虛警信息。

本系統中采用100和20雙脈沖的工作模式,其中100脈寬對應中頻頻率為65MHz,20脈寬對應中頻頻率為55MHz,探測盲區為3km。AD采樣率為80MSPS,DDC處理后數據率為4MSPS,匹配濾波后數據率為2MSPS,基于FPGA的脈沖壓縮處理實現流程如圖1所示。

本系統采用Xilinx公司的Vivado開發工具進行FPGA設計,上述處理流程中的NCO、混頻器、濾波器、數據緩存、FFT、乘法器、IFFT均使用開發工具提供的IP核。通過對IP核的準確配置,實現算法需要的功能。

2算法設計

2.1 基于FPGA的數字下變頻處理

DDC(Digital Down Converter)即數字下變頻,是通過NCO(數控振蕩器)產生與射頻或中頻信號載波相同頻率的正弦或余弦信號,與采樣后的中頻信號相乘,最后通過濾波、抽取得到基帶信號的過程。本系統中,為盡可能降低不同載頻的兩種發射脈沖的相互干擾,在DDC處理前加入了帶通濾波器。

DDC處理過程中的NCO、混頻器以及低通濾波器均使用Vivado開發工具提供的IP核。其中NCO使用開發工具提供的DDS Compiler核完成,通過配置DDS Compiler核中的系統時鐘、動態范圍、頻率精度以及輸出頻率等信息。混頻器使用開發工具提供的Multiplier核完成,配置Multiplier核的數據類型、數據位寬、資源使用選擇等信息。

DDC處理過程中,最核心部分是在于低通濾波器的設計。實際開發時,使用Matlab仿真低通濾波器,并生成低通濾波器系數。在Vivado開發環境中調用FIR Compiler核,配置濾波器系數、數據率以及抽取關系等參數。

2.2基于FPGA的數據緩存處理

本脈沖壓縮處理過程中,為節約處理過程中的時間資源,采用160MHz時鐘進行FFT和IFFT運算,由于DDC輸出數據率與FFT輸入數據率時鐘不匹配,所以在DDC輸出與FFT輸入之間加入緩存處理,每完成一個PRT的I/Q數據緩存后,啟動FFT處理。本系統中寬脈沖最大處理庫數為8192,所以實際設計時,使用深度為16384的雙口RAM進行數據緩存。數據緩沖器使用Vivado開發工具提供的Block Memory Generator核,配置存儲器類型、寫端口的數據寬度和深度、讀端口的數據寬度等信息。

2.3?基于FPGA的頻域匹配濾波處理

匹配濾波器是一種最佳線性濾波器,其作為最優濾波器,依據是白噪聲背景下的信號經處理后輸出信噪比達到最大值。在這一準則下,使得接收信號在判決時刻的輸出信噪比最大,能最佳地判斷信號的出現,系統的檢測性能就可以提高,從而實現對信號的最佳接收。匹配濾波器的傳輸函數與輸入信號有關,信號不同,則匹配濾波器也不同。

基于FPGA的匹配濾波,首先將濾波器系數量化后存至ROM,調用FFT IP核完成回波的FFT處理,接著將回波FFT結果與濾波器系數進行點乘,最后再次利用FFT IP核完成點乘結果的IFFT運算(配置成逆FFT方式)。本系統中,為滿足高實時性的要求,使用流水線結構模式,該模式允許連續的數據處理,系統中寬脈沖的最大處理庫數為8192,所以FFT點數設置為8192,工作時鐘頻率為160MHz。

3性能分析

在硬件設計時,硬件資源和處理時間的均衡是設計難點,本系統中,合理計算各模塊的處理時間,并根據處理時間將硬件處理通道分時復用,達到資源利用最大化。重復周期等于1024us時,每個重復周期DDC輸出數據庫數為4096。所以當重復周期大于1024us時,FFT的運算點數8192,小于等于1024us時,FFT運算點數為4096。

本系統中,為節約硬件資源,要求FPGA務必在一個重復周期內盡可能完成更多通道的脈沖壓縮處理。所以,在分時控制時,必須精準控制每個完成一個通道的脈沖壓縮處理時間。

實際設計時,為盡可能節約時間資源和硬件資源,務必清晰FFT核工作時,注入數據時間、計算時間以及輸出數據時間等信息,本設計中,采用160MHz時鐘進行匹配濾波運算,一個FFT核和一個IFFT核完成匹配濾波算法

8192點處理耗時關系為:t=154.762*N+103.562(N為處理通道數)

4096點處理耗時關系為:t=77.969*N+52.369(N為處理通道數)

當PRT(脈沖重復周期)大于1024時,FFT點數為8192,單個硬件處理通道最多可復用5次,即一個重復周期內單處理通道最多可完成5個通道脈沖壓縮處理。當PRT為500時,FFT點數為4096,單個硬件處理通道最多可復用5次,即一個重復周期內單處理通道最多可完成5個通道脈沖壓縮處理。對于本設計中,每個FPGA完成8個通道的處理,通過以上處理時間的分析可知,在FPGA內部搭建兩個處理通道即可分時完成8個通道的處理。

4小結

本文主要闡述了基于FPGA+AD的脈沖壓縮處理系統方案,給出了脈壓系統方案設計和算法設計,并對性能進行了分析,分析表明該方案達到了設計目的。

參考文獻

[1]S.Mudukutore,V.Chandrasekar.R.Jeffrey Keeler,Pulse Compression for weather radars,IEEE Trans.Geosciense and Remote Sensing,VOL 36,N0.1,January 1998

[2]魏靈,楊日杰,崔旭濤.基于分布式算法的數字濾波器設計[J].儀器儀表學報,2008(10):2100-2104.

作者簡介:張濤(1986-)男,漢族,新疆伊寧人,本科學歷,工程師,從事氣象業務培訓工作。

(作者單位:1.中國氣象局氣象干部培訓學院新疆分院;2.新疆信息工程學校)