Gardner同步算法在高速GMSK信號傳輸中的應用

顧圣明,陳麗婷,陳建斌

(上海航天電子技術研究所,上海 201109)

0 引言

高斯最小頻移鍵控(GMSK)調制屬于連續相位調制[1-2],具有很好的頻譜性能和恒包絡特性。這2種特性使得GMSK調制在遙控遙測領域的應用也日益廣泛。目前,中國大多數的脈沖編碼調制-調頻(PCM-FM)體制遙測系統的碼率都不超過2 Mbps[3],少數靶場開始配備10 Mbps碼率的GMSK體制遙測系統。但面對越來越高的遙測傳輸需求,提高GMSK體制遙測系統的傳輸速率迫在眉睫。通常,限制遙測系統碼速率的有硬件平臺性能以及位同步所需的過采樣率,文獻[4]針對GMSK系統提出了一種簡單的位同步開環算法,結構簡單,但其需要16倍乃至更高的過采樣率,且同步性能一般。文獻[5]中提出了一種快速捕獲的位同步器,主要通過超前滯后信息來完成時鐘的“添扣”,達到同步目的,但其精度取決于環路分頻即過采樣率,同樣限制了傳輸速率。文獻[6]提出了一種針對脈沖成型波形的位同步方法,在接收端進行匹配濾波來提取位同步時鐘,復雜度低,但只適用于高倍采樣系統中。可以看出,目前大多數遙測系統仍通過資源換性能的方法,以高倍采樣率來完成高精度的位同步。本文利用Gardner算法,以低倍采樣率來完成位同步,在保證相同誤碼率的條件下提升GMSK信號傳輸的速率。Gardner算法是利用內插法來實現位同步的方法,通過定時環路調整內插濾波器的位置參數來找到最佳的內插位置,從而恢復位同步信號,主要優點在于不需要調整本地時鐘,直接數字處理便可獲得同步時鐘以及最佳采樣點判決信息。本文將Gardner算法應用于GMSK體制中,給出其改進結構和程序設計,并進行仿真和實際測試,最終給出其在GMSK體制中20 Mbps碼率下的測試結果。

1 Gardner算法的原理與改進

1.1 Gardner算法的基本原理

如文獻[7-9]中所述,Gardner算法的實現流程如圖1所示,主要由4部分組成:內插濾波器、環路濾波器、控制器和定時誤差檢測器,在不改變本地時鐘的同時能夠實現位同步。同步過程如下:接收端以本地時鐘Ts對接收信號重新采樣,送入內插濾波器進行內插值的計算,計算出的結果送入定時誤差檢測器進行誤差檢測,并送入環路濾波器濾除帶外噪聲,環路濾波器的輸出送入NCO控制器計算內插基點和分數間隔,進行下次內插位置的調整,如此循環往復,從而在最佳采樣時刻內插出準確的判決值,即滿足位同步條件時的采樣值。

圖1 Gardner算法的實現流程

1.2 Gardner算法的改進與設計

1.2.1 內插濾波器設計

內插濾波器[10]是Gardner算法的核心。內插濾波器的作用可以理解為重構后重采樣,也就是從離散信號理想地重構出連續信號y(t),再用另一個不同速率或不同初始時刻重新采樣。

從采樣x(mTs)恢復原連續信號

(1)

再對其進行重采樣,可以得到

(2)

(3)

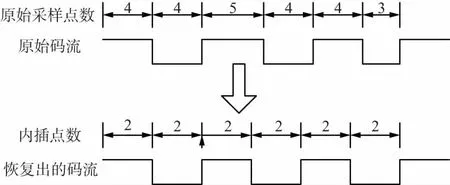

(4)

式中,μk為計算出的分數間隔,決定內插濾波器的系數大小;mk為插值位置的基點,決定由哪幾個位置的采樣點計算出內插值;kTi和μk的信息由內部控制器給出。輸入與輸出的采樣時刻關系如圖2所示。

圖2 輸入與輸出的采樣時刻關系

從式(4)可以看出,插值輸出就是采樣點的線性加權和。而且實際上不需要對連續信號完全重構,可以直接從非同步采樣到同步采樣值。式(4)是無窮項的加權求和,實際上做不到沒有誤差的理想插值,只能用有限階的濾波器來實現,即

(5)

式中,μk可以取到0-1之間的所有值,對不同的μk實時計算sinc函數在硬件上難以實現,因此用多項式對理想加權系數進行逼近,即

(6)

顯然,階數取得越大,逼近效果越好。考慮到資源和平衡,本設計采用分段拋物線式濾波器[11],根據文獻[12],α=0.5時濾波器具有較好的性能,即

(7)

式中,

(8)

1.2.2 定時誤差檢測器設計

定時誤差檢測算法對位同步整體性能起決定性作用。本設計采用GA-TED[13]算法,該算法獨立于信號速率,提取出的定時誤差可以表示為:

(9)

式中,相鄰碼元差值表示誤差正負即方向,碼元中間采樣時刻的值代表誤差大小。本設計中,用y(n)和y(n-1)的符號代替實際值,來表示誤差的方向,即

(10)

采用式(10)可以消除大部分噪聲的影響,并且可以避免乘法運算,有利于數字系統的實現。

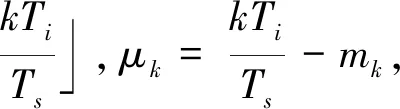

1.2.3 環路濾波器設計

本文對Gardner算法中的環路濾波器進行了修改,采用二階環路濾波器[14],具有比較好的跟蹤性能。濾波器采用文獻[15]中所述的結構,如圖3所示。

圖3 環路濾波器結構

其在Z域上的傳遞函數為:

(11)

式中,k1=2ξωn/(K*Rs);k2=(ωn)2/(K*R2s);一般來說,阻尼系數ξ取0.707;ωn為環路的自然角頻率;ωn=4ξBL/(4ξ2+1);BL為環路帶寬,對環路同步速度和精度都有影響。環路增益K=KdKo;Kd為鑒相器增益;Ko為NCO的增益。對上式進行反變換,就可以得到環路濾波器的時域方程:

y(n)=y(n-1)+k1[x(n)-x(n-1)]+k2x(n) 。

(12)

另外,本設計中開放濾波器參數k1,k2接口,如果碼元速率變化,NCO參數可以隨之變化,實現跟蹤。

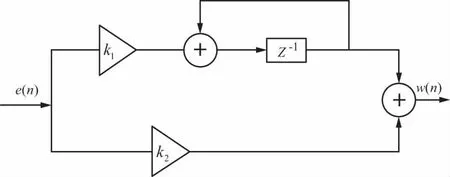

1.2.4 NCO控制器

Gardner環的控制器主要由NCO以及分數間隔計數器組成。NCO起到一個累減器的功能,0~1累減并給出溢出信號,即確定內插基點位置mk。分數間隔計數器計算出分數間隔μk,作為內插基點后所需要的更精確的位置信息,從而找到最佳采樣值。下面給出累減器的差分公式:

ηmk=[ηmk-1-w(mk-1)]mod(1) ,

(13)

式中,ηmk為第mk個時鐘時寄存器的值;w(mk)為第mk個時鐘時的控制字(環路濾波器輸出;,mk為內插基點;k為內插點的序號;NCO的初值設為1。隨著采樣時鐘進行遞減,到零時得到內插時鐘,確定內插基點,然后開始計算它的分數間隔μk。當環路穩定時,w(mk)就是一個固定值,每隔1/w(mk)個周期就會產生一次溢出,而控制器的工作頻率為1/Ts,內插的工作頻率為1/Ti,則穩定后w(mk)=Ts/Ti。w(mk)與環路濾波器的具體關系為

w(mk+1)=w(mk)+e(mk) ,

(14)

式中,e(mk)即為環路濾波器的輸出。求得w(mk)就可以求得η(mk+1),如果η(mk+1)得負值,則說明NCO寄存器溢出,此時的mk即為內插基點,此時計算出相應的分數間隔μk,并讓插值濾波器進行一次內插操作。μk的計算關系如圖4所示。

圖4 內插間隔的計算示意圖

根據圖4三角形的相似關系可得:

(15)

(16)

以上就得到了信號的內插基點和分數間隔。

2 程序設計與仿真

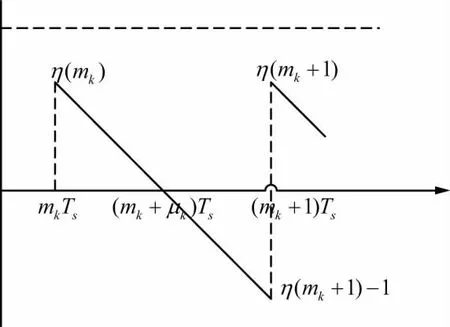

本設計是將Gardner算法應用于GMSK體制信號傳輸中,即對GMSK解調后的基帶碼元做位同步設計。GMSK體制的解調模塊采用文獻[16]的設計,即GMSK調制信號經過維特比解調后輸出基帶碼元。經調查,文獻[16]采用的是利用超前滯后信息來添扣時鐘的位同步方法,需要16倍的過采樣率來保證提取精度,如果要實現20 Mbps碼速率的傳輸,其硬件平臺需提供320 MHz的采樣時鐘,對硬件性能要求比較高,因此限制了其碼元速率為10 Mbps。

本設計旨在利用Gardner同步算法降低過采樣率需求,從而提升傳輸碼速率。在文獻[16]中,GMSK解調后的輸出碼元為不均勻采樣的01碼元,以4倍采樣率為例,輸出的碼元大部分為4個采樣點的碼元,少部分為3個或5個采樣點的碼元,即存在采樣偏移,而Gardner算法則是要從這樣的碼元中找到最佳采樣時刻的判決信息。Gardner算法作用示意圖如圖5所示。

圖5 Gardner算法作用示意圖

2.1 Matlab仿真

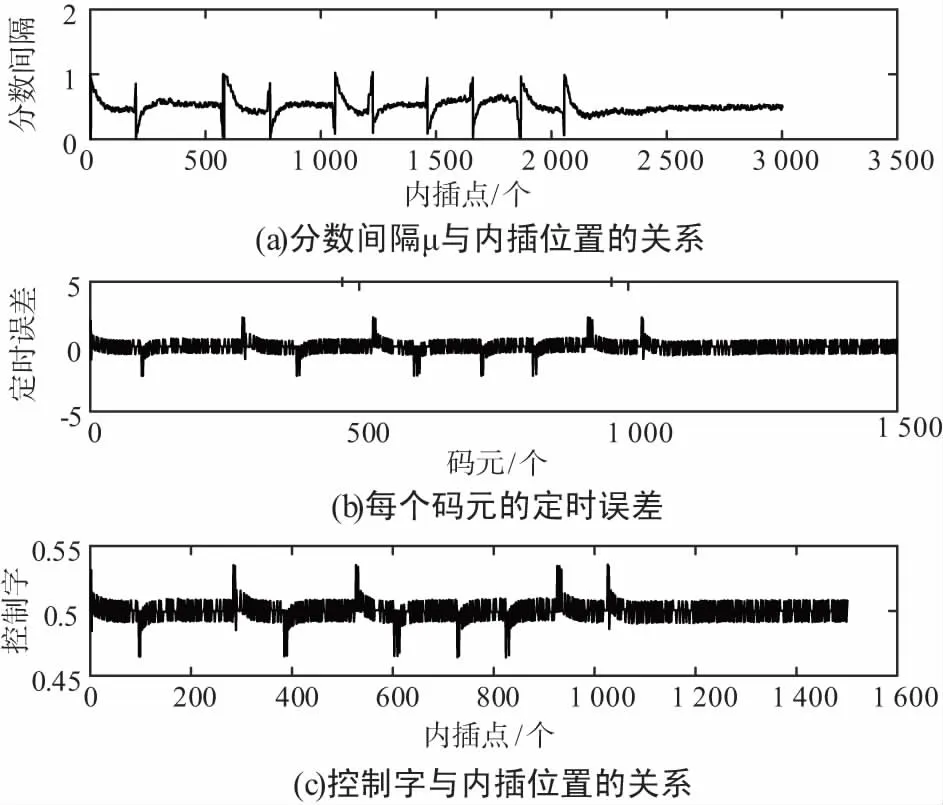

在Matlab中模擬出GMSK解調模塊輸出的碼元并用Gardner算法對其進行位同步,仿真結果如圖6所示。可以看出,當存在3個或5個采樣點的時候,分數間隔會進行對應調整,偏移內插基點,最終找到最佳采樣時刻的判決信息。圖中仿真了1 500個碼元,分數間隔輸出為3 000個點,定時誤差和環路濾波輸出為1 500個點,正對應于每個碼元內插出2個采樣點,并輸出一個定時誤差間隔。經過長時間測試,Gardner位同步模塊的誤碼率為0,性能可靠。

圖6 Gardner算法的Matlab仿真圖

2.2 FPGA設計

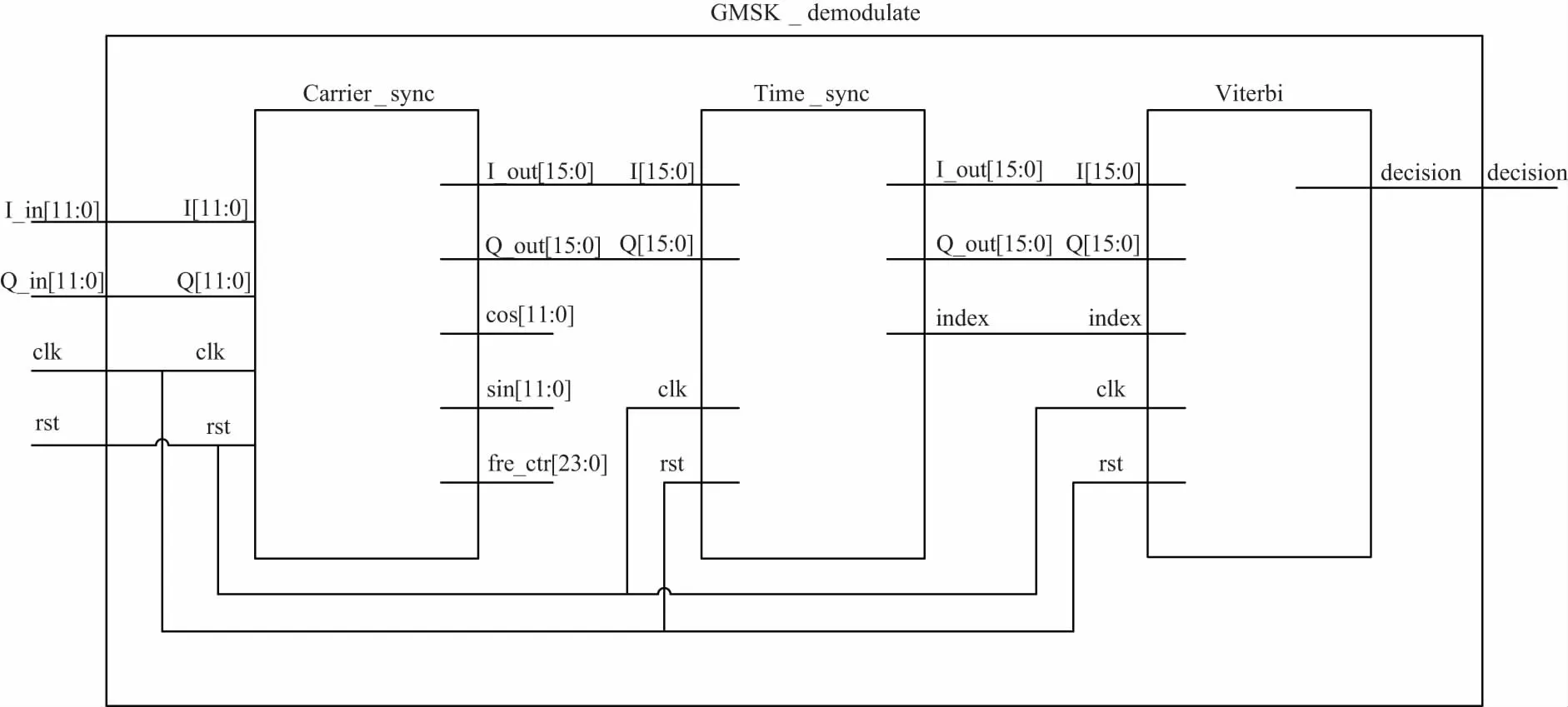

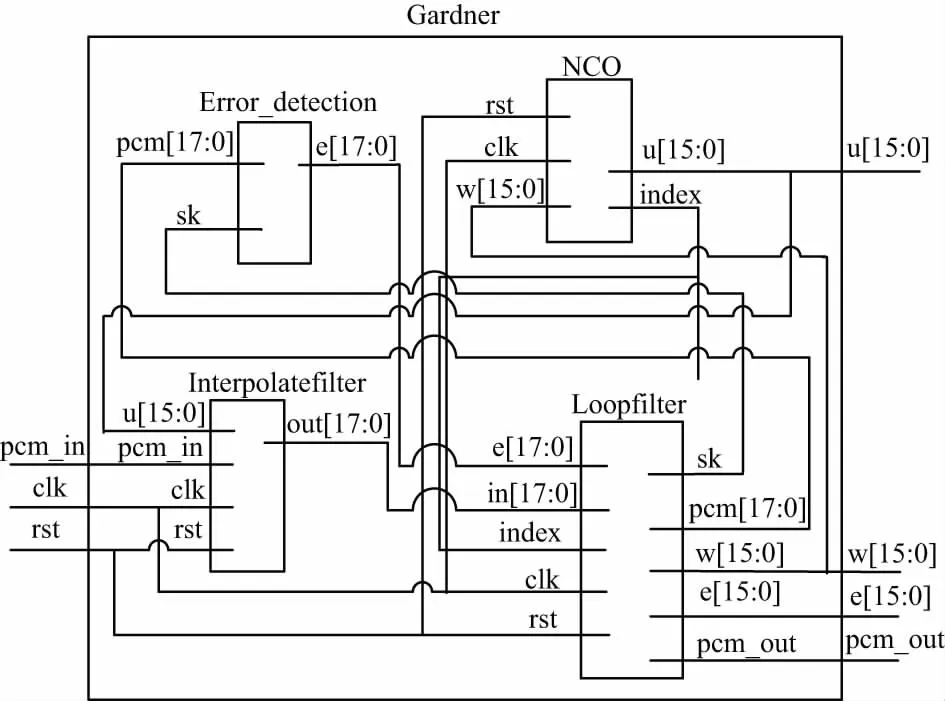

根據1.2節的設計原理,對Gardner算法進行Verilog設計,FPGA采用Xilinx公司K7系列的XC7K160T芯片。GMSK解調模塊和Gardner位同步器FPGA設計的頂層圖如圖7和圖8所示,GMSK解調出的基帶碼元信號送到Gardner位同步模塊進行同步。

圖7 GMSK解調模塊頂層設計

圖8 Gardner位同步模塊頂層設計

可以看到,Gardner模塊分為內插濾波器、控制器、定時誤差檢測器以及環路濾波器4個模塊,最終輸出判決碼元信息,其中,內插濾波器使用分段拋物線式濾波器,占用了9個加法器和3個乘法器,占用資源很少。另外,程序中除以2的運算都采用移位實現,避免使用除法器,所有變量的寄存器經過計算后均采用最小位數,有效減少了Logic Elements資源的占用。

2.3 FPGA仿真

仿真在Xilinx ISE環境下進行,基帶信號由Matlab的Binary generator產生,將碼速率設置為10~20 Mbps,NCO及環路濾波器做相應設置,不同碼速率仿真出的波形基本相同,僅存在采樣速率上的差別,恰巧說明了Gardner算法對不同速率的基帶信號均能很好地提取位同步信號。仿真結果如圖9所示。可以看到,與第3章中Matlab仿真結果一致,Gardner算法在存在采樣偏移的碼元處進行內插位置的調整,從而找到最佳采樣時刻。

圖9 Gardner算法Modelsim仿真結果

根據設計要求,同時對Gardner算法的同步范圍進行了測試,同步范圍測試即對存在采樣率偏移的基帶信號,用相同的時鐘,濾波器參數等對其進行同步,測試其采樣偏移的允許范圍。

當10 Mbps碼速率40 MHz時鐘均勻采樣的基帶信號由39.8 MHz時鐘重新采樣后,Gardner算法對其位同步所得到的仿真圖如圖10所示。可以發現,誤差間隔μ按一定周期規律進行調整,原因則在于此時的基帶碼元存在周期性的采樣偏移,由此可知,Gardner算法仍然能有效工作。經測試,Gardner算法能夠允許的采樣偏移為±1.5%(以此40 MHz數據為例,同步范圍為39.4~40.6 MHz),在此范圍內,Gardner算法均能準確無誤碼地提取位同步信號。

圖10 存在采樣偏移時Gardner算法的Modelsim仿真結果

3 硬件平臺實際測試與分析

本設計中用于實際測試的遙測系統為以AD9361+FPGA為基礎構成的軟件無線電平臺[17-18],如圖11所示。GMSK調制信號由RS公司的SMW200A射頻信號源給出,AD9361將射頻信號搬移到零頻送給FPGA進行GMSK解調以及本設計中的Gardner位同步,同步后的碼元送入實時軟件進行碼元對比,測試誤碼率。

圖11 AD9361+FPGA的軟件無線電平臺

信號源輸出的信號為20 Mbps 碼速率100 MHz采樣率的 GMSK 信號,其中頻載波為390 MHz,碼元序列采用的是 EB90測試序列。Gardner 碼同步器的環路濾波器的參數分別為1.3×10-3和8.9×10-7。

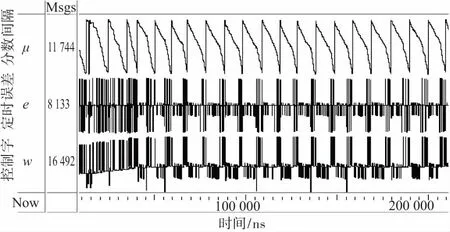

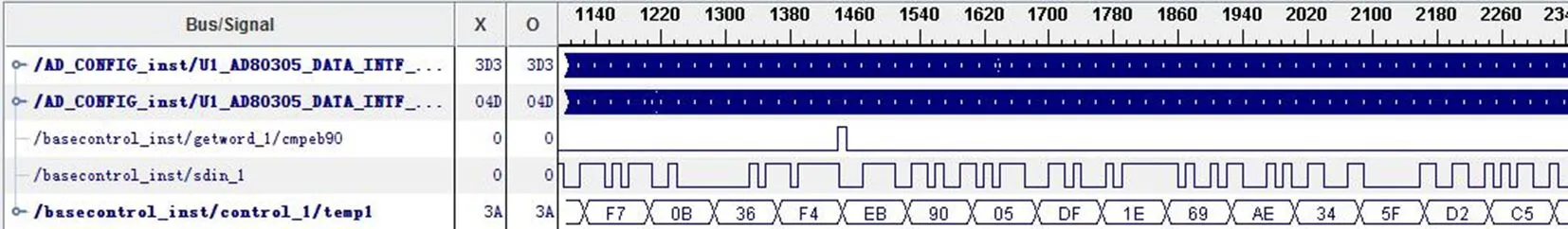

測試過程中,用Chipscope在線邏輯分析儀對Gardner模塊中的信號進行抓取,驗證其是否正常工作。

Chipscope所抓取出的分數誤差間隔μ的工作情況如圖12所示。與之前的仿真結果一致,分數間隔μ在出現采樣偏移的時刻會進行內插位置的調整,以獲得最佳采樣時刻,在沒有采樣偏移的時刻,μ穩定在0.5附近進行均勻內插。

圖12 硬件測試時Gardner算法工作情況

Gardner位同步的輸出如圖13所示。其中,sdin信號即為判決出的碼元序列,temp1為其16進制表示,cmpeb90為檢測到EB90幀頭所輸出的同步信號,經過對比,可以發現其波形與信號源中設置的 EB90的Datasource完全相同,Gardner位同步模塊正確找到了所有碼元的判決信息。

圖13 硬件測試時Gardner同步模塊的輸出

最后,對此GMSK體制信號傳輸系統進行誤碼率測試,在低信噪比環境下驗證其傳輸性能,測試結果如圖14所示。可以發現,與維特比的理論解調值僅有0.5 dB的損失,此結果也與文獻[16]中的誤碼率一致,說明在碼速率提升至20 Mbps的情況下,采用了Gardner位同步算法的GMSK體制在相同誤碼率的情況下沒有造成信噪比的損失,Gardner算法準確找到了所有碼元的判決信息。

圖14 GMSK誤碼率測試曲線

4 結束語

本文主要研究并實現了Gardner同步算法在GMSK體制高速通信處理中的應用。研究和實驗表明,在原有GMSK體制的解調平臺下(通信速率10 Mbps),通過采用Gardner位同步算法,降低了同步采樣率,將系統的通信速率升級到20 Mbps,提升了系統的性能指標,降低了軟件設計的復雜度。另外,Gardner算法所表現出的優異性能并不受調制體制限制,可以將其應用在其他數字解調技術的位同步中,有利于數字接收機的簡化以及傳輸速率的提升。