一種小型化設備方案的設計與實現

王磊

摘 要:為解決現有通信設備體積、功耗大的問題,文中提出一種小型化設備的設計及實現方案。方案主要由數字信號信息處理和收發信道兩部分組成,使用高性能SoC處理器代替現有設備中的DSP及FPGA等處理器,使用基于捷變頻器件AD9164設計的數字跳頻本振源代替模擬跳頻本振源,使用射頻直接發射技術代替模擬上變頻混頻技術,簡化了設備數字電路及模擬電路的設計難度,有效降低了設備的功耗、減輕了設備重量、縮小了設備體積。對方案設計中的系統啟動加載流程及通信能力進行測試驗證,測試結果表明,方案可滿足現有通信設備的需求,對后續設備的小型化、輕量化設計具有指導意義。

關鍵詞:AD9164;小型化;射頻直接發射;SoC處理器;通信;輕量化

中圖分類號:TP39文獻標識碼:A文章編號:2095-1302(2019)07-00-02

0 引 言

現有通信設備由中頻信號處理、數據處理、接收信道、發射信道及射頻前端組成,中頻信號處理及數據處理組合使用多種處理器實現數字信號處理及數據解析等功能,接收信道使用二次混頻電路實現下變頻功能,發射信道使用復雜的模擬電路實現上變頻功能,多種專用處理器及模擬混頻電路的使用使得現有設備的質量、體積、功耗都較大。隨著SoC技術及數字電路技術的高速發展[1],完全可對中頻信號處理、數據處理及收發信道進行數模一體化設計。

本文提出一種小型化設備設計方案,給出了設計框圖及實現方法。該方案采用數模一體化設計思想,使用高性能SoC處理器代替現有設備中的多種專用信號處理器,使用數字本振源代替模擬本振源,使用射頻直接發射技術代替模擬上變頻混頻電路,降低數字電路及模擬電路的設計難度。

1 系統設計方案

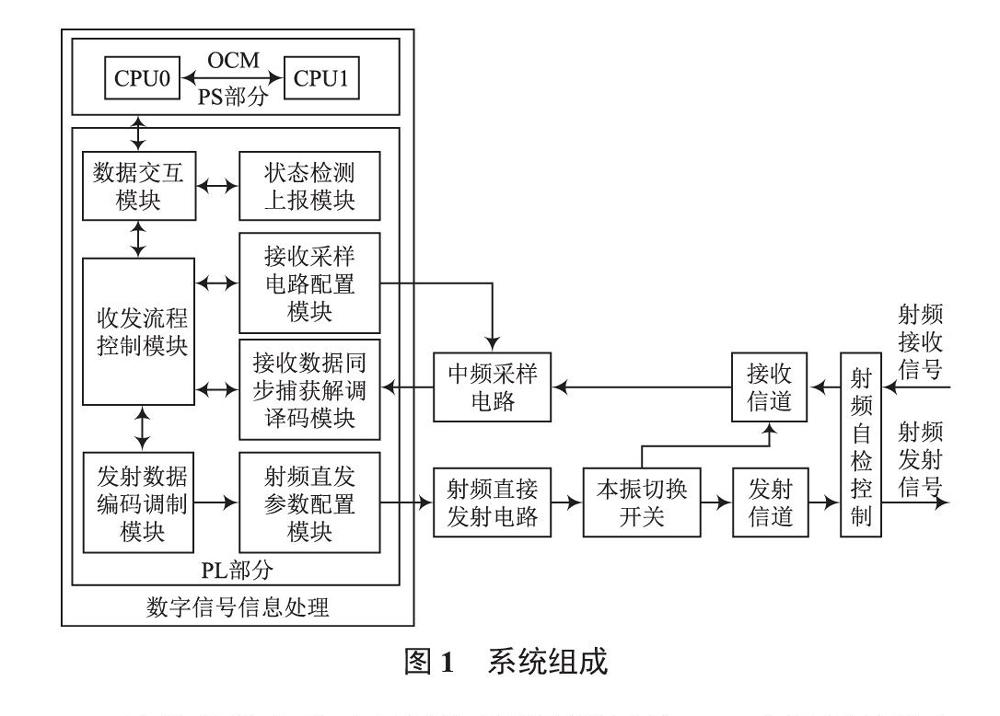

系統由數字信號信息處理、接收信道、發射信道、中頻采樣電路、射頻直接發射電路、本振切換開關及射頻自檢控制組成,結構如圖1所示。

數字信號信息處理分為PL和PS兩部分,具有VxWorks鏡像文件加載、系統收發流程控制、收發電路參數配置、數字信號處理算法及狀態檢測上報等功能。

中頻采樣電路對接收信道輸出的中頻信號進行模數變換后送入數字信號信息處理模塊進行后續處理。

射頻直接發射電路使用高性能AD9164器件和放大濾波電路實現上變頻功能,在系統處于發射模式時將基帶信號上變頻為射頻信號后輸出,在系統處于接收模式時產生所需的快跳本振信號。

接收信道完成對射頻信號的預選濾波、一次混頻及放大處理,發射信道對射頻直接發射電路輸出的射頻信號進行放大濾波后輸出。

本振切換開關在系統處于發射模式時將射頻信號送入發射信道,在系統處于接收模式時將射頻信號送入接收信道的混頻器作為本振源使用。

射頻自檢控制由一組開關組成,系統處于射頻自檢模式時將發射信道產生的信號直接回環到接收信道進行處理,處于正常模式時將射頻接收信號送入接收信道、將發射信道輸出信號送往射頻前端。

2 數字信號信息處理設計

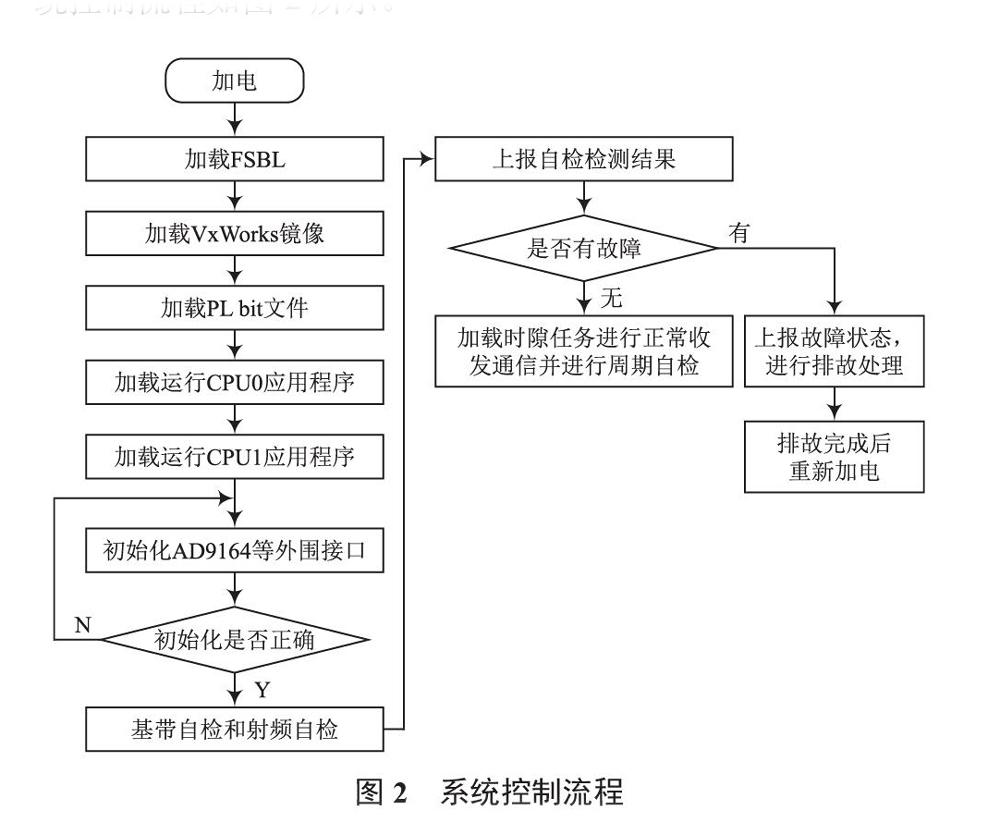

數字信號信息處理部分使用高性能SoC處理器實現現有設備的中頻信號處理及數據處理功能,分為PL和PS兩部分[2],在PL中實現中頻信號處理功能,在PS中實現數據處理功能。PS為兩個主頻為800 MHz的ARM Cortex-A9內核[3],按照功能劃分為CPU0和CPU1,CPU0負責處理器上電初始程序加載、VxWorks系統運行及數據處理軟件運行;CPU1運行信號處理軟件完成收發狀態控制、數據解析等功能。系統控制流程如圖2所示。

設備加電后首先加載FSBL,然后依次加載VxWorks鏡像文件和PL bit文件,最后加載并運行CPU0及CPU1程序。程序運行后首先初始化所有外圍接口,隨后讀取配置狀態,如果配置失敗則重新配置,配置成功后分別進行基帶自檢和射頻自檢,并上報自檢結果,自檢無故障則根據時隙任務進行正常收發通信并進行周期自檢,自檢有故障則根據故障類型進行排故處理,之后重新加電運行。

3 收發信道設計

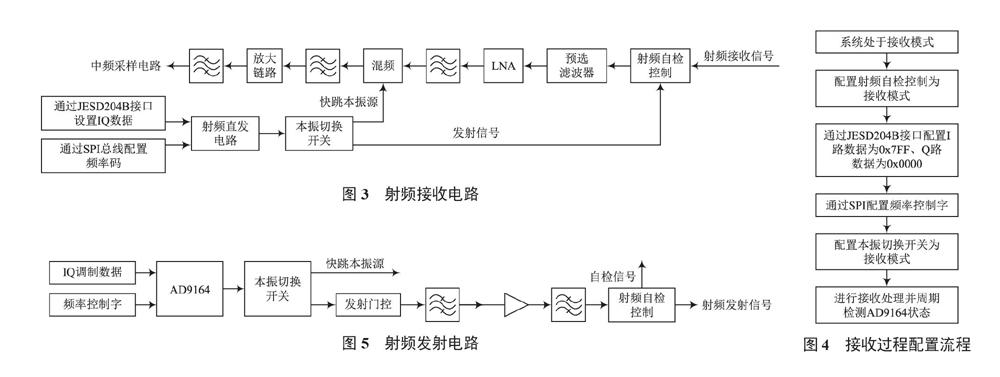

接收信道使用一次混頻電路代替原有的二次混頻電路,使用數字快跳本振源代替模擬快跳本振源,簡化電路結構設計,接收電路框圖如圖3所示。

接收信道首先對射頻接收信號進行預選帶通濾波、LNA放大,然后通過混頻器進行下變頻,最后經中頻濾波后送入中頻采樣電路進行模數變換。通過配置射頻直接發射電路來產生數字快跳本振信號,實現流程如圖4所示。

發射信道采用高性能AD9164和濾波放大電路實現射頻直接發射功能,射頻發射電路設計如圖5所示。

系統處于發射模式時,首先經JESD204B接口設置IQ調制數據[4],然后通過SPI總線配置相應頻率控制字,最后對AD9164上變頻產生的射頻信號進行放大濾波后輸出。本方案中配置AD9164為24倍內插模式,工作模式為NCO基帶直流模式[5],內核采樣速率fDAC為5.76 GHz,頻率控制字為48 bit,計算方式:

4 測試驗證

由系統控制流程可知,設備加電啟動后首先加載FSBL,然后依次加載VxWorks鏡像文件和PL bit文件,最后加載并運行CPU0和CPU1中的應用程序,加電啟動流程如圖6所示。

由圖6可知,系統的加電啟動控制符合設計要求,待所有程序加載運行成功后,使用發送通信測試數據方式進行性能測試,測試結果如圖7所示。

根據測試結果可知,發送端發送5 000組通信測試數據后,在接收端可以完整接收到5 000組通信測試數據,且無丟包和誤碼,滿足通信設計要求。

5 結 語

本文采用數模一體化設計方法,提出一種小型化設備設計方案,給出設計框圖及實現方法,并驗證了方案的可行性。與現有通信設備相比,該方案可以簡化數字電路及模擬電路的設計,有效降低設備功耗、減輕設備重量、縮小設備體積、簡化數據交互控制時序,為后續設備的小型化、輕量化設計提供新的設計思路和參考依據,具有廣闊的應用前景。

參 考 文 獻

[1]陸啟帥,陸彥婷,王地,等.Xilinx Zynq SoC與嵌入式Linux設計實戰指南[M].北京:清華大學出版社,2014.

[2]符曉,張國斌,朱洪順.Xilinx ZYNQ-7000 AP SoC開發實戰指南[M].北京:清華大學出版社,2015.

[3] Xilinx.Zynq-7000 All Programmable SoC Technical Reference Manual[Z].2014.

[4]亞德諾半導體.JESD204串行接口和JEDEC標準數據轉換器[Z].

[5] AD9164:16-Bit,12 GSPS,RF DAC and Direct Digital Synthesizer,Analog Devices[Z].

[6]張清聯.淺談NFC手機非接觸式射頻接口測試方法[J].物聯網技術,2018,8(8):45-47.

[7]金駿,王旭云,孫晨,等.一種小型化高可靠USB測控應答機的設計與實現[J].信息通信,2016(3):70-73.

[8]薛猛,馮占群.一種小型化PLL電路的設計方案[J].產業與科技論壇,2013,12(11):73.

[9]王鈺.基于AD9164的小型化設備研究與實現[J].物聯網技術,2018,8(6):57-59.

[10]吳律.小型收發信機設計與實現[D].西安:西安電子科技大學,2014.