基于TEA1791A 的同步整流電路

朱黎麗,張 彬

(1.重慶工程職業(yè)技術(shù)學(xué)院,重慶 402260;2.重慶航天職業(yè)技術(shù)學(xué)院,重慶 400021)

0 引 言

隨著LED照明技術(shù)的快速發(fā)展,關(guān)于LED驅(qū)動電源的研究越來越多[1-4]。越來越多的使用場合要求電源具備高功率密度和高效率,因此在LED驅(qū)動電源中,LLC諧振變換器和同步整流成為研究的熱點[5-7]。本文以TEA1791A為核心控制芯片,配合帶有中心抽頭的LLC集成變壓器,設(shè)計了一種同步整流電路,給出了實驗結(jié)果。實驗表明,該電路能夠高效工作,提升整機效率。

1 原理分析

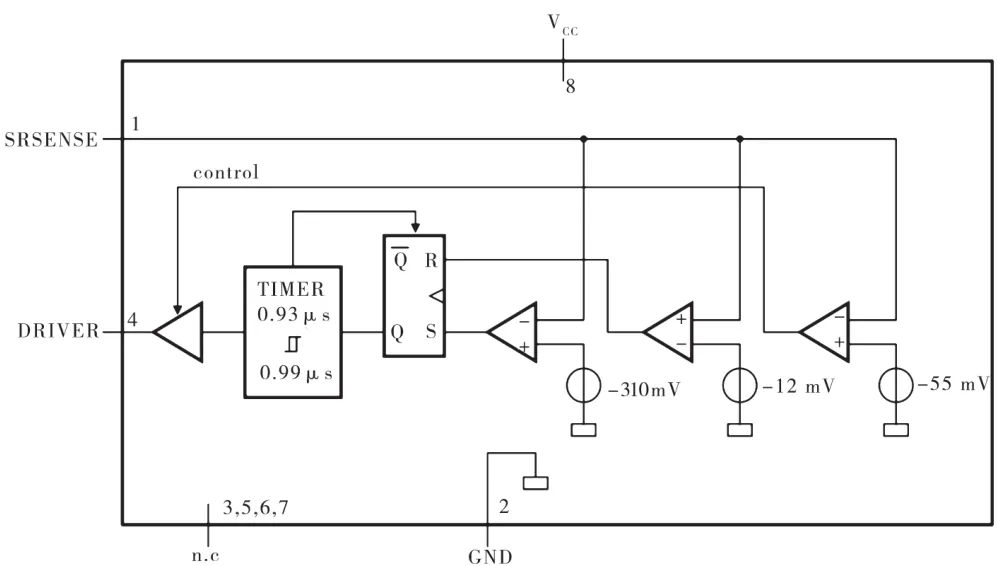

同步整流電路的核心控制芯片為TEA1791A,可用于不連續(xù)模式和準諧振反激變換器,內(nèi)部框圖如圖1所示。當VCC引腳電壓超過8.5 V(典型值)后,芯片會脫離欠壓鎖定狀態(tài)并正常工作。若正常工作中電壓低于8 V(典型值),芯片會重新進入欠壓鎖定狀態(tài),DRIVER引腳保持低電平。當SRSENSE引腳上檢測到負電壓(-310 mV典型值)后,DRIVER引腳會變?yōu)楦唠娖剑獠康腗OSFET會導(dǎo)通。當SRSENSE引腳上的電壓升高到-55 mV時,DRIVER引腳會保持和SRSENSE引腳電壓一致。當SRSENSE引腳上的電壓升高到-12 mV時,DRIVER引腳會被拉到低電平。

當開啟外部的諧振MOSFET時,TEA1791A芯片引腳SRSENSE的內(nèi)部信號會斷開0.93 μs(典型值),以避免由于高頻干擾而導(dǎo)致的誤關(guān)斷。

圖1 內(nèi)部電路框圖

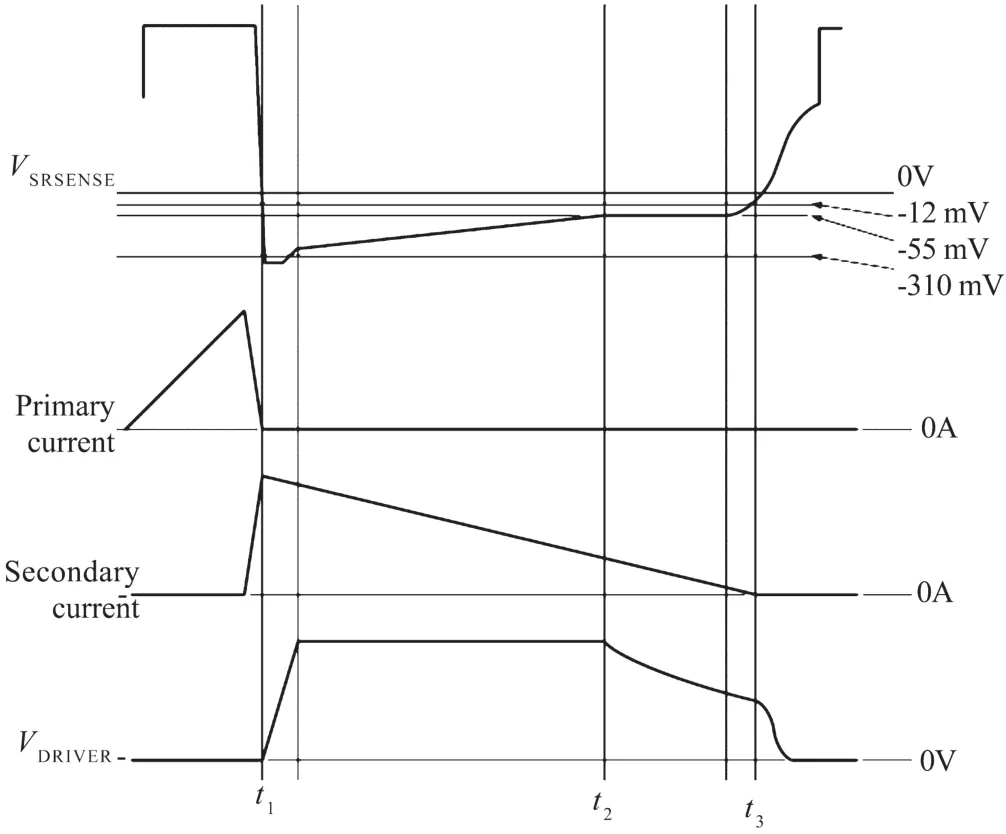

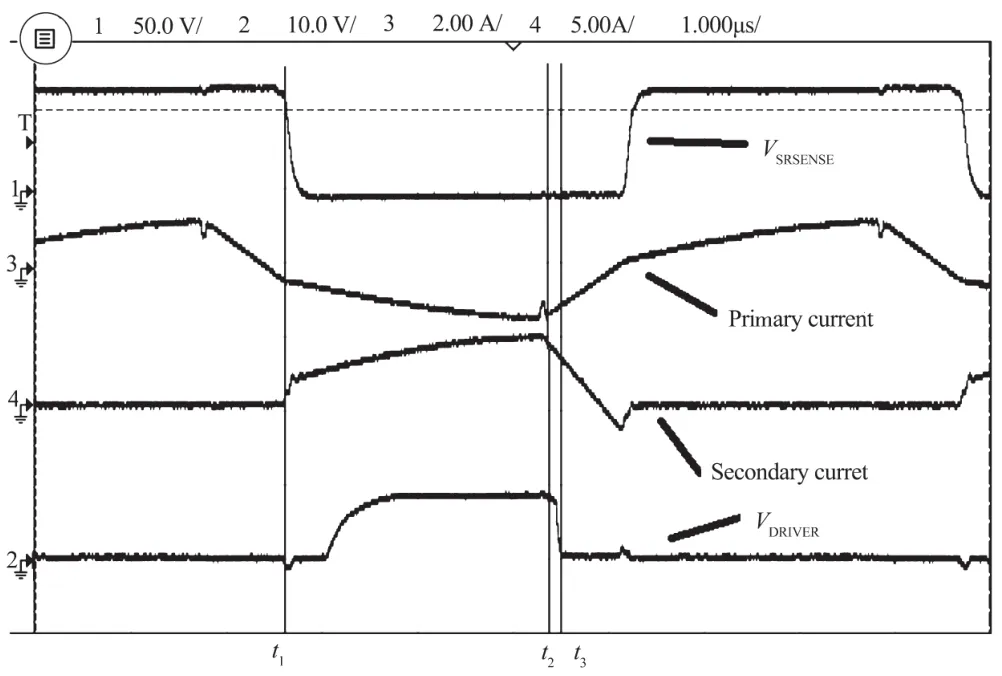

TEA1791A芯片同步整流信號工作原理,如圖2所示,Primary current和Secondary current分別是諧振電路中的一、二次側(cè)電流。受一次側(cè)諧振控制電路控制實現(xiàn)諧振工作,無論電流大小只要符合這種換流趨勢,二次側(cè)都可以用此種芯片進行同步整流。SRSENSE引腳檢測二次側(cè)諧振電流,并把這個電流信號轉(zhuǎn)換為一個電壓信號VSENSE。整個同步整流的工作過程受VSENSE控制。當二次側(cè)諧振電流開始輸出時,檢測到的電壓VSENSE一旦超過-310 mV,DRIVER引腳會開始變?yōu)楦唠娖剑鐃1時刻同步整流工作開始。隨著二次側(cè)輸出電流逐步減小,VSENSE電壓逐步升高,一旦升高到-55 mV,DRIVER引腳的輸出電壓VDRIVER會降低,如t2時刻。當VSENSE持續(xù)升高到超過-12 mV,此時芯片認為流過外部開關(guān)的電流為零,關(guān)閉驅(qū)動,同步整流工作結(jié)束。通過這樣逐步降低驅(qū)動電壓的方式,當通過外部開關(guān)的電流到0時,外部開關(guān)能被迅速關(guān)閉。有了這種零電流關(guān)斷工作模式,不需要為了空載時的高效率而設(shè)計獨立的待機模式。

2 電路設(shè)計及實驗結(jié)果

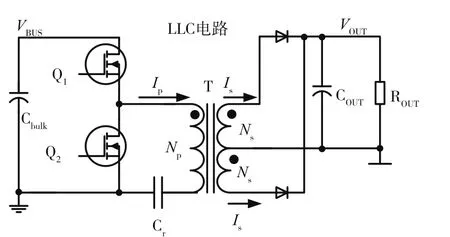

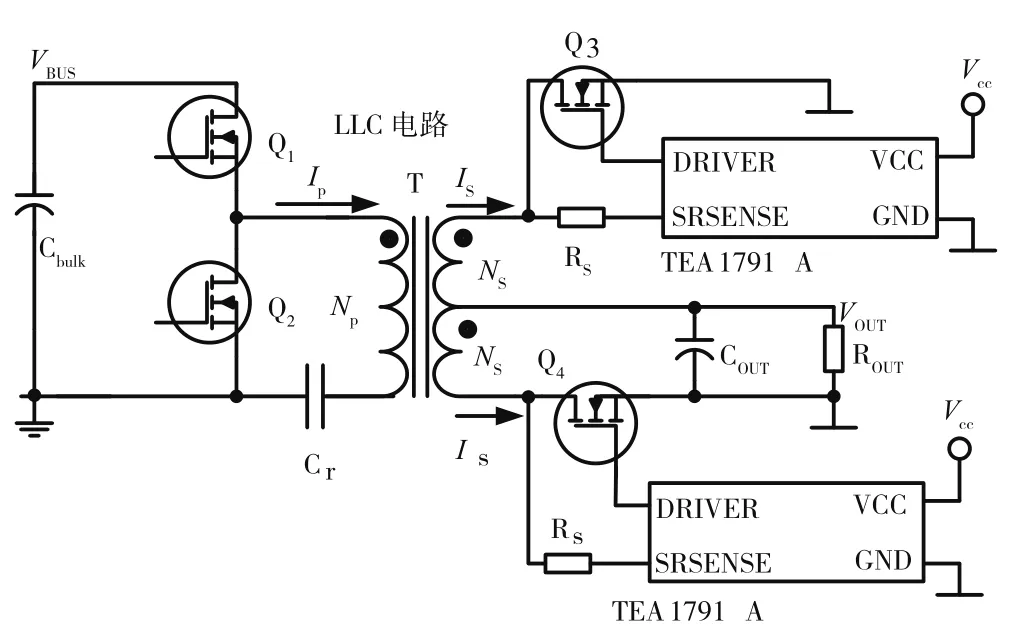

LLC諧振變換器一般電路如圖3所示。

圖3中,T為帶中心抽頭的變壓器,雙路二極管的陰極并聯(lián)接在輸出端。使用同步整流時,不能簡單使用MOSFET替換二極管,應(yīng)考慮MOSFET的內(nèi)部寄生二極管的導(dǎo)通特性。因此,設(shè)計同步整流電路如圖4所示。

圖2 同步整流信號

圖3 LLC諧振變換器

圖4 同步整流電路

圖4 中,Q3、Q4為同步整流用的MOSFET,源極接在輸出的地端,漏極接變壓器,變壓器的中心抽頭為電壓輸出的正極。一次側(cè)電流為Ip,二次側(cè)電流信號Is通過一個電阻RS接在TEA1791A芯片的SRSENSN引腳,變成控制信號VSENSE。本文用1臺輸出功率為120 W、輸出電流3.3 A、輸出電壓為36 V的LLC開關(guān)電源作為實驗平臺,RS電阻阻值設(shè)計為3.6 kΩ,實測同步整流信號如圖5所示,實驗場景如圖6所示。

圖5中,時間為1 μs/格。通道波形1為50 V/格,測試的信號為TEA1791A芯片SRSENSN引腳的電壓值VSRSENSE。通道波形2為10 V/格,測試的信號為TEA1791A芯片DRIVER引腳的值VDRIVER。通道波形3為2 A/格,測試的信號為變壓器一次側(cè)的電流。通道波形4為5 A/格,測試的信號為變壓器二次側(cè)的電流。

圖5 實測同步整流信號

圖6 實驗場景

從圖5看出,在t1時刻,受一次側(cè)控制電路控制,一側(cè)電流結(jié)束,二次側(cè)電流開始輸出,此時VSENSE電壓迅速降低。受示波器顯示精度所限,大約可以讀出此時VSENSE電壓為-3 V,超過-310 mV,VDRIVER開始上升,打開二次側(cè)同步整流開關(guān),進入同步整流工作時間。在t2時刻,受一次側(cè)控制電路控制,二次側(cè)電流輸出結(jié)束,VSRSENSE電壓開始升高,VDRIVER電壓開始降低,至t3時刻完全關(guān)閉。實測波形和圖2中的理論波形較為吻合,主要同步整流工作時間集中在t1~t2時間段和t2~t3時間段,驅(qū)動電壓關(guān)閉過程較為迅速。相比使用二極管整流電路,使用該同步整流電路能夠降低整流的電能損耗,提升整機效率。

3 結(jié) 論

本文設(shè)計了一種基于TEA1791A的同步整流電路,應(yīng)用場合為帶中心抽頭出線方式的LLC諧振變換器。經(jīng)過實驗驗證,設(shè)計實現(xiàn)了同步整流功能。實際電路中應(yīng)盡可能減少主電流導(dǎo)線的長度,增加主電流導(dǎo)線的寬度,降低高頻帶來的干擾。MOSFET的驅(qū)動電路還可以設(shè)計得更為合理和高效。