3bit-ADC底極板與頂極板采樣分析

蘇慶

摘 要:經典ADC/DAC中,為消除頂極板采樣保持電路中存在的電荷注入與時鐘饋通影響,常常采用底極板采樣電路。基于此,本文利用Cadence Spectre工具,對ADC中頂極板采樣和底極板采樣的波形及SNDR等參數進行分析,發現底極板采樣穩定性較好,但能耗相對于頂極板采樣更大。頂極板采樣由于功耗小、失真小、SNDR較大,一般適用于低位ADC中。

關鍵詞:ADC;底極板采樣;頂極板采樣;SNDR

中圖分類號:TP391.41;P631.83 文獻標識碼:A 文章編號:1003-5168(2019)14-0078-02

Analysis of 3bit-ADC to Bottom Plate Sampling and Top Plate Sampling

SU Qing

(Chongqing University of Posts and Telecommunications,Chongqing 400065)

Abstract: The bottom plate sampling circuit is often used to eliminate the influence of charge injection and clock feed-through in the roof ?sample and hold amplifier of classical ADC/DAC. Therefore, this paper used the Cadence Spectre tool to analyze the waveforms of the top plate sampling and bottom plate sampling in the ADC and the parameters such as SNDR. It’s concluded that the stability of bottom plate is better, but the energy consumption is larger than top plate sampling. Because of its lower power consumption, lower distortion and larger SNDR, the climax sampling is generally used in low ADC.

Keywords: ADC;bottom plate sampling;top plate sampling;SNDR

高精度ADC要求采樣保持電路(Sample and Hold Amplifier,SHA)有足夠高的速度與精度,SHA是ADC的關鍵模塊之一,性能制約著高精度ADC的整體性能。電容在采樣電路中起著重要作用,電容型SHA的能量效率更高[1]。在電容型SHA中,主要有頂極板采樣(Top-plate Sampling)和底極板采樣(Bottom-plate Sampling)兩種采樣的開關方式。頂極板采樣中,由于MOS開關管存在電荷注入效應和時鐘饋通效應[2],使SHA電路出現非線性誤差。在經典采樣電路中,底極板采樣技術應用相對較廣泛,主要原因是該方式可以有效消除采樣開關的電荷注入。但由于底極板采樣通過試探法來連接開關,因此相比于頂級板采樣來說,消耗了更多能量,功耗較大。

1 采樣架構

一般ADC的原理結構分為對模擬信號的采樣及對采樣信號的量化編碼兩部分。采樣保持電路結構主要由采樣頻率控制時鐘信號、電容、開關等組成,是ADC的第一級,直接對輸入模擬信號進行跟蹤、采樣和保持,性能直接制約了ADC的整體性能。采樣保持電路將外界連續變化的模擬信號轉化為離散信號并保持足夠的時間以供后級電路進行量化編碼,從而實現輸入信號的從模擬信號到數字信號的轉換。

在采樣電路中,頂極板采樣采用電容采樣開關。與運算放大器相比,電容消耗的功耗和占用的面積較小。輸入模擬信號經過CMOS互補開關后,一端接后級量化電路,另一端接電容開關后接參考地。頂極板采樣利用電容兩端電壓充放電及壓差不變的特性來控制采樣開關的通斷狀態。

底極板采樣利用電容的底極板采樣,上極板保持電荷,在采樣開關斷開前,先隔斷保持電荷與上極板的電荷通路,用以消除電荷注入與時鐘饋通。底極板采樣包括采樣電容、兩個或多個開關。對于使用MOS管做開關的電路來說,還應增加一個非重疊時鐘電路來控制電容充放電的開關。傳統的非重疊時鐘發生器設計采用與或非門以及反相器鏈組成延時單元。通過改變反相器的使用數量或者直接改變MOS管的寬長比,改變延遲時間。

2 底極板與頂極板采樣仿真

在3bit-ADC中,設置仿真中的輸入正弦波信號幅度為0.5V,頻率[fc]為10MHz,采樣頻率[fs]為100MHz。通過對3bit-ADC頂極板采樣和底極板采樣進行分析可知,采樣保持電路中只有頂極板和底極板采樣方式不同,量化編碼電路完全相同。

對于底極板采樣,設置MOS管的3個非重疊時鐘信號分別為clk1、clk2、clk3,輸入高電平為1V,低電平為0V的初始時鐘信號clk1,在保持時鐘周期不變的基礎上對clk1進行處理,得到clk2及clk3。其中,clk2與clk1同相,clk1的高電平帶寬比clk2延遲了100ps;clk3與clk1反相,clk3的高電平帶寬比clk1小200ps,clk1的下降沿與clk3的上升沿之間間隔100ps。

2.1 采樣波形圖

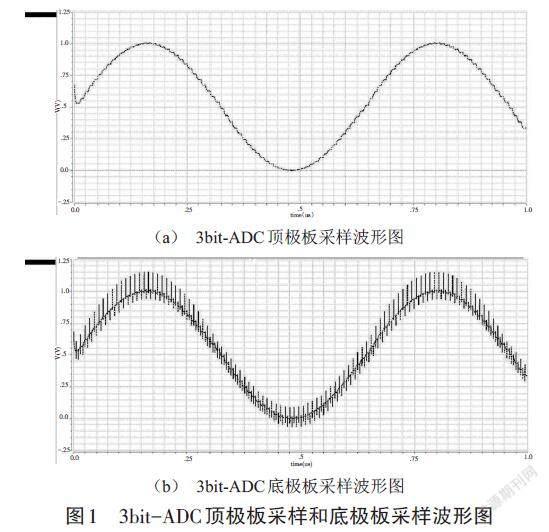

3bit-ADC經過頂極板采樣和底極板采樣后,進行量化編碼前的波形如圖1所示。

在圖中可以明顯看到,頂板采樣中波形比較理想,失真較小。而底極板采樣電路的波形中毛刺現象較為嚴重。這主要是因為底極板采樣電路的電壓有上升也有下降,在開關試探時會出現需重新撥回開關的可能性,增大了誤差。

2.2 3bit-ADC電路的SNDR值

根據經驗值設置采樣電路中CMOS開關的MO管的溝道寬度和長度,[L=2wn],[W=wn]。對[wn]掃描分析得到信號噪聲失真比(SNDR)隨[wn]的變化圖象。分析可知,頂極板采樣圖象穩定性較差,但最大SNDR值比底極板采樣的最大值高。頂極板采樣ADC的SNDR值在[wn]較小的范圍內均比底極板采樣高,說明在該溝道寬度范圍內頂極板采樣性能更好。3bit-ADC理想的SNDR值為:

[SNDRideal=6.02×ENOB+1.76=6.02×3+1.76=19.87]

對頂極板采樣,當NMOS管溝道的寬[wn=10μm]時,[SNDRmax=19.525 3]dB,此時對應的PMOS管溝道的寬[wp=39.050 6μm]。對底極板采樣,[wn=31.622 6μm]時,[SNDRmax=19.422 9]dB,此時對應的PMOS管溝道的寬[wp=63.245 2μm]。

3 結語

通過Cadence Spectre仿真工具分析得到,頂極板采樣在較小的溝道長度和寬度內的失真較小,性能較好。但頂極板電容陣列的寄生電容會引入非線性,一般適用于低位低功耗采樣電路,節省一些開關功耗。底極板采樣有效減小了非線性誤差以及動態失配,提高了ADC的精度。雖然底極板采樣功耗較大,SNDR值稍小,但由于其精度高、穩定性好等優良特性,在實際高精度數模、模數轉換等研究中應用廣泛。

在底極板ADC中,由于傳統非重疊時鐘發生器中的時鐘電路模塊獨立于輸入信號發生器,定義非重疊時鐘屬性的參數在電路集成后不能改變,給器件應用帶來很大限制。因此,在一些研究及生產應用中,通過設置控制電壓,得到占空比不同的輸出信號,從而產生非重疊時鐘,用占空比可調的非重疊時鐘發生器代替傳統非重疊時鐘發生器[3]。

參考文獻:

[1]馬俊.頂極板采樣橋式電容陣列低功耗高速度逐次逼近型模數轉換器的研究與實現[D].上海:復旦大學,2013.

[2]畢查德·拉扎維.模擬CMOS集成電路設計[M].西安:西安交通大學出版社,2003.

[3]張學敏,王衛東.一種占空比可調的兩相非重疊時鐘發生器[J].電路與系統學報,2013(1):427-431.