基于混合SETMOS 結構的超前進位加法器

曲航,劉德州,周海力,侯興華

(中國船舶工業系統工程研究院,北京,100094)

0 引言

在集成電路中,加法是最重要的一種邏輯運算。 通過按不同的方式組合加法器模塊,我們能實現諸如快速加法器之類的許多功能,而增加運算速度并減少基礎加法器電路的復雜程度在實際設計集成電路時非常重要。雖然基于MOS工藝的加法器等電路廣泛應用于現代電子行業,但隨著器件小型化及提升運行速度的需求越來越旺盛, MOS 工藝的局限性逐漸凸顯了出來,例如其最小僅能達到幾百微米級,且具有量子效應和對微小電流不敏感等特性。另外,繼續在已經開發到極限MOS 器件上繼續拓展新應用的經濟效益很低[1]。

相比之下,單電子晶體管(Single-electron Transistor,SET)則擁有極低功耗、更小的納米級工藝制程、以及實現更多的邏輯功能等巨大潛力,這是由于其在縮小空間的同時還擁有其獨有的庫倫阻塞效應。然而目前純粹的SET 器件因靈敏度極高而很容易受干擾,并且必須在較低溫度下才能展現良好的電流特性,甚至不能在一般室溫條件下正常運轉。因此,當前最好的解決方法是將SET 和MOS 工藝結合起來制成一種全新的SETMOS 混合電路,如此便可最大限度地降低SET 器件固有的缺陷。

本文首先將通過基礎SETMOS 混合邏輯電路構建一個加法器,然后在此基礎上發展出一種全新的超前進位加法器(carry look-ahead adder, CLA) ,以此來替代傳統的由全加器組成的加法器,并提高了電路的可靠性及運算速度。

1 SETMOS 基礎邏輯門電路

1.1 單電子晶體管

SET 晶體管結構包含2 個隧道結和數個電容。通常意義上, SET是由源極、漏極、1個夾在2處隧道結之間的“島”、以及控制島內電子數量的門電容所組成的。SET 結構在納米級的電路下具有良好表現,因為它可以基于庫倫阻塞定律精準地將微小的電子一個接一個地傳導,如此便可精細控制電流并降低功耗。

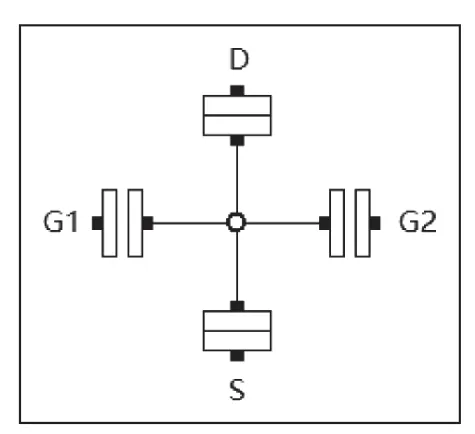

與MOS 管一樣,SET 管也存在源極、漏極和柵極,不同的是后者的源極、漏極為隧道結,而柵極則是集成在SET 管中的電容。通常SET可以包含單個或多個電容,即擁有單個或多個柵極[2]。圖1 展示了一個雙柵SET 管的電路結構,本文主要采用雙柵SET 來組合電路。

圖1 雙柵SET 管

1.2 純SET 結構門電路的局限

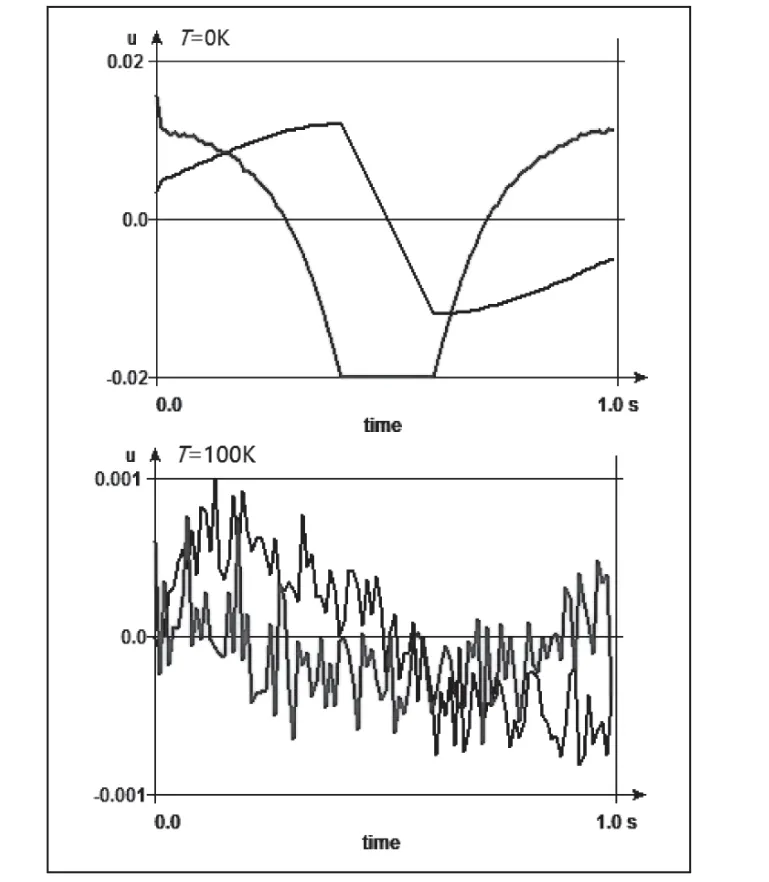

然而,SET管對背景電荷等許多類型的干擾都極為敏感;更有甚者,SET 管只有在溫度極低的情況下才能運行良好,在常溫下工作時則會功能紊亂,這是由于SET 器件工作時所產生的庫倫震蕩現象會隨著溫度升高而幅度逐漸減小甚至幾近消失。相關研究表明SET 管的理想運行溫度十分接近絕對零度[3],至少得保持在比較接近絕對零度的條件下方可維持功能。圖2 展示了軟件仿真的一種純SET 非門分別在0K(-273.15℃)和100K(-173.15℃)時的特性曲線[4],從中可以看到SET 電路在遠遠低于0℃時就已經出現了嚴重的失真現象,且電壓幅度范圍也大為縮水。上述問題極大限制了SET 元器件在實際復雜條件下的應用。

圖2 純SET 非門電路在不同溫度下的特性曲線

與SET 相比,MOS 的對外敏感度和輸出阻抗更低,但電壓增益卻很高,且作為常用器件的MOS 擁有良好的可靠性與環境適應性。這兩類器件在直觀的對外接口和整體功能上都十分相似,具備協同使用的條件。將它們融合起來一定程度上既可結合二者獨有的優點,又能降低雙方各自的缺陷。特別是對于SET 來說,MOS 良好的溫度承受能力具有無與倫比的補償作用[5]。

1.3 SETMOS 混合非門電路單元

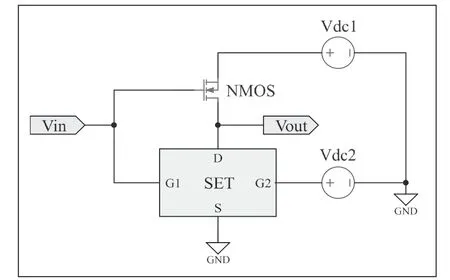

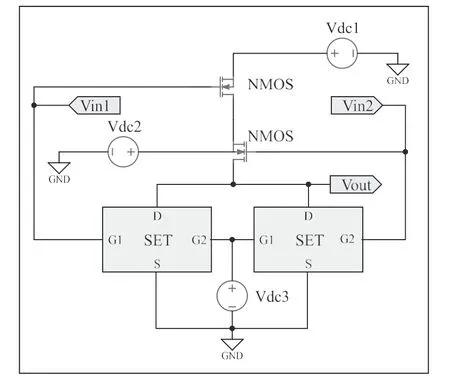

圖3 演示了一種基于SETMOS 混合工藝構建的反相器,即非門。其中Vin表示輸入電壓,Vout表示輸出電壓。功能上它等同于純粹的MOS 非門,但電路上則將下拉MOS 晶體管替換成了1 個SET 管[6]。

圖3 SETMOS 混合器件構建的非門

圖中的SET 選用了MIB 提供的雙柵模型[7],其相關 參 數 設 置 如 下:CG1=CG2=0.3aF,CD=CS=0.3aF,RD=RS=1MΩ。其中CG1、CG2為柵極電容,CD為漏極電容,CS為源極電容,RD為漏極電阻,RS為源極電阻。而SETMOS結構中的MOS 應選用NMOS 來與SET 相匹配[8],本文選用的是CMOSP18 模型。MOS 管的相關參數設置如下:W=500nm,L=180nm。其中W、L 分別為MOS 管溝道的長度和寬度。此外,通常需要提供不低于300mV 來啟動CMOSP18 模型。這里設置Vdc1=365mV,Vdc2=750mV。

圖4 SETMOS 與非門

與同類MOS 電路結構相比,這種設計方式顯著降低了非門的總功耗(約幾百pW)和傳輸延遲時間(低于100ns)[9]。

圖5 SETMOS 或非門

圖6 SETMOS 異或門

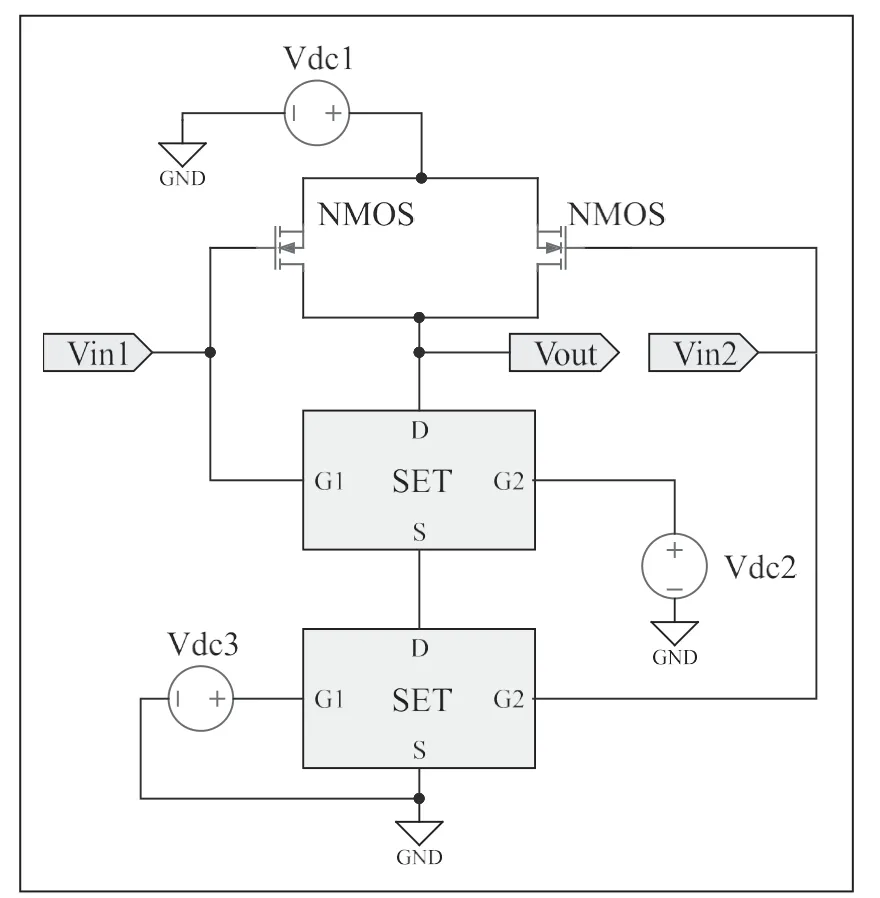

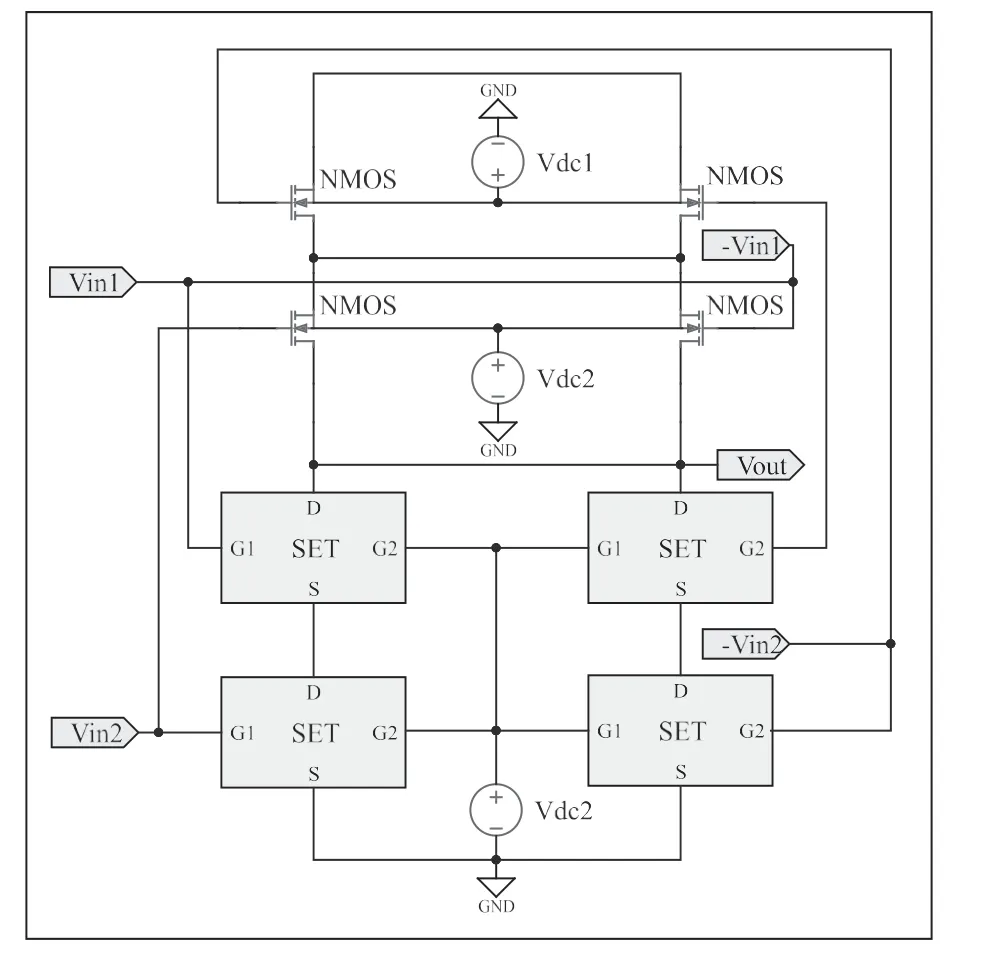

1.4 其他混合邏輯電路單元

同理,我們可以創造出其他由混合器件構建的與非門、或非門和異或門,其電路原理分別如圖4、圖5、圖6 所示。在SETMOS 與非門中,設置Vdc1=365mV,Vdc2=750mV,Vdc3=750mV;在SETMOS 或非門中,設置Vdc1=750mV,Vdc2=750mV,Vdc3=365mV;在SETMOS 異或門中,設置Vdc1=750mV,Vdc2=750mV,Vdc3=365mV。

將SETMOS 非門與上述與非門、或非門串聯起來,就可以得到SETMOS 結構的與門、或門等其他混合邏輯電路。

SETMOS 門電路同常規門電路一樣,可以加以組合連接從而形成能執行更復雜功能的集成電路。但需要注意,在一條電路線路中不要同時串聯過多的SETMOS 門,因為SETMOS 電路的輸出有時會有幾毫伏甚至十幾毫伏的衰減,在不添加任何放大電路的前提下,串聯SETMOS 電路中的衰減經過疊加后會變得很可觀,導致傳輸線路后方的門電路從前方電路得到的輸入信號越來越微弱,對閾值的設定的精度要求將變得十分苛刻。此外,由于SET 本身容易受干擾的特性并未因與MOS 融合而完全消除,各種形式的干擾也更容易使后方門電路得到的輸入波動從而干擾閾值判斷。

由于本文討論的CLA 電路結構具有明顯的并行特征,因此通過SETMOS 門電路來構建CLA 可以在很大程度上規避傳統加法器在進行多位運算時需要串聯許多全加器的問題,電路的可靠性將有所保障。

2 SETMOS 超前進位加法器

2.1 CLA 原理

加法運算經常需要進位,而可以實現單獨1 位加法并計算進位的全加器是最基礎的加法器之一,同時也是組成其他大多數邏輯運算電路的基本邏輯單元之一。1 個單位全加器可由2 個與門、2 個或非門以及1 個或門組合構建。 若想實現多位相加功能,只需組合數個最基本的單位全加器,也就是把前一位全加器的進位輸出與后一位全加器的進位輸入串聯,如此便生成了脈沖進位加法器。

脈沖進位加法器結構簡單卻有很多局限,因為如果想要運算得到最終結果,加法器的每一位都需要先從上一位獲悉進位結果才能進行本位求和,進而再將本位進位傳遞給下一位,這種一次只能處理一位數據的運算方式將大幅降低電子器件的運行速度[10]。除此之外,如果直接使用SETMOS 混合設計來實現全加器進而實現脈沖進位加法器,其可靠性更加難以得到保證,因為SETMOS 混合后的電路對外界干擾仍然有一定的敏感性,一旦構成脈沖進位加法器的某一位全加器因受到干擾而產生錯誤的進位,將會影響到全部后續其他位的運算結果。

為了提高SETMOS 多位加法器的運算速度和電路可靠性,組建具有平行運算結構的超前進位加法器更加合理。本文所展示的例子是SETMOS 結構下的3 位超前進位加法器。

在數學上,加法器第i 位的運算結果Si可由下面公式求得:

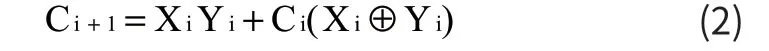

式中Xi和Yi分別表示第i 位的加數和被加數,Ci則表示來自前一位的進位。而第i 位向第i+1 位所提供的進位Ci+1則如下所示:

為了切斷進位鏈,如果設定2 個中間變量Gi和Pi如下:

可得到:

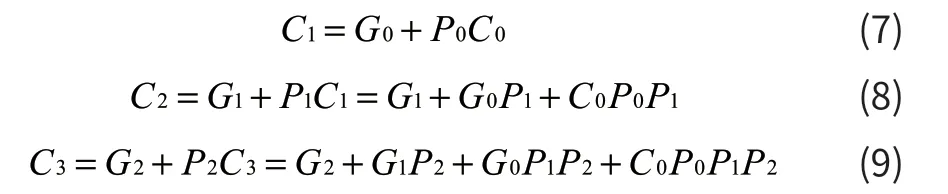

展開公式(6)后,各位的Ci可由下列公式表示:

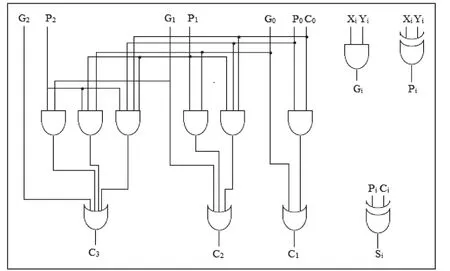

通過公式(3)、(4)、(5)、(7)、(8)、(9)可以設計出3 位CLA 的原理圖,具體如圖7 所示。

從原理圖中不難看出,每一位的進位輸入Ci是同時獨立生成的,不同位的Ci的與其他位的進位輸出Ci+1沒有直接關系,因此可以同時生成全部各位的求和。

2.2 基于混合電路的CLA

將先前設計的各SETMOS 邏輯單元帶入圖7 所示的原理圖中,最終我們可以得到采用SETMOS 器件構建的3 位CLA。

圖7 3 位CLA 原理圖

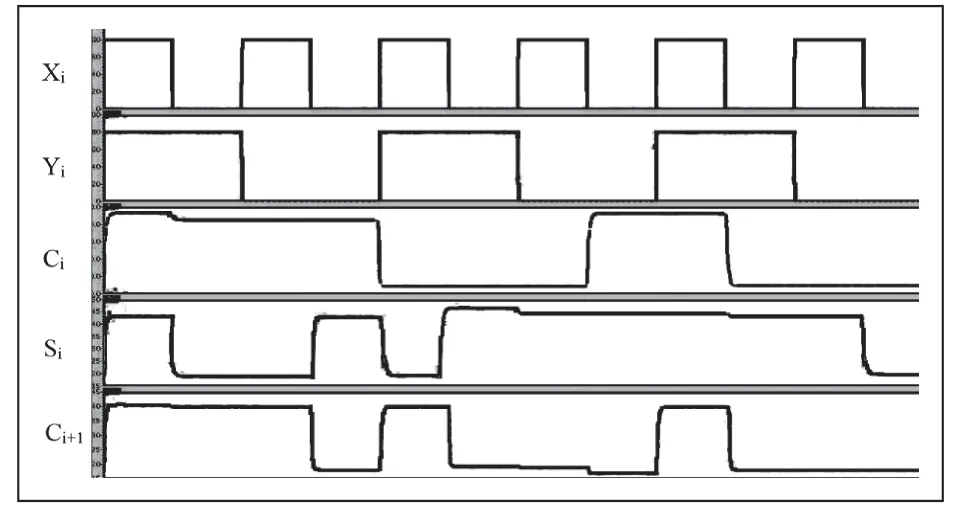

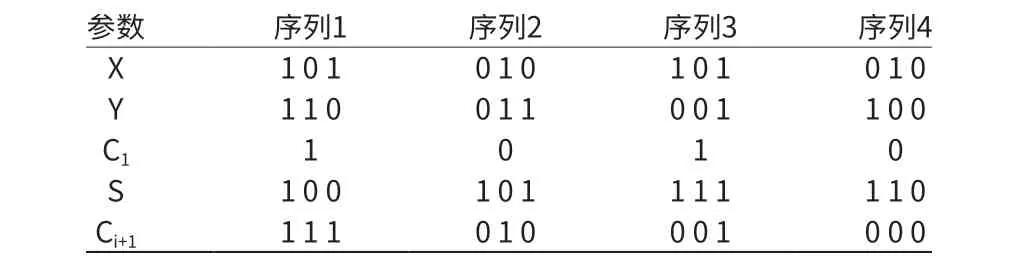

為了驗證基于混合SETMOS 結構CLA 的正確性,需對其進行功能性能測試。這里我們通過CADENCE 進行軟件仿真,并分別按照表1 中的數值賦予加法器的輸入X、Y、C1,它們的大小可以在0V 及100mV(或低于100mV 但高于80mV 的某個值)兩個電壓值之間選取。其中X、Y 均為矩形脈沖數組,形成多種不同的3 位二進制加數組合對,而C1則表示X、Y 相加時來自第0 位的進位,每一個C1對應一組X、Y。所有的測試均模擬在室溫(27℃)條件下進行。

3 測試結果及分析

3.1 功能測試結果

軟件仿真的結果如圖8 所示,從圖中可以看到SETMOS 加法器的脈沖波形基本良好。將測試結果轉換成二進制數值的形式后,得到的運算結果如表1 所示。其中Ci表示進行第i 位加法運算時來自之前一位的進位值,S 表示X、Y、C1相加后得到的最終3 位加法運算結果,Ci+1表示第i 位運算后應當向下一位、即第i+1 位輸送的進位值。

以序列1 的輸入組合為例,加數X 和Y 分別為3 位二進制數1 0 1 和1 1 0,他們在相加時也要同步與來自第0 位的初始進位C1相加,此刻C1等于1。經過SETMOS 架構的CLA 運算后得到的3 位二進制輸出結果S 為0 1 1,而每一位運算所產生的的對下一位的進位Ci+1為1 1 1。

總結一下可以簡單描述為:X、Y、C1相加后得到了結果為0 1 1 的3 位二進制數值,并繼續向3 位CLA 以外的第4 位產生了高電平進位C4。這一結果完全符合加法運算規律,同理其他序列的運算組合經由SETMOS 架構的CLA 得到的結果也完全正確。輸出波形上,只要將閾值設置在高低電平中間位置即可妥善將二進制的0、1 區分出來。因此從功能性能的角度來看,SETMOS 混合器件可以在常溫下實現超前進位加法計算。

圖8 3 位SETMOS 結構CLA 的輸入輸出脈沖仿真結果

表1 SETMOS CLA測試輸入及結果(27 ℃)

3.2 性能提升

(1)電路復雜度:相較于MOSFET, SET 管內已經集成了電容結構,因此在設計SETMOS 混合電路CLA 時不需要額外添加電容,更加便于設計連線。

(2)尺寸:作為納米電子器件的SET 拉低了混合電路的整體尺寸,同時由于不需要額外添加電容進一步節省了空間。

(3)功耗:3 位SETMOS 結構的CLA 中間及輸出電壓功耗及發熱情況均不高,一般只有幾納瓦甚至更低。

(4)運算速度:與同等復雜程度的MOS 加法器相比,SETMOS 加法器運行速度更快,這是由于每個混合邏輯電路門均比純MOS 門節省了十幾甚至幾十納秒的間隔時間,而基于超前進位加法器的原理,最終總共可以節省4log4N倍的間隔時間,其中N 表示加法器位數。通常3 位CLA 在SETMOS 結構下可以比通常的MOS 加法器快0.6~3.5 微秒。

4 結語

本文所介紹的基于混合SETMOS 晶體管結構的超前進位加法器擁有比常規MOS 加法器更快的運行速度和更小的尺寸,并且通過結合SET 與MOS 兩種類型的器件一定程度上彌補了SET 固有的缺陷,使其初步具備實際應用的條件。接下來的研究方向與改進空間主要在于能否實現SET 器件在更加惡劣環境、尤其是高溫條件下的正常工作。一旦在溫度問題上形成突破,SET 器件將有很大潛力成為下一代集成控制電路的核心部分,實現電子制造設計領域的重大飛躍。