基于STM32+FPGA的存儲控制系統優化設計

許 艷,孟令軍,謝玲芳,朱 珊,王靜波

(中北大學 儀器與電子學院, 太原 030051)

隨著圖像采集技術的不斷發展,對圖像的采集存儲系統的要求也越來越高,比如軍事領域炮彈姿態的獲取、飛機飛行過程中的遙測監控、高速公路的路況獲取等都離不開圖像的采集存儲,在實驗過程中將運動狀態記錄下來,為線下的研究分析提供實驗依據。因此對存儲控制系統進行優化設計也是至關重要的[1]。

傳統的數據存儲控制系統具有通信復雜,IO資源緊缺,成本高,體積大、功耗高的特點;意外掉電,系統錯亂,無法正常記錄,并且每次上電記錄前都需要擦除FLASH數據,經常擦除會降低FLASH芯片壽命[2],這會使得前期的系統開發效率低下,研發周期較長。因此,針對行業需求,研究并開發了一種基于STM32+FPGA的存儲控制系統的優化設計,該系統采用STM32F103(以下簡稱STM32)作為主處理器,它具有精簡指令集以及功耗低、成本低等特點;FPGA作為協處理器可編程邏輯強,并行處理速度快,STM32與FPGA相結合可以實現性能互補,從而提高系統的穩定性。該設計解決了意外掉電存儲的問題,在通信復雜、資源短缺的情況下用數據拼接方式進行通信,減少IO口資源的占用,減小體積,使模塊趨于小型化,降低電路復雜度,從而降低系統開發成本。該系統還具有可移植性強和可維護性好的特點,可為其他相關系統研發提供一種參考方式。

1 總體方案設計

該系統采用STM32+FPGA的主協處理器進行頂層設計,主要包括三大模塊:供電與掉電檢測模塊、422差分指令的接收、解析、編幀發送模塊和數據存儲及發送模塊。系統框圖如圖1。

圖1 系統組成框圖

系統每次上電后等待上位機發送系統開啟工作指令,上位機下發指令通過讀數盒到STM32,STM32作為主控,完成了422差分指令的接收、解析、編幀、數據拼接方式的指令傳輸以及電源電壓的監控;存儲板FPGA接收指令,進入指定的工作狀態;當上位機下發啟動記錄指令時,存儲板將外部數據進行編幀存儲寫入FLASH,上位機下發下載指令時,對存儲板進行數據回讀,將數據以LVDS的形式發送至讀數盒,讀數盒轉換成USB上傳給上位機,存儲板在意外掉電時存儲每次掉電時FLASH的當前地址[4]。系統工作的主要指令有:自檢、復位、啟動記錄、停止記錄、下載、下載取消及容量查詢。

2 系統主要硬件設計

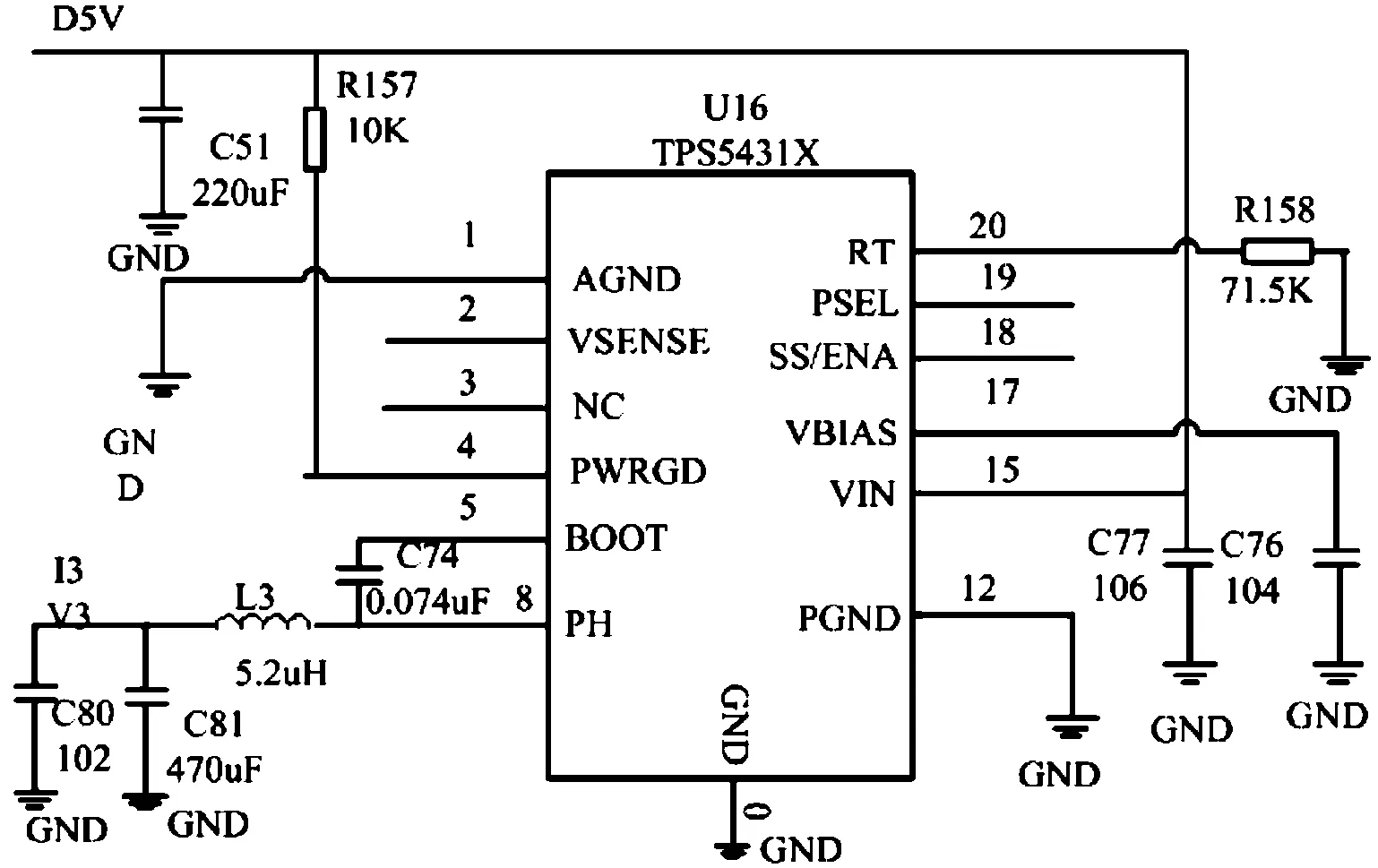

2.1 電源模塊設計

該設計的供電系統采用5 V電源適配器供電,控制系統直接采用5 V電源,經過一個肖特基二極管,二極管的作用是防止電流倒灌,這種設計既能減小干擾又不會損壞設備。此外,系統還需要3.3 V、2.5 V及1.2 V電壓,分別有開關電源模塊TPS54316、TPS54315與TPS54312來輸出3.3 V、2.5 V及1.2 V。圖2為開關電源模塊電路原理圖。

圖2 開關電源設計原理圖

2.2 接口模塊設計

存儲板和機箱讀取盒之間的通信接口采用的是LVDS接口,LVDS接口可以最大限度地減少影響遠距離數據傳輸信號的干擾因素,滿足設計系統測試要求。為了便于在惡劣環境中進行測試,應用了性能最好的七類全屏蔽雙絞線作為LVDS傳輸線。這種類型的網絡電纜在雙絞線的基礎上增加了一個高效的屏蔽網絡層,可以有效地屏蔽大氣顆粒子對信號產生的干擾[5],為方便LVDS線纜拔插,采用了RJ45接口插槽,圖3是RJ45網口傳輸接口原理圖、圖4是LVDS驅動電路設計原理圖。

圖3 RJ45傳輸接口原理圖

圖4 LVDS驅動電路設計原理圖

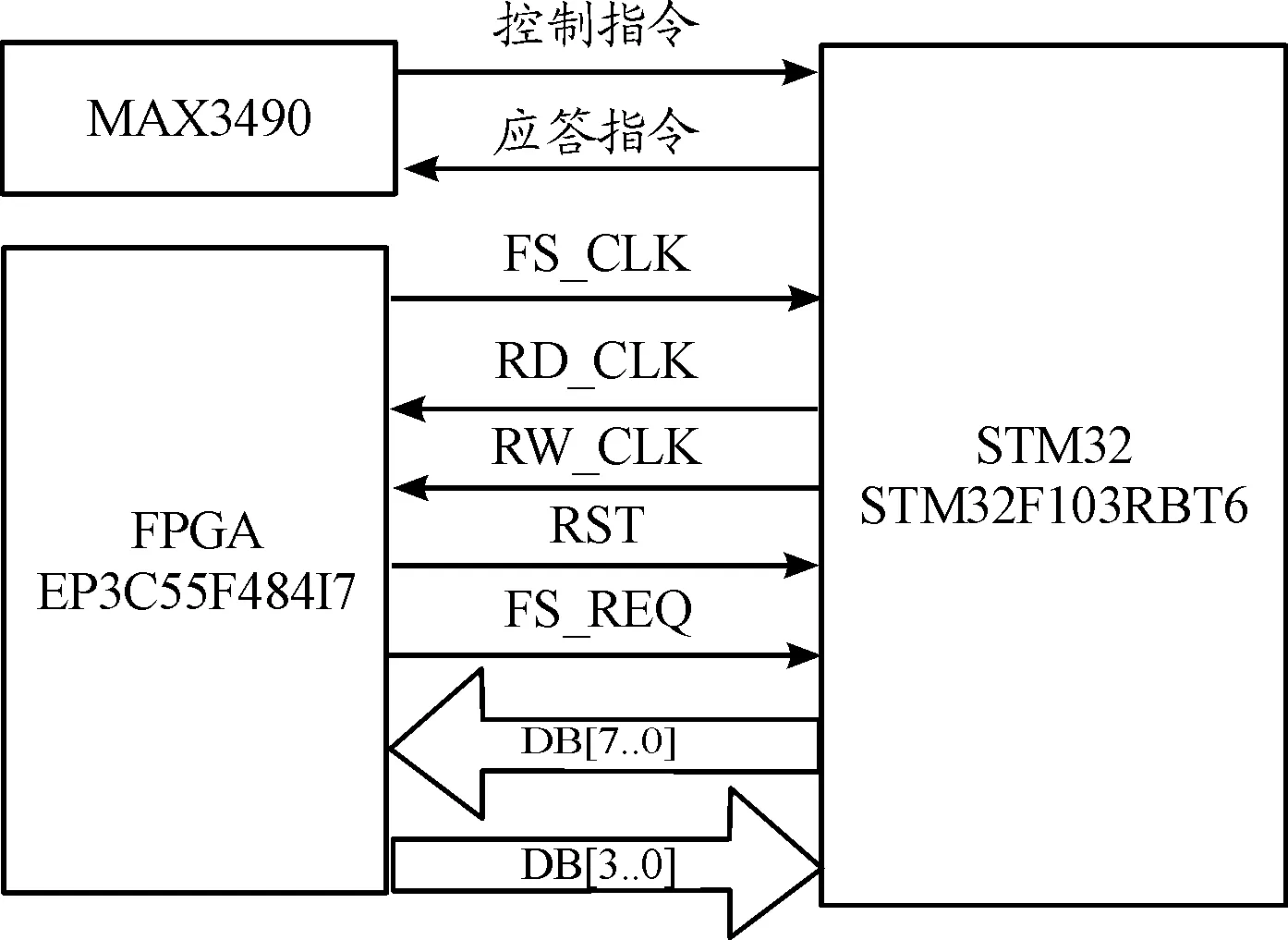

2.3 存儲控制模塊設計

存儲模塊主要由四塊鎂光8Gbytes的FLASH芯片和一塊FPGA芯片組成。STM32控制著存儲板模塊復位、自檢、啟動記錄、停止記錄、擦除、下載、下載取消動作,STM32與存儲板之間的硬件連接結構示意圖如圖5所示。

圖5 STM32與存儲板硬件連接結構示意圖

STM32通過8位數據線給FPGA下發指令,FPGA收到指令后會給一個請求信號FS_REQ,之后STM32通過4位數據線回讀FPGA給出的數據信息,由于STM32F103引腳較少,存儲模塊通信復雜,IO 資源緊缺,采用數據拼接的方式接收數據能夠有效節約雙方的通信資源。

3 系統的軟件設計

3.1 掉電監測

電源供電維持著一個電子系統的工作,但并不是關閉電源系統就會立即停止工作。電源關閉后,一般系統都可以繼續正常工作數個毫秒或者數個微秒,本系統的掉電檢測正是利用系統掉電后短暫的延遲效應,監測系統電源[6]。當STM32監測到供電電壓VDD低于閾值時會觸發PVD掉電中斷,系統進入中斷服務函數進行緊急處理,立刻給FPGA輸出一個掉電信號。存儲板FPGA連續判斷到掉電信號有效時得知系統即將掉電,存儲模塊可以在系統完全掉電之前將當前地址信息等進行存儲,下次上電時即可重新讀出掉電時的存儲地址,避免了每次上電后重新擦除再記錄,節約系統開發周期,有效的防止了意外掉電系統進入紊亂狀態。掉電監測的工作流程框圖如圖6。

掉電信號檢測如圖7所示。圖7(a)中①是系統外部供電直接切斷電源后的示波器信號圖,②是系統內部5 V供電的電壓下降曲線圖,時間單位是1 ms。圖7(b)中①是觸發PVD中斷后輸出的掉電信號,②中的FLASH存儲掉電信號所用的時間信號線(低電平時間段為存儲所用的有效時間<200 μs),單位是100 μs。由圖7(a)可知系統完全掉電最少需要3 ms的時間,圖7(b)可知,存儲模塊從檢測掉電信號到完成掉電信息的存儲需要的時間小于600 μs,因此,掉電監測模塊可以滿足系統工作要求。

圖6 掉電信號檢測工作流程框圖

圖7 掉電信號檢測

3.2 多路指令編幀

本控制系統通過串口中斷和定時器中斷完成了多條422指令的接收,編幀處理。上位機通過RJ45網口下發指令至讀數盒,然后將422指令發送到STM32,STM32解析編碼下發指令字給存儲板FPGA。

存儲板FPGA在WRCLK的下降沿接收STM32發送的指令,FPGA接收完成后進行指令校驗解析并下發至FLASH控制器,回讀FLASH數據,并將回讀結果傳輸給STM32。

STM32在RDCLK的下降沿接收存儲板的數據信息寫入內部FLASH,時序如圖8所示,并進行編幀處理,給出應答指令上傳至上位機。主要包括接收FLASH壞塊數、停止記錄的結束地址、ID字比較結果及指令反饋。

圖8 STM32讀數據時序圖

STM32接收FLASH數據使用了4位數據端口,采用數據拼接的方式接收FPGA數據,即4位數據為一組進行接收,STM32兩個讀時鐘接收1Byte的數據,數據拼接過程如圖9所示。STM32通過PB5、PB6、PB7、PB8 進行IO口數據接收,定義一個16位變量DATA_H,將接收的數據右移1位后再與0x00f0相與,同理定義一個16位變量DATA_L,將接收的數據右移5位后再與0x000f相與,兩個變量各自相與后的和相加組成了一個1Byte數據,即兩個讀時鐘完成一字節的數據接收,多次測試,系統穩定,能夠準確傳輸。此設計有效的節約了4個IO口,STM32F103價格便宜,IO相對較少,本次實驗也是一次數據接口的新嘗試,在數據接口通信復雜,資源緊缺的情況下可以采用此方案設計,為數據接口通信設計提供一種新思路,節約資源,降低開發成本。

圖9 數據拼接過程圖

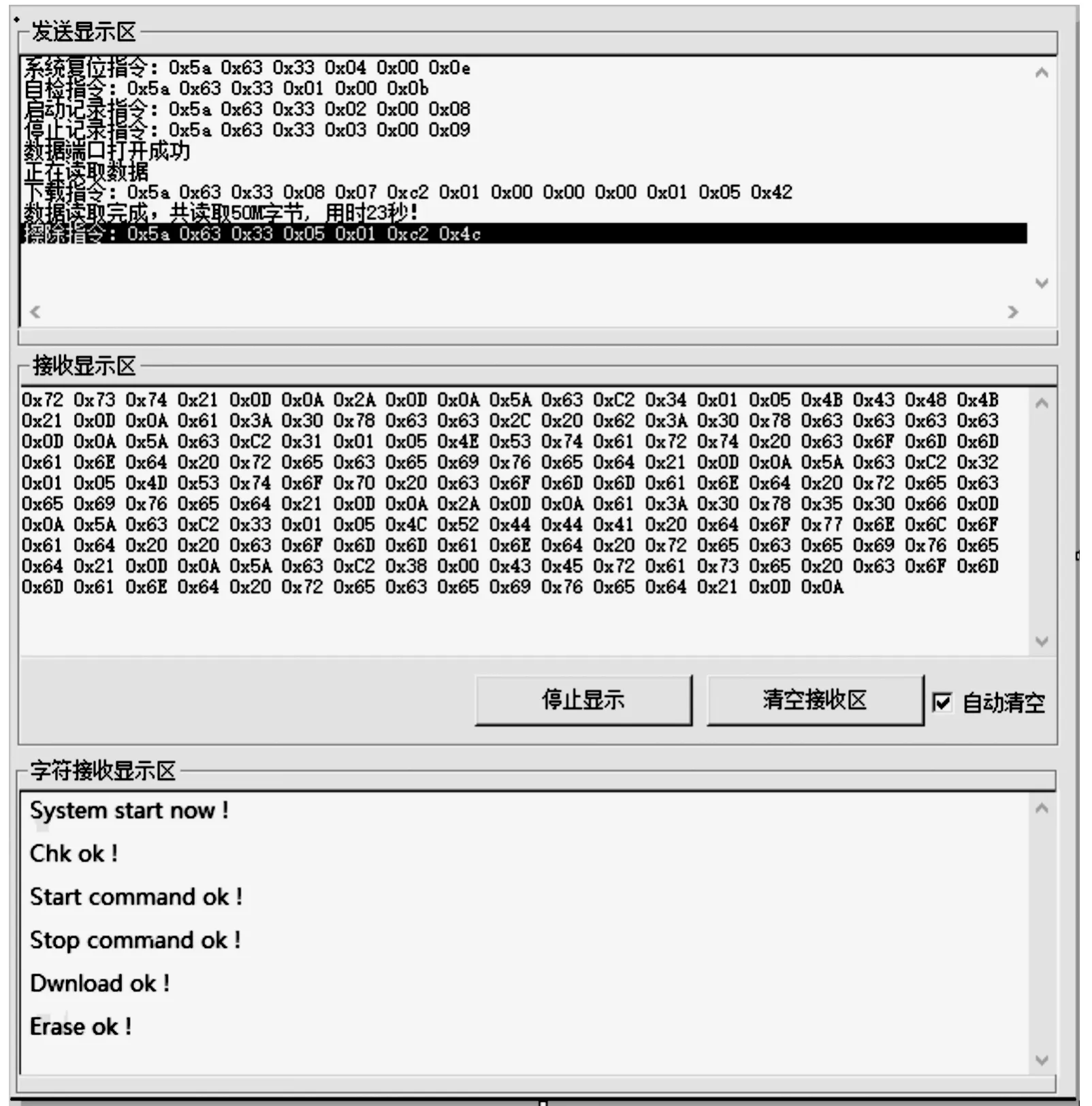

本控制系統上位機采用VB編程,人機交互友好,界面顯示清晰。系統上電后通過上位機發送指令,發送的指令顯示在發送顯示區;接收的應答指令顯示在接收顯示區,指令的含義在字符顯示區顯示,下載回讀的數據以文件的形式存儲在電腦磁盤,便于提取分析,數據回傳無誤。控制系統上位機測試結果如圖10所示的操作界面。

圖10 上位機操作界面

3.3 數據存取

數據存儲單元主要包括數據接收、數據緩存、flash控制等模塊。其功能框圖如圖11所示。

本系統采用8 Gbytes的鎂光FLASH,每塊FLASH有16 384個BLOCK,采用FLASH的第零塊BLOCK不同頁存壞塊數、系統的啟動記錄次數、停止記錄地址以及每次系統意外掉電的結束地址[7],在下次啟動記錄時找到上次的啟動次數和結束地址,分別對應累加后再開始新一次的記錄。發送下載指令讀取FLASH中的數據,其回讀結果如圖12所示,用Matlab進行數據分析處理提取頁計數結果如圖13所示,分析可知數據無丟幀亂碼現象,多次測試,系統穩定,數據回傳正確。

圖11 數據存儲功能框圖

圖12 數據回讀結果顯示

4 結論

該系統分別從硬件和軟件方面對存儲控制系統進行了系統優化,利用STM32強大的內部資源與FPGA靈活的操控性能進行系統設計,實現了功能互補,符合系統優化的原則[8]。系統采用PVD監測系統電源VDD,給出掉電信號后有效存儲數據,保證系統工作的穩定性及準確性。另外系統采用數據拼接的方式接收,有效的節約通信雙方的IO口資源,在綜合性強、通信復雜度高資源不夠用的情況下,此種方法能夠有效的減少IO口的使用,節約資源,并且節省電路板空間、降低系統開發成本。該系統還具有良好的可移植性和可維護性,具有很好的實用價值。