快速鎖定鎖相環技術綜述

許莎莎 盧萌

【摘 要】鎖相環是把輸出相位和輸入相位相比較的負反饋系統。快速鎖定的鎖相環電路一直以來都是鎖相環研究工作中的重點。本文對快速鎖定鎖相環技術做了綜述性介紹,歸納得出快速鎖定鎖相環的發展歷程及研究現狀。

【關鍵詞】快速鎖定;鎖相環;專利分析

中圖分類號: TN763.3文獻標識碼: A文章編號: 2095-2457(2019)30-0219-002

DOI:10.19694/j.cnki.issn2095-2457.2019.30.112

1 鎖相環技術簡介

鎖相環是一種自動調節系統,檢測兩信號的相位差,主要控制的是信號的相位而不是電壓幅值。在鎖定狀態下,鎖相環輸入信號的相位差值為零或保持不變,如果出現相位差,一種控制機理會作用在振蕩器上,之后將振蕩器的輸出信號反饋回去,使相位差值不斷減小,直到最后使輸出信號的相位與參考信號的相位相同,保持在鎖定狀態。下圖為鎖相環的基本結構,這個控制回路可以使輸出信號和輸入信號的頻率和相位同步。

圖1 鎖相環的基本結構框圖

2 快速鎖定鎖相環的主流技術

目前針對鎖相環的研究工作,大多在選取合適結構的基礎上,致力于如何提高電路的性能,包括低噪聲、寬輸出頻帶、高輸出頻率、低工作功耗和低響應時間等性能。其中鎖定時間是鎖相環的一項重要指標,在快速移動設備和藍牙收發技術等電子系統中都需要具有快速鎖定功能的鎖相環。

目前快速鎖定鎖相環領域的研究主要涉及以下四類:延遲鎖相環,電荷泵鎖相環,擴展捕獲帶寬,存儲鎖定電壓。其中延遲鎖相環和電荷泵鎖相環技術發展較多,技術相對成熟。接下來對主流技術進行說明。

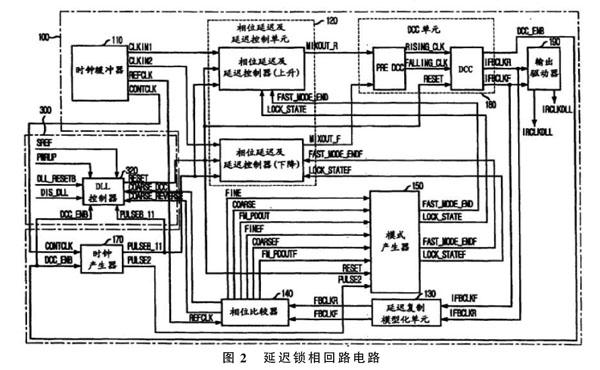

1)延遲鎖相環。以一個專利為例說明,申請號為CN200610159334A(發明名稱:延遲鎖相回路電路,申請人:海力士半導體有限公司)的專利技術方案為(參考圖2):提供一種與外部時鐘同步地操作的同步存儲器裝置,其包括:DLL,其用于執行相位更新以產生鎖定狀態的DLL時鐘,并在該鎖定狀態下以小于一個單位延遲的延遲量實施該相位更新;及控制單元,其用于在該鎖定狀態被外部變化破壞時重設該DLL,從而使其能夠在鎖定狀態由于指示延遲復制模型化單元的延遲在該鎖定狀態下的突然變化的外部影響(諸如tCK或電源電壓VDD的變化)而被破壞時,迅速再次恢復該鎖定狀態。

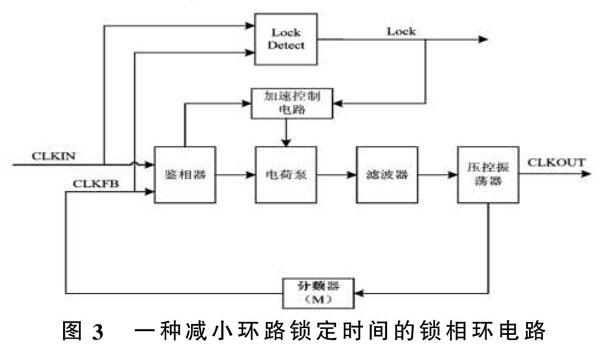

2)電荷泵鎖相環。以一個專利為例說明,申請號為CN201610525483(發明名稱:一種減小環路鎖定時間的鎖相環電路,申請人:中國電子科技集團公司第五十八研究所)的技術方案為(參見圖3):在該鎖相環電路中,電荷泵(CP)的電流源分為兩部分,并分別由兩個控制電路來控制輸出:一個是由鑒相器的輸出信號直接控制,另一個是由鑒相器輸出信號與相位鎖定檢測電路輸出的Lock信號一同控制。該電路在PLL系統鎖定的過程中開啟由Lock信號控制的電流源部分來增加CP的輸出電流,提高壓控振蕩器(VCO)控制電壓的響應速度、增加環路帶寬來減小環路鎖定所需的時間,從而實現PLL系統的快速鎖定。

圖3 一種減小環路鎖定時間的鎖相環電路

圖4

3)擴展捕獲帶寬。以一個專利為例說明,申請號為CN00800446A(發明名稱:鎖相環裝置,申請人:松下電器產業株式會社)的技術方案為(參見圖4):提供一鐘鎖相環裝置,它能根據復制信號檢測相位信息,以及根據相位信息的瞬時變化檢測頻率信息,與模擬鎖相環電路的捕獲區相比,它具有更寬的捕獲區,當鎖相環電路被數字化時,本發明能高速執行相位鎖定。

4)存儲鎖定電壓。以一個專利為例說明,申請號為CN94109157(發明名稱:PLL頻率合成器和使用該合成器的高速頻率鎖定法,申請人:日本電氣株式會社)的技術方案為(參見圖5):PLL頻率合成器包括:AD變換器,存儲單元,DA變換器,環路濾波器,壓控振蕩器,控制單元。其中AD變換器接收頻率穩定狀態中的頻率控制電壓并將頻率控制電壓變換為相應的數字信號;存儲單元存儲AD變換器發出的數字信號;DA變換器將存儲單元中的數字信號變換為相應的頻率控制電壓模擬信號;控制單元可控制AD變換器和DA變換器的變換,并控制從存儲單元讀取數字信號;環路濾波器在頻率合成器起動之前,將模擬信號的輸出電壓由控制單元加到壓控振蕩器上,可穩定地實現高速頻率鎖定。

圖5

3 總結

本文針對快速鎖定鎖相環的主流技術進行了分析,通過對快速鎖定鎖相環技術專利文獻的研究發現,快速鎖定鎖相環的技術相對已經很成熟了,隨著現代電子技術的發展,對于快速鎖定鎖相環性能的要求越來越高。我國的快速鎖定鎖相環技術正處于快速發展的階段,然而由于起步較晚,與國外還存在一定的差距,因此具有很大的發展空間。

【參考文獻】

[1]王麗,CMOS快速鎖定鎖相環的研究與設計[D].合肥工業大學,2015,04.

[2]任傳陽,快速鎖定電荷泵鎖相環研究與設計[D].山東大學,2016,04.