SVDU的多協處理器并行化方法研究

趙 洋,汪 亨,吳延群,余 波

(中國核動力研究設計院 核反應堆系統設計技術重點實驗室,成都 610213)

0 引言

人機界面是人與設備之間進行交互的重要媒介。人通過人機界面對計算機所控制的實際設備進行控制,同時人機界面會將計算機采集的設備信息反饋給用戶,以便用戶分析并作為決策的重要依據之一。根據不同的調查統計,在核電站中發生的重要事故和故障中,約60%的事故是由操作員的失誤造成的[1]。因此,人機界面的功能重要性在核電系統中不斷加強。

SVDU 作為安全級DCS 配套的數字化人機界面,其核心功能主要由基于CPU 的軟件技術實現。為保證SVDU設備的高可靠性,其相關軟件開發往往遵循“單任務運行”“限制中斷使用”“固定周期運行”“靜態內存分配”等保守性設計原則。這些設計原則使得SVDU 的應用功能開發與技術指標要求呈現矛盾狀態,難以兼得。在工程實踐中,犧牲功能豐富性和完善性來保證人機響應時間、頁面刷新速率等技術指標要求會使SVDU 的功能偏向簡單化,有時并不能夠完全滿足安全級DCS 配套人機界面的某些功能需求。

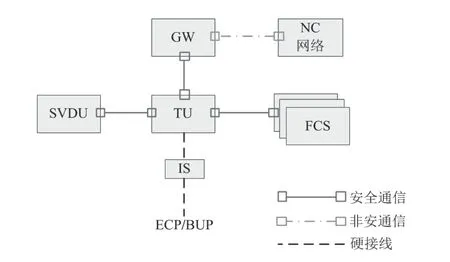

圖1 安全級DCS簡化連接圖Fig.1 Simplified connection diagram of safety DCS

如果能夠以新的設計方法來提升SVDU 設備的運行效率,使得功能和性能同時兼顧,又能有效保證可靠性,對于保障核電安全可靠運行具有重要意義。

1 SVDU功能分析

國內外應用于核電廠的SVDU 產品主要包括TXS QDS、MELTEC SVDU、Tricon SVDU 以及NASPIC SVDU。雖然各產品采用的技術不同,但在安全級DCS 中發揮的作用類似。SVDU 作為安全級DCS 配套的人機界面,為操作員提供狀態監視、手動干預系統運行的能力。圖1 是安全級DCS 中的簡化連接圖,各模塊的功能如下:

GW:網關站(Gate Way),實現安全級DCS 與NC 網絡的通信隔離。

TU:傳輸單元(Transfer Unit),實現SVDU、FCS、TU、GW 之間的數據中轉傳輸,通過TU 能夠將各個單一的站點通信互聯,構成較大的控制通信網絡。

FCS:自動控制單元(Fieldbus Control System),執行數據采集、邏輯運算及輸入輸出控制。

ECP/BUP:獨立于安全級DCS 的應急盤(Emergency Control Panel)和后備盤(Backup Panel)。

SVDU:安全級圖形顯示單元,通過TU 獲取需要監視的網絡變量,通過TU 將控制指令發送到FCS 中。

在安全級DCS 中,SVDU 需要完成的功能包括但不限于:

1)反應堆保護系統功能的閉鎖及復位。

2)通道旁通狀態顯示。

3)長時間PAMS 變量記錄和趨勢顯示。

4)T3 定期試驗。

5)停堆斷路器復位。

表1 SVDU設備功能與系統功能的關系Table 1 The relationships between SVDU device functions and system functions

在系統運行中,SVDU 的故障可能會導致操作模式由KIC 模式切換到BUP 模式[2]。因此,SVDU 的功能大多可由BUP 代替。總體上,SVDU 發揮著與BUP 相似的功能。在設備級手動控制方面,可以認為SVDU 與BUP 構成了多樣化的人機輸入手段;在狀態監視方面,SVDU 借助自身的大屏幕和多種顯示形態的圖形控件,能夠代替大量BUP 盤面布置的信號狀態指示燈、參數監視儀,使得BUP 僅保留必要的信號監視,能夠簡化BUP 的設計復雜度。

2 SVDU設備底層支撐技術分析

從安全級DCS 整體的角度來看,SVDU 主要執行的系統功能有兩個:

1)設備級手動控制。

2)實時狀態監視。

為滿足以上系統功能,SVDU 需要具備以下設備功能:

① 安全通信:能夠與TU 進行雙向安全通信。

② 人機輸入:具備接收來自用戶人機輸入指令的能力。

③ 畫面顯示:以圖形、數值、文本、趨勢及日志等多種顯示形態反映狀態監視的實時值和歷史值。

④ 用戶配置信息解析:SVDU 是一款組態型設備,所有顯示畫面均在離線組態后下裝至設備中。因此,需要具備解析用戶組態配置信息的功能。

SVDU 系統功能與設備功能的關系如表1 所示。

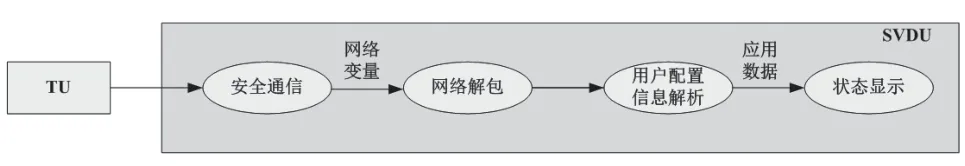

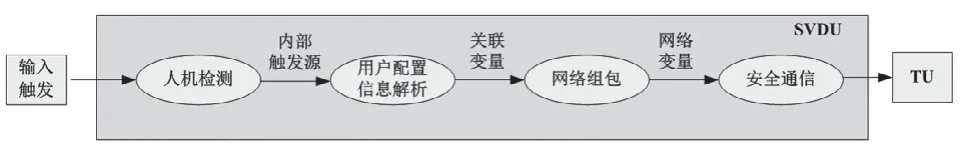

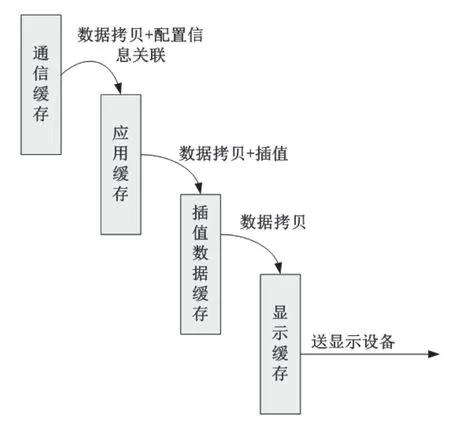

圖2、圖3 描述了狀態監視和設備級手動控制的數據流向及其經過的處理環節。

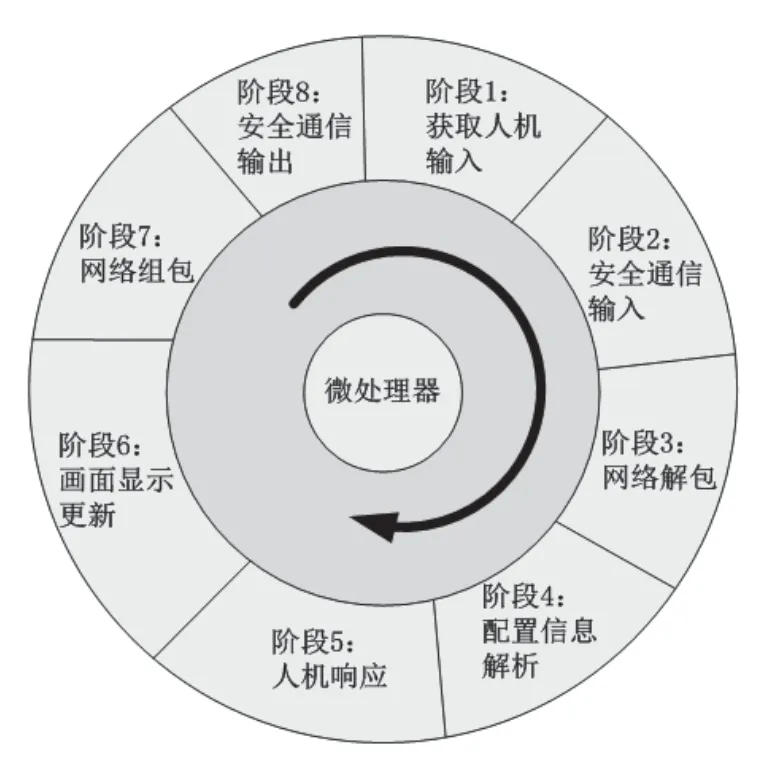

SVDU 軟件在滿足“單任務運行”“固定周期運行”等設計原則的前提下,在一個固定的運行周期內,將按照圖4 所示機制固定地分配時間片段,確定、順序地執行各項設備功能。

如果SVDU 中某個控件涉及的設備功能過于復雜,圖4 中的各個時間片段將增加,進而增加運行周期,降低SVDU 人機響應和數據更新速度。在“限制中斷使用”“無人機輸入輸出緩存”的設計中,系統還有可能丟失人機輸入信息,嚴重影響SVDU 安全功能的可靠性。

圖2 狀態監視的數據流向Fig.2 The data flow of status monitor

圖3 設備級手動控制的數據流向Fig.3 The data flow of device-level manual control

圖4 SVDU固定時間片段運行機制Fig.4 SVDU running mechanisms based on fixed time slice

航空和工業控制等諸多領域對計算系統要求越來越高,嵌入式計算機系統日益復雜[3]。因此,不得不引入操作系統來實現任務調度和硬件管理。與此類似,某些SVDU 產品中也使用基于實時性操作系統的多任務處理機制來提升并發數據處理能力。任務管理和調度是操作系統的核心功能之一,而任務調度必然會引入程序指針重賦值的軟件或硬件中斷,帶來嚴重的不確定性,背離了安全級軟件的設計原則;同時會導致軟件的確定性評估以及驗證確認工作變得復雜且困難。此外,操作系統的引入,使得硬件資源需求提升,硬件復雜度的增大反而會導致SVDU 的可靠性預計指標下降。

3 多協處理器并行化方法在SVDU中的應用

“單任務運行”“固定周期運行”等設計約束本質上是為了保證SVDU 軟件的行為簡化,有利于可靠性分析。如果能將圖4 所示各個時間片的功能聚合為多個獨立的協處理器,在統一的時序節拍驅動下,各個協處理器盡可能地同步并發執行,將極大提升對應用功能的處理能力,各個模塊的功能復雜度也可以保持在較低水平。

3.1 多協處理器并行化方法的架構

圖4 中各個時間片代表的SVDU 各子功能,可以被聚合為以下具備一定獨立性的協處理功能:

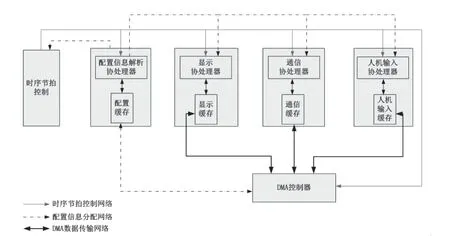

圖5 基于多協處理器并行化方法的SVDU技術方案Fig.5 The method of SVDU based on multi-processor

1)用戶配置信息解析協處理功能。

2)顯示協處理功能。

3)通信協處理功能。

4)人機輸入協處理功能。

為了保證各協處理功能有序地運行,需要配備專門的時序節拍控制模塊。在執行SVDU 系統功能時,各協處理功能間需要執行數據傳輸。因此,需要配備專門的DMA 控制模塊。

按照以下兩個原則可構建起如圖5 所示基于多協處理器并行化方法的SVDU 技術方案:

原則1 同步性

各協處理器有統一的時序基準以保證SVDU 行為的確定性。

原則2 并行性

本方法是一個去中心化的設計,除時序節拍控制外,其他協處理器地位等同。任意兩個或多個協處理器能夠配合實現SVDU 的應用功能。

圖5 中各協處理器的功能描述如下:

a)時序節拍控制模塊

本模塊為SVDU 運行提供時序基準,輸出的同步時序節拍定義了SVDU 的運行周期以及各個時間點應該執行的功能。通過本模塊來保證SVDU 功能的確定性。

b)配置信息解析協處理器

配置信息定義了SVDU 在不同的輸入條件下應當具備的狀態和輸出行為。本模塊在時序節拍的控制下,解析配置信息并將配置信息轉換為需要的操作后以并行的方式分發到指定的協處理器中。每個配置信息解析處理器需要配套一個配置緩存,用于暫存配置解析前后的相關信息。

c)顯示協處理器

顯示協處理器在時序節拍的驅動下,既要實現對顯示設備的驅動,又要按照特定的人機輸入、配置信息以及通信網絡變量實時地生成顯示畫面數據。每個顯示協處理器需要配套一個顯示緩存,用于實現顯示畫面信息的暫存。

d)通信協處理器

通信協處理器在時序節拍的驅動下,要完成多層安全通信協議的封裝、解析、接收以及發送控制,又要與應用數據、人機輸入數據配置信息關聯。每個通信協處理器需要配套一個通信緩存,用于實現通信接收或發送數據的暫存。

e)人機輸入協處理器

人機輸入協處理器在時序節拍的驅動下,既要完成對實體按鍵、觸摸屏等人機輸入設備的驅動控制和坐標數據捕獲,又要與配置信息關聯以識別其關聯的控件、通信網絡變量等。每個人機輸入協處理器需要配套一個人機輸入數據和應用數據緩存,用于人機輸入、應用數據關聯等信息的暫存,避免人機輸入信息的丟失。

f)DMA 控制器

以上各個協處理器中不存在中心節點,協處理器間存在數據傳輸的需求。DMA 控制器在時序節拍的控制下,按照配置信息的定義,實現協處理器間的數據傳輸控制。

3.2 多協處理器并行化方法的運行

基于單任務的SVDU 設備在執行“按鈕”類設備級手動控制功能時,需要順序地執行以下5 個動作:

1)捕獲人機輸入

定期掃描人機輸入設備,如果有人機輸入則開始準備人機響應,否則在下一個周期繼續掃描人機輸入設備。

2)人機響應關聯

在已捕獲到人機輸入的前提下,結合配置信息,確定應該執行的具體人機響應內容,如果配置信息未定義人機響應,則放棄人機響應操作,在下一個周期到來時繼續掃描人機輸入設備。

3)人機響應輸出控制

在人機響應關聯完畢的前提下,在顯示緩存的某一區域內產生人機回饋顯示數據,并將該信息輸出到顯示設備上,提示操作員SVDU 已經捕獲到人機輸入。

4)網絡變量關聯

通過配置信息的定義,識別該人機輸入是否關聯相應的網絡變量。如果關聯了網絡變量,則將對應的網絡變量設置為指定數值,否則放棄本次操作。

5)通信輸出

將網絡變量包通過安全通信發送至TU。

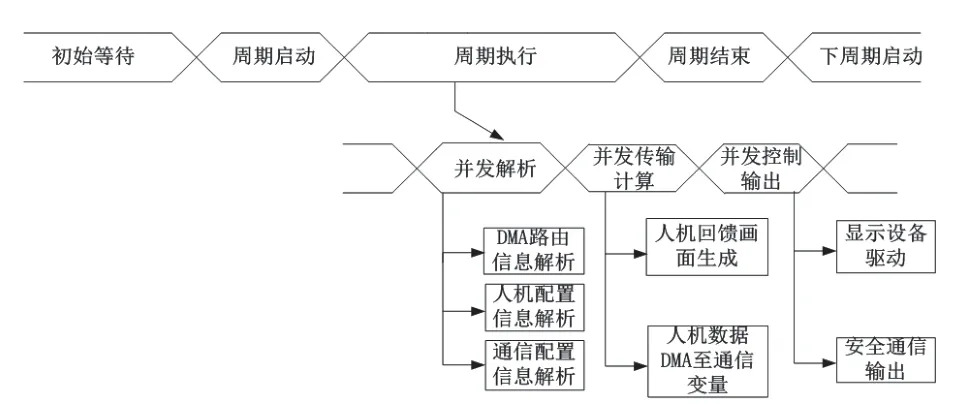

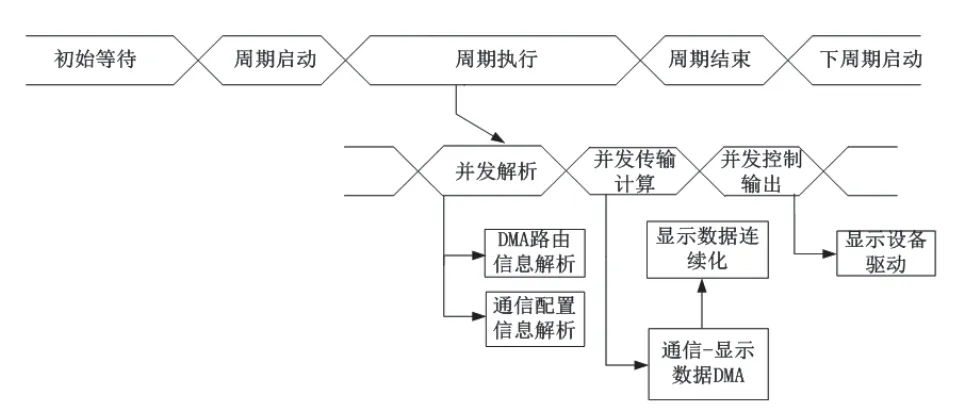

以上順序動作在多協處理器并行化方法下,將精簡為圖6 所示的時序。

圖6 設備級手動控制時序Fig.6 Device-level manual control timing

圖6 中,周期執行階段的具體操作如下:

a)并行配置信息解析

配置信息解析協處理器解析主體的配置數據,產生DMA 路由控制信息。顯示、通信、人機輸入協處理器解析自身所需要的配置信息。

b)并行數據處理與傳輸

顯示、通信、人機輸入協處理器通過DMA 獲取到自身所需數據,按照預定義的時序節拍結合各自解析的配置數據,并行地實現通信、人機、顯示數據計算。

c)并行數據輸出控制

在上一步的基礎上,各協處理器并行執行各自的功能。

在涉及復雜數據傳輸、數據運算的功能執行時,多協處理器并行化方法將體現出巨大的優勢。下面以事故后監測系統(Post Accident Monitor System,簡稱PAMS)變量趨勢顯示為例進行說明。其他復雜的狀態監視功能與此類似。

基于單任務的SVDU 設備進行PAMS 變量趨勢顯示時,通常需要順序地執行以下動作:

① 獲取通信數據。

② 通信數據與配置信息關聯,轉換為應用數據。

③ 應用數據通過插值算法連續化為顯示數據。

④ 顯示數據輸出至顯示設備。

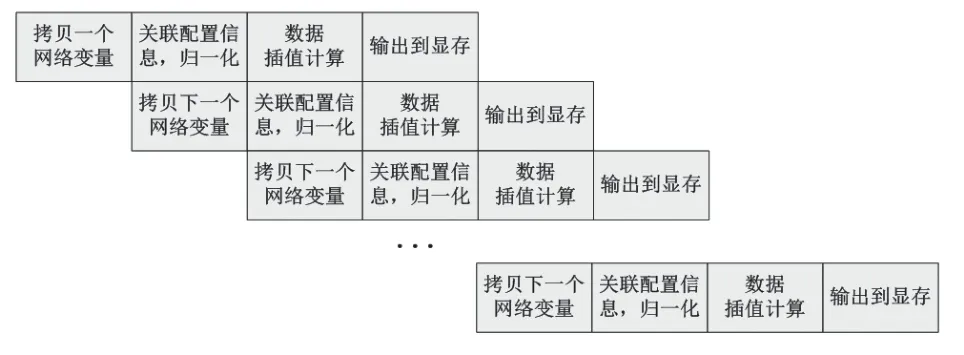

以上各個步驟順序執行過程中牽涉到大量的數據重復搬運工作,如圖7 所示。

采用多協處理器并行化方法,則PAMS 變量的趨勢顯示可按照圖8 所示的時序執行。

具體地,基于多協處理器并行化方法能夠使得PAMS變量的趨勢顯示實現四級流水線處理,如圖9 所示。數據吞吐率提升3 倍,在每個時序節拍可以完成一個PAMS 采樣點的數據搬運、數據歸一化處理、數據插值計算和輸出顯示。通過這種方法,一方面可以在單幅SVDU 畫面上顯示更多的PAMS 變量趨勢,另一方面更有利于某些復雜的數據插值和連續化算法的實施。

3.3 多協處理器并行化方法的技術實現

多協處理器并行化方法將SVDU 中的主要功能聚合為獨立的協處理器,主要有以下2 種實現方式:

圖7 順序化PAMS變量趨勢顯示流程Fig.7 Sequential trend display proc

1)基于多個通用微控制器元件的協處理器陣列

各個協處理器使用獨立的微控制器,通過板上總線連接,互相配合實現SVDU 的各項功能。這種實現方法存在以下問題:

◇ 元器件增多,可靠性預計指標下降。

◇ 板載通信接口、協議繁雜,限制整體性能提升。

◇ 某些特殊功能無法定制化,例如流水線處理、數據突發訪問等。

2)基于FPGA 的SOC

FPGA 的片上邏輯資源、布線資源以及RAM 資源越來越豐富。同時,隨著制程工藝的提升,FPGA 在執行相同邏輯功能的功耗與傳統的ASIC 器件已經相差不大。這些有利條件使得基于FPGA 的SOC 技術在面向小批量、柔性定制功能的應用中具有明顯優勢。通過SOC 的方式,不僅能克服通信接口的復雜,還能實現片上系統的集成[4]。

基于FPGA 的協處理器并行化方法具體實施方式如下:

◇ 利用FPGA 片上的邏輯資源、RAM 資源、布線資源來構建各協處理器。

◇ 利用FPGA 上的邏輯資源、布線資源來構建各協處理器間的片上并行通信總線。

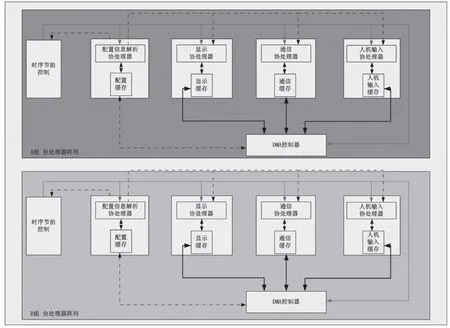

目前,多核處理器按照集成方式不同,可以分為同構多核處理器和異構多核處理器[5]。多協處理器并行化方法的實現需要結合同構和異構的特點。因此,在圖5 的基礎上,構造了雙冗余—混合型架構片上系統,如圖10 所示。

圖10 中,A 組協處理器陣列和B 組協處理器陣列采用完全相同的設計并執行相同的功能,可視為兩個同構的處理器核,用于滿足目前核電廠業主對SVDU 越來越高的可靠性要求。通過同構的冗余處理器核,使得即便在硅片上也實現了冗余功能,對于防范由于硅片部分區域損壞帶來的安全功能喪失具有重要意義。

圖8 PAMS趨勢顯示時序Fig.8 PAMS trend display timing

圖9 四級流水線PAMS變量趨勢顯示Fig.9 Four-level pipeline methods for trends display of PAMS variables

在A 組或B 組協處理陣列內,各協處理器可視為多個異構處理器核,執行不同的功能。通過異構的處理器核設計,能夠有效發揮各協處理器的專業功能,有效提升處理能力。此外,在A 組協處理器陣列和B 組協處理器陣列間還可以增加鎖步、互相監督等手段來提升可靠性。

3.4 多協處理器并行化方法的優劣

多協處理器并行化方法具有以下明顯優勢:

1)不明顯增加系統運行的功能復雜度

每個協處理器只執行特定的功能,其運行的復雜度小于單任務模式。在統一的時序節拍驅動下,所有時序流程均是清晰明確的,確定性高,有利于可靠性分析預測。

2)簡化測試驗證流程

多協處理器并行化方法將顯著減小軟件測試和驗證確認(Verification & Validation,簡稱V&V)的工作難度。各個協處理器間接口和時序關系明確,測試和V&V 可以按模塊逐個開展。

3)改善系統自診斷方法并提高安全性

多協處理器并行化方法可以使得精確和完善的自診斷監視方法的實施更為簡單和方便。這也使得SVDU 可以不再依賴特定的具有高安全完整性等級的CPU,有利于進一步提升SVDU 的自主可控能力。

當然,多協處理器并行化方法也有其不足之處:

圖10 雙冗余-混合型架構Fig.10 Dual redundant hybrid architecture

a)芯片資源需求增加

隨著半導體技術進步以及實際設備的低功耗、小型化、智能化的實際需求,多協處理器并行化方法必然是基于片上系統技術,即在單FPGA 或ASIC 上集成多個協處理器核和附屬的數據緩存,這又對目標芯片的布線資源、計算資源、存儲資源等提出了較高要求。

b)引入了額外的安全風險

節拍控制器定義了SVDU 所有行為的先后關系。準確可靠的節拍控制直接決定了SVDU 運行的正確性。節拍協調控制的引入可能帶來潛在的共因故障風險。

c)前期調試工作較為復雜

多協處理器并行化方法是針對特定的需求開發的非標準架構,在前期工作開展中,還需要增加調試工具設計,加重研發工作負荷。

4 結束語

本文通過梳理SVDU 的系統功能和當前設備底層支撐技術的局限性,提出了多協處理器并行化方法,并闡述了該方法的系統架構、運行機制以及技術實現的細節,同時分析了該方法的優劣性。多協處理器并行化方法具有并發執行高效率、功能驗證方便等突出優勢,對于未來SVDU產品的持續改進升級具有一定的啟發意義。