一種基于共用存儲空間的FPGA的QC-LDPC碼并行譯碼架構

陳章 安君帥 王本慶

摘 ? 要:針對QC-LDPC碼并行譯碼FPGA實現結構復雜、資源消耗大等不足,文章提出一種中間計算變量的共用FPGA存儲資源的QC-LDPC碼并行譯碼架構,此架構通過兩個交織單元,使得變量更新節點和校驗更新節點的結構使用同一個存儲資源,該架構具有控制簡單、效率高和存儲需求量低等優點,適用于高速衛星、地面等通信系統接收機中。

關鍵詞:準循環結構;低密度奇偶校驗譯碼;現場可編程邏輯門陣列;資源共享

準循環結構的低密度奇偶校驗碼(Quasi Cyclic-Low Density Parity Check Code,QC-LDPC)具有良好的編譯碼實現特性,被廣泛應用于地面移動5G標準、DVB-S2標準(IRA-LDPC)等國際通信標準中。采用QC-LDPC一方面可以提升編碼增益,另一方面編碼譯碼時可采用多路并行譯碼,提升系統的吞吐量。LDPC的通用譯碼算法是置信度傳播(Belief Propagation,BP)算法,是一種迭代的概率譯碼算法,硬件實現中一般采用最小和算法(Min-Sum Algorithm,MSA)進行近似。MSA包括變量節點更新和校驗節點更新兩個主要環節,在并行譯碼算法時兩個環節之間的中間計算結果需要進行二維交織和二級緩存[1-8]。本文基于QC-LDPC碼的準循環特點,在并行譯碼時的中間把數據存儲到共用存儲空間,更新時利用兩個交織器,只需要進行列間交織和列內循環移位即可實現二維交織,把二維運算簡化為兩個一維運算,極大節省了存儲空間。

1 ? ?QC-LDPC碼

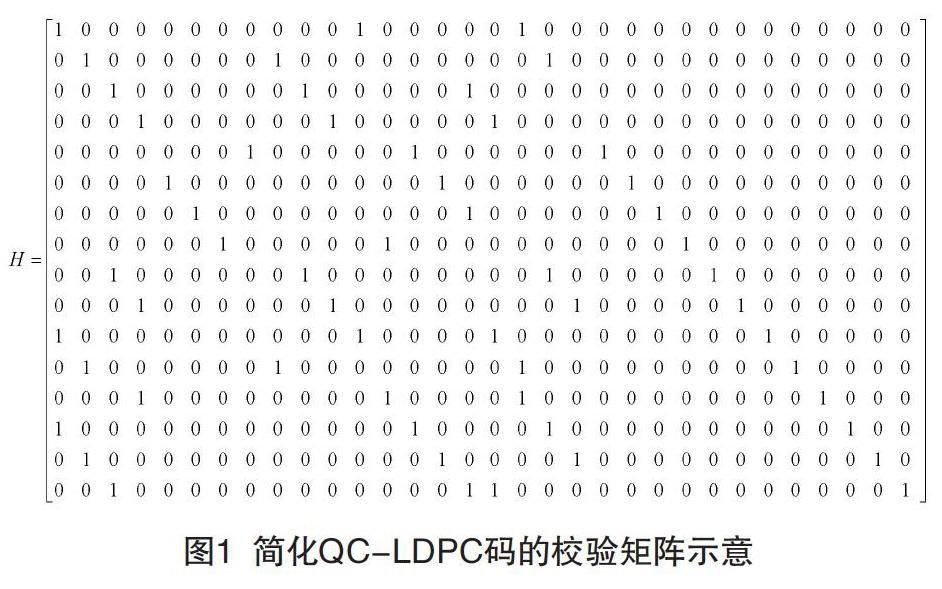

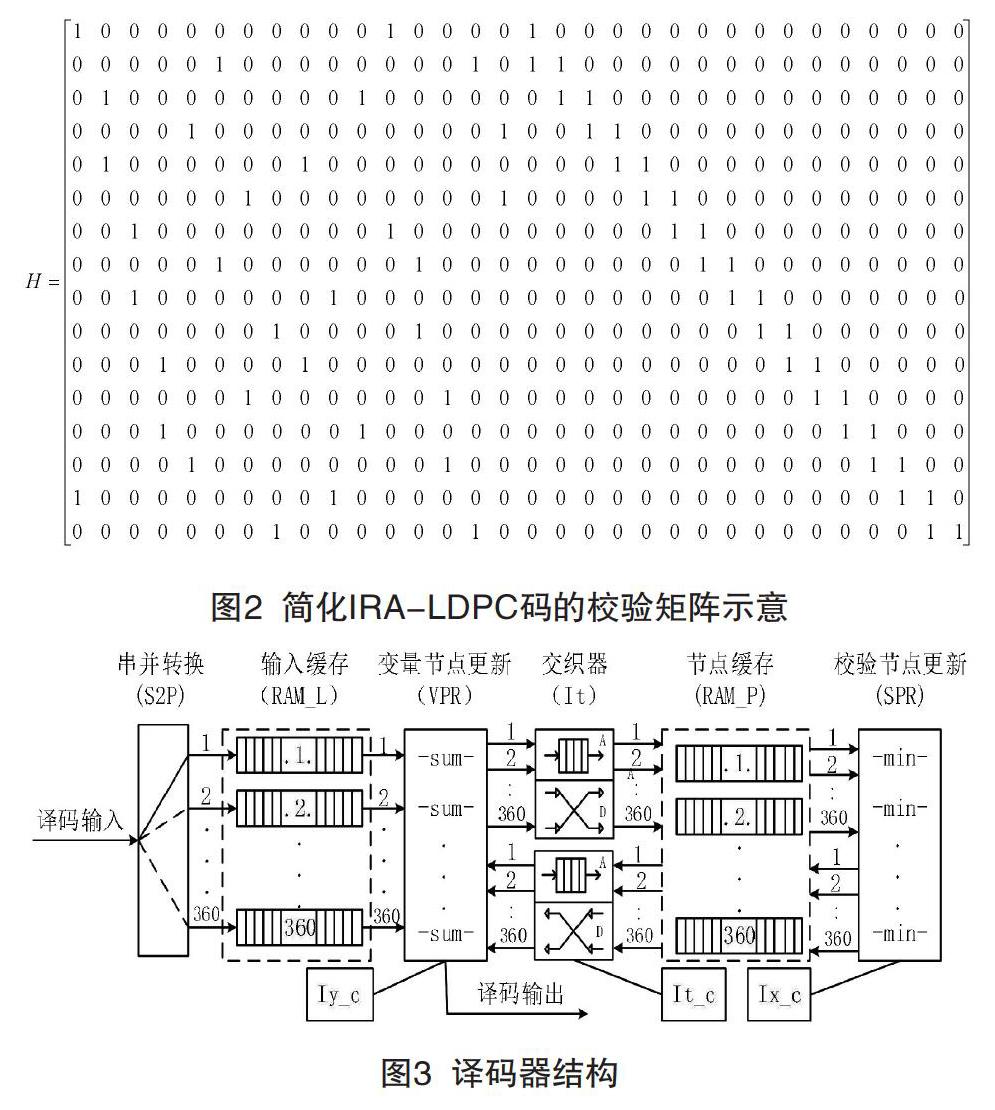

QC-LDPC碼是一類具有循環結構特性的LDPC碼,將LDPC碼的校驗矩陣劃分成多個子塊,每個子塊由全零矩陣或非零的、具有循環特性的置換矩陣構成。這種矩陣的特殊性使得QC-LDPC碼的編碼復雜度為線性,有利于硬件實現,而且碼字之間有較大的最小距離。QC-LDPC碼H矩陣的表現形式如圖1—2所示。

圖1為符合地面5G標準規則的QC-LDPC碼的簡化校驗矩陣示意,其中,k=16,n=32,進行4路并行譯碼,則Zc=4。

圖2為符合DVB-S2標準規則的非規則IRA-LDPC碼的簡化校驗矩陣示意,其中,k=16,n=32,進行4路并行譯碼,則Q=4。

2 ? ?譯碼器結構

本文設計的基于DVB-S2標準的IRA-LDPC碼并行譯碼現場可編程邏輯門陣列(Field Programmable Gate Array,FPGA)實現方法主要包括以下6個部分:串并轉換(Serial to Parallel,S2P)、輸入緩存(RAM_L)、變量節點更新(VPR)、交織器(It)、節點緩存(RAM_P)和校驗節點更新(SPR)。譯碼器結構如圖3所示。

(1)S2P,對串行譯碼輸入進行并行存儲控制,前面系統碼按順序分別并行存儲至360個輸入緩存(RAM_L)中,后面校驗碼按順序分別串行存儲至360個輸入緩存(RAM_L)中。

(2)輸入緩存(RAM_L),由360個獨立存儲器(RAM)組成,單輸入單輸出,存儲譯碼輸入(似然比),每個存儲器的存儲深度為碼長除以360。

(3)變量節點更新(VPR),由360個獨立變量節點更新(VPR)模塊組成,變量節點每次更新從相應輸入緩存(RAM_L)中讀取一個數據,從節點緩存(RAM_P)中按Iy_c控制字讀取多個數據,按變量節點更新(VPR)規則更新后,再按Iy_c控制字存儲至節點緩存(RAM_P)中。

(4)交織器(It),由正交織器(It1)和逆交織器(It2)組成,實現節點緩存(RAM_P)數據的存儲地址(列)間交織和360個數據的(列)內循環移位。正交織器(It1)實現節點緩存(RAM_P)數據按It_c控制字規則的列間交織和列內循環移位,并輸出至變量節點更新(VPR);逆交織器(It2)實現變量節點更新(VPR)后數據按It_c控制字逆規則的列內循環移位和列間交織,并輸出至節點緩存(RAM_P)。

(5)節點緩存(RAM_P),由360個獨立存儲器組成,雙輸入雙輸出,所有存儲器都同時按相同地址讀取或存儲數據,對應存儲360路校驗節點更新(SPR)之后的中間數據,存儲深度為校驗矩陣中每個按行塊的所有行重之和。

(6)校驗節點更新(SPR),由360個獨立校驗節點更新(SPR)模塊組成,校驗節點每次更新從節點緩存(RAM_P)中按Ix_c控制字讀取多個數據,按校驗節點更新(SPR)規則更新后,再按Ix_c控制字存儲至節點緩存(RAM_P)中。

(7)Ix_c,Iy_c和It_c控制字,Ix_c為校驗節點更新(SPR)控制字,是校驗矩陣每個按行塊中的每行行重的集合,Iy_c為變量節點更新(VPR)控制字,是校驗矩陣按列塊中的每塊首列列重的集合。It_c為交織器控制字,包括交織器對節點緩存(RAM_P)存取地址的列間交織控制字,和相應地址上讀取360路數據后的列內循環移位控制字。

3 ? ?譯碼流程

本文中譯碼器的譯碼流程主要由5個部分組成:初始化、譯碼輸入、變量節點更新、校驗節點更新和譯碼輸出。

(1)初始化,節點緩存(RAM_P)置零,校驗節點更新(SPR)載入Ix_c控制字、變量節點更新(VPR)載入Iy_c控制字和交織器(It)載入It_c控制字。

(2)譯碼輸入,檢測譯碼輸入使能有效時,計數器開始計數。前面系統碼時,計數器除以360取余作為360個輸入緩存(RAM_L)的片選信號,計數器除以360取整作為每個輸入緩存(RAM_L)地址信號。后面校驗碼時,計數器除以Q取余加系統碼存儲地址偏移后作為每個輸入緩存(RAM_L)地址信號,計數器除以Q取整作為360個輸入緩存(RAM_L)片選信號。整個碼字輸入結束后,開始譯碼,其中變量節點更新和校驗節點更新按順序都執行一次稱為一次譯碼迭代。對于高速連續譯碼,需要設計乒乓緩存結構進行譯碼輸入數據的緩存。