基于國產FPGA的千兆以太網交換機復位系統設計

王立瑩,左延智

(1.中國電子科技集團公司第五十四研究所,河北 石家莊 050081;2.北京跟蹤與通信技術研究所,北京 100094)

0 引言

經過多年的發展,我國數據通信設備制造業堅持技術引進和技術開發相結合,已經實現了網絡設備的整機國內設計和整機國內集成,并廣泛應用于各行業信息系統建設中[1]。但國內生產的網絡設備中,核心電子元器件主要采用國外產品,高端芯片等核心要素受制于人,網絡裝備總體自主化程度低[2]。電子元器件是數據通信設備的基礎,是保證數據通信設備可靠運行的基本單元[3]。電子元器件性能指標、質量與可靠性以及供貨保障能力直接關系到數據通信設備的性能、研制生產進程以及產品的售后保障能力等[4]。我國電子元器件產業受各種因素的影響,在元器件的門類、品種、性能和質量可靠性方面與國外產品相比都有較大差距,成為制約我國通信行業發展的瓶頸之一[5]。

核心元器件采用國外產品,關鍵技術受制于人,致使網絡設備在本質屬性上存在嚴重的安全隱患[6]。首先,在網絡空間對抗日趨激烈的背景下,西方國家有意愿有能力利用芯片內部可能存在的后門密碼、數據包監測和惡意攻擊等,操控網絡與信息系統、破壞關鍵業務數據、竊取核心機密信息及干擾網絡運行,甚至致癱設備和網絡,給國家和國防信息系統構成安全威脅;其次,各發達國家均把核心電子元器件作為影響國家安全的戰略資源加以控制,把限制核心電子元器件的出口作為一項基本國策[7]。例如美國政府制定嚴格的政策和相關措施限制高新技術及產品出口;美國商務部制定商品管制清單,規定符合相關性能指標的產品嚴禁出口到相關國家和地區[8]。西方國家還可通過對核心元器件、標準規范和核心技術專利的壟斷,形成對網絡與信息系統裝備供應鏈的安全威脅。尤其對于我國國防信息化裝備,有必要且急切需要實現交換設備的自主可控。

交換機國產化的關鍵是國產化核心電子元器件的應用,但也應清楚地認識到國產芯片的不足,與國外芯片相比,在性能、體積、功耗、集成度、可靠性、成本及配套軟件等方面都有一定的差距[9]。尤其是交換機內部集成電路的增多導致了交換機上電復位的復雜性,為了降低使用國產芯片對交換機功能、性能指標的影響,保證千兆以太網交換機的穩定運行,要充分考慮硬件性能、穩定性、可靠性及擴展性等因素,在設備上電啟動和運行過程中支持對部分芯片或模塊的復位[10],并提供不同的復位時序用以滿足交換機內部不同芯片的啟動順序及復位時間要求[11],提高整個系統的可靠性,以彌補國產器件的不足。因此,對以太網交換機復位系統的研究就非常有必要,本文從千兆以太網交換機的邏輯組成介紹出發,討論千兆以太網交換機復位系統的設計方法和設計過程。

1 交換機邏輯組成

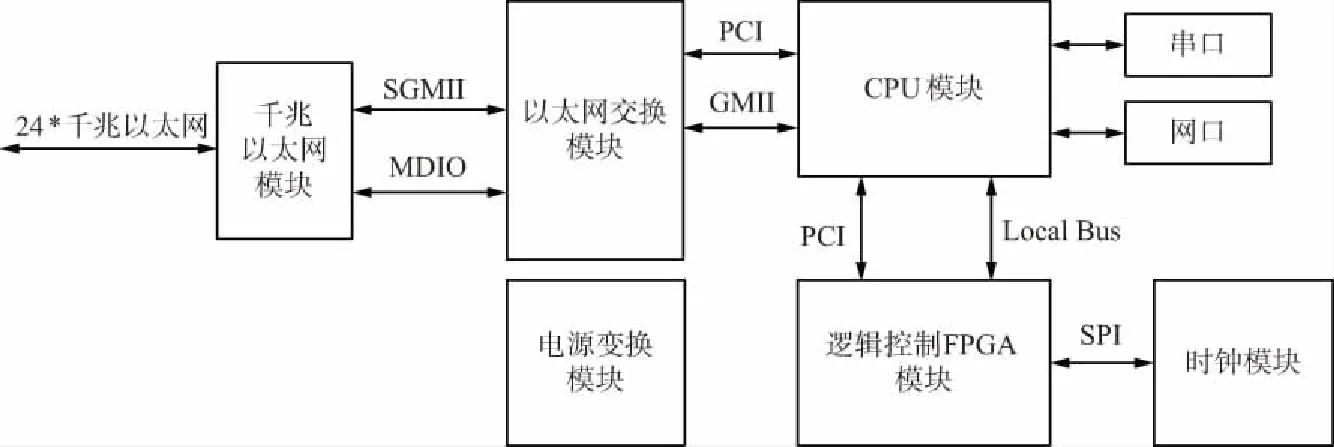

千兆以太網交換機主要由以太網交換模塊、CPU模塊、邏輯控制FPGA模塊、千兆以太網模塊及時鐘模塊等組成,如圖1所示。

圖1 以太網交換機邏輯組成Fig.1 Logic composition of ethernet switch

以太網交換模塊作為千兆以太網交換機的核心,主要完成業務數據路由交換功能,設計選用蘇州盛科公司的萬兆以太網交換芯片CTC6048,對外提供SGMII Serdes接口、數據通道接口、控制接口及管理接口等[12]。CPU模塊完成交換機的控制與協議處理,是各種路由協議運行的平臺,國產CPU芯片[13]采用中國科學院計算研究所的64位處理器芯片龍芯2F[14]。千兆以太網模塊實現千兆以太網線路接口,用于用戶業務接入。邏輯控制FPGA模塊主要實現各種可編程控制和業務處理邏輯,為設備提供復位控制、時鐘變換和寄存器維護管理等功能,選用上海傲格芯公司的AG10KF256[15]。時鐘模塊主要為相關功能單元提供時鐘參考,選用成都振芯科技公司的時鐘芯片。

2 硬件電路設計

在復位電路設計時,需要綜合考慮各芯片對復位的要求,如復位高低電平、復位順序及復位脈沖寬度等,且在設計中需實現以上形式組合多變的復合設計。通過合理選擇器件、邏輯設計,實現電路的需求。

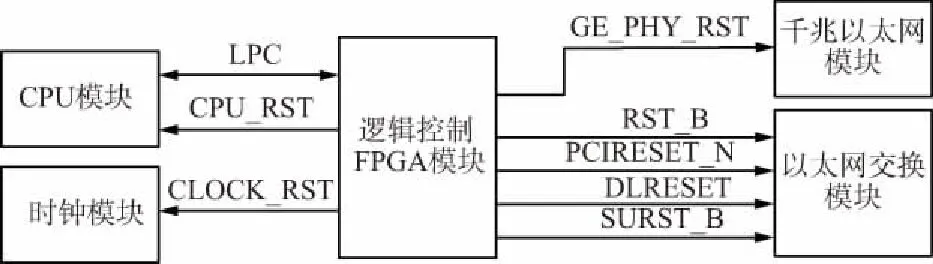

以太網交換機內需要復位信號的模塊包括CPU模塊、時鐘模塊、千兆以太網模塊及以太網交換模塊等,各模塊的復位邏輯主要由FPGA完成,具體復位電路邏輯如圖2所示。

圖2 復位電路邏輯框圖Fig.2 Logic block diagram of reset circuit

3 軟件設計

3.1 上電復位時序設計

以太網交換機中大多數芯片的復位都需要在供電和參考時鐘穩定后進行,在供電穩定后,首先要復位時鐘芯片,然后完成時鐘芯片的初始化配置,在時鐘芯片輸出時鐘穩定后,再復位其他芯片。

時鐘芯片支持多種復位方式,包括上電復位、異步RESET管腳復位和寄存器軟復位,本設計采用FPGA直接控制時鐘芯片的異步RESET管腳完成時鐘芯片的復位,根據時鐘芯片的異步復位時序要求,需要保證低電平脈沖≥50 ns。該復位信號采用“1-0-1”電平方式,先保持CLOCK_RST高電平10 ms,然后低電平脈沖10 ms,然后置高,完成一次時鐘芯片的復位操作。

在時鐘芯片復位后等待10 ms再開始時鐘芯片的配置過程,讓時鐘芯片復位生效,在時鐘芯片配置完成并輸出時鐘穩定后,再復位其他芯片,該過程主要取決于配置芯片時間和VCO的校準時間,配置芯片時間不大于5 ms,VCO的校準時間如下:

(1)

根據參考時鐘頻率、輸出時鐘頻率等因素,可獲得R取值1,cal_div取值2,fREFIN為25 MHz,根據式(1)計算VCO校準時間為0.352 ms。整個配置芯片時間加上VCO校準時間不大于10 ms,該過程取值10 ms。

千兆以太網芯片要求的復位時序為“0-1-0-1”電平方式,其中tW為在上電和時鐘穩定后NRESET可配置的時間,不小于2 ms;tREC為恢復時間,不大于105 ms;tW(RL)為低電平脈沖時間,不小于100 ms;tWAIT為NRESET置高后可以訪問SMI接口時間,不小于105 ms。參照復位時序要求,本設計中千兆以太網芯片的GE_PHY_RST復位信號先保持GE_PHY_RST低電平40 ms,然后置高電平150 ms,再低電平保持110 ms,然后置高,完成千兆以太網芯片的復位。

龍芯2F的復位時序要求在CPU_RST拉低之前,相關的時鐘信號、測試信號和初始化信號都必須有效,CPU_RST低電平脈沖要求至少一個時鐘周期。本設計中CPU_RST復位信號采用“1-0-1”電平方式,先保持CPU_RST高電平40 ms,然后低電平保持到以太網PHY芯片復位完成,保證CPU初始化程序運行前以太網PHY芯片的SMI接口工作正常,低電平時間取370 ms,然后置高。

CTC6048的復位信號主要包括全局復位信號RST_B、PCI接口復位信號PCIRESET_N、DDRDL復位信號DLRESET和CPU寄存器訪問接口復位信號SURST_B。本設計中RST_B、PCIRESET_N、SURST_B信號采用“1-0-1”電平方式,先保持高電平40 ms,然后低電平保持370 ms,然后置高,與CPU_RST一致。DLRESET信號采用“0-1-0”電平方式,先保持低電平40 ms,然后高電平保持370 ms,然后拉低。

3.2 FPGA設計

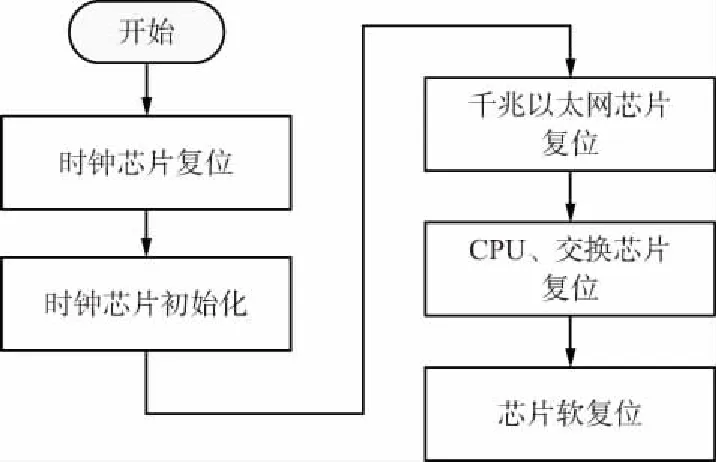

FPGA復位模塊信號主要包括CPU接口、SPI接口和復位信號等,復位模塊頂層原理如圖3所示。

圖3 復位模塊頂層原理Fig.3 Top level principle of reset module

FPGA程序主要包括時鐘分頻、計數器、時鐘芯片初始化配置及CPU軟復位寄存器等,完成時鐘芯片的初始化、各芯片的上電復位及軟件復位控制等功能。

FPGA通過SPI接口間接訪問配置時鐘芯片內部寄存器,時鐘芯片配置程序流程實際是全部寄存器配置的寫入流程組合,單個寄存器配置流程:① FPGA將要配置的寄存器地址寫入地址寄存器;② FPGA將要寫入寄存器的數據寫入寫數據寄存器;③ 開始寫操作;④ 將并行的地址、數據串行的寫入時鐘芯片SPI接口。通過時鐘芯片配置程序,完成需要配置的時鐘芯片寄存器的寫操作,實現時鐘芯片的整個配置流程。

上電復位程序參照上電復位時序,通過計數控制各芯片復位信號的高低電平。在設備上電初始化過程中或設備正常工作中,為了增加設備的可靠性,增加了部分芯片的自檢程序或狀態監控程序。當CPU判斷到特定接口或芯片發生故障,可以通過軟件控制FPGA完成相應芯片的復位。CPU與FPGA間互聯接口為Local Bus總線,CPU可以通過該接口訪問控制FPGA內相應的復位控制寄存器,完成復位。通過將各芯片的上電復位信號和相應軟復位信號進行“與”“或”組合,可以得到既保留上電復位時序又可以通過CPU控制的復位信號。復位程序流程如圖4所示。

圖4 復位程序流程Fig.4 Reset procedure flow

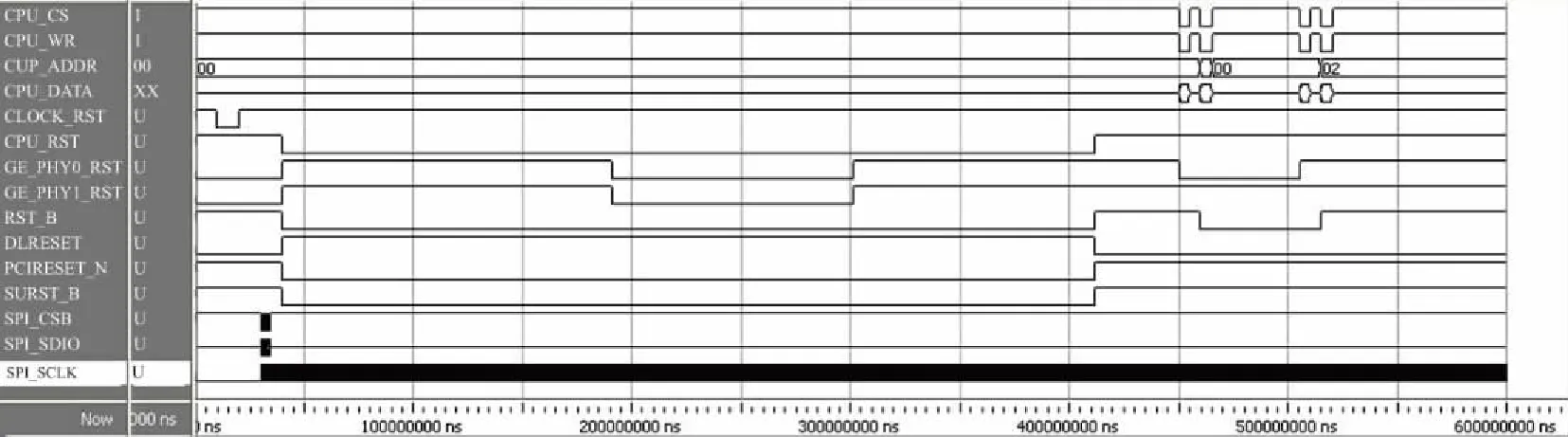

本設計采用上海傲格芯FPGA芯片AG10KF256,整個設計采用VHDL硬件描述語言來實現,在Quartus II 11.1開發軟件上完成設計、綜合及布局布線。通過上海傲格芯的開發軟件Supra完成工程轉換和編譯,并使用ModelSim進行時序仿真。交換機復位時序如圖5所示。在圖5中,先完成了時鐘芯片的復位,然后開始時鐘芯片的初始化配置。在時鐘芯片輸出時鐘穩定后,實現了CPU、交換芯片及千兆以太網芯片的上電復位過程。在CPU正常工作后,通過CPU接口訪問控制FPGA內復位控制寄存器,分別控制了GE_PHY0_RST和RST_B復位,實現了交換機內芯片的軟復位功能。

圖5 交換機復位時序仿真Fig.5 Simulation of switch reset sequence

4 結束語

本文從千兆以太網交換機的邏輯組成出發,研究了以太網交換機復位系統的實現原理,分析了軟硬件設計的實現過程,提出了以太網交換機的上電復位及軟件復位方案,并最終給出了一種適用于千兆以太網交換機的復位系統。通過FPGA實現交換機的復位,具有處理速度快、方便靈活和可擴展性好的特點。該設計滿足千兆以太網交換機的國產化需求,上電復位結合軟件復位方案可以推廣到其他交換設備中,能提高整個設備的可靠性,有著很好的應用效果。