國產復旦微SOC平臺AXI_DMA的應用研究

申偉 李浩 徐彬彬 劉秋生 李朝亮

摘? 要:國內SOC芯片日益崛起,而國產SOC平臺的應用尚未普及。ARM+FPGA架構中,CPU與FPGA通過AXI總線協議進行數據交流,小批量的數據可以通過AXI_lite進行交互,對于大容量的數據需要采用AXI_stream協議。本文進行了復旦微FMQL系列芯片AXI_DMA的應用研究與測試,并與賽靈思ZYNQ_7000系列進行了傳輸性能對比。

關鍵詞:SOC平臺? AXI_DMA? FPGA? LINUX

中圖分類號:TP368? ? ? ? ? ? ? ? ? ? ? ? ? ? ?文獻標識碼:A? ? ? ? ? ? ? ? ? ? 文章編號:1674-098X(2020)08(b)-0119-03

Abstract: Domestic SOC chips are rising day by day, but the application of domestic SOC platforms has not been popularized. In the ARM+FPGA architecture, the CPU and FPGA exchange data through the AXI bus protocol. Small batches of data can interact through AXI_lite. For large-capacity data, the AXI_stream protocol is required. In this paper, the application research and test of Fudan Micro FMQL series chip AXI_DMA is carried out, and the transmission performance is compared with Xilinx ZYNQ_7000 series.

Key Words: SOC; AXI_DMA; FPGA; LINUX

FMQL45_FFG900芯片為復旦微電子旗下的一款SOC芯片。該芯片采用PS+PL架構,四核APU,GP接口帶寬支持64位,且有更豐富的外設管腳。可應用于汽車輔助駕駛、無線通信、視頻、醫療、工業控制等。AXI_DMA是為內存與AXI4_Stream外設之間提供高帶寬的直接存儲訪問,可將CPU從數據搬移任務中解放出來,大大提高數據傳輸效率。

1? AXI接口互聯及握手機制

AXI協議提供單一的接口定義,能用在下述三種接口之間:master/interconnect、slave/interconnect、master/slave。在AXI總線使用過程中可以使用共享地址與數據總線,共享地址總線,多數據總線,multilayer多層,多地址總線,多數據總線。在大多數系統中,地址通道的帶寬要求沒有數據通道高,因此可以使用共享地址總線,多數據總線結構來對系統性能和互聯復雜度進行平衡。

AXI所采用的是一種READY,VALID握手通信機制,即主從模塊進行數據通信前,新根據操作對各所用到的數據、地址通道進行握手。主要操作包括傳輸發送者A等到傳輸接受者B的READY信號后,A將數據與VALID信號同時發送給B。

AXI總線還定義了在進出低功耗節電模式前后的握手協議。規定如何通知進入低功耗模式,何時關斷時鐘,何時開啟時鐘,如何退出低功耗模式。這使得所有IP core在進行功耗控制的設計時,有據可依,容易集成在統一的系統中。

2? AXI_DMA

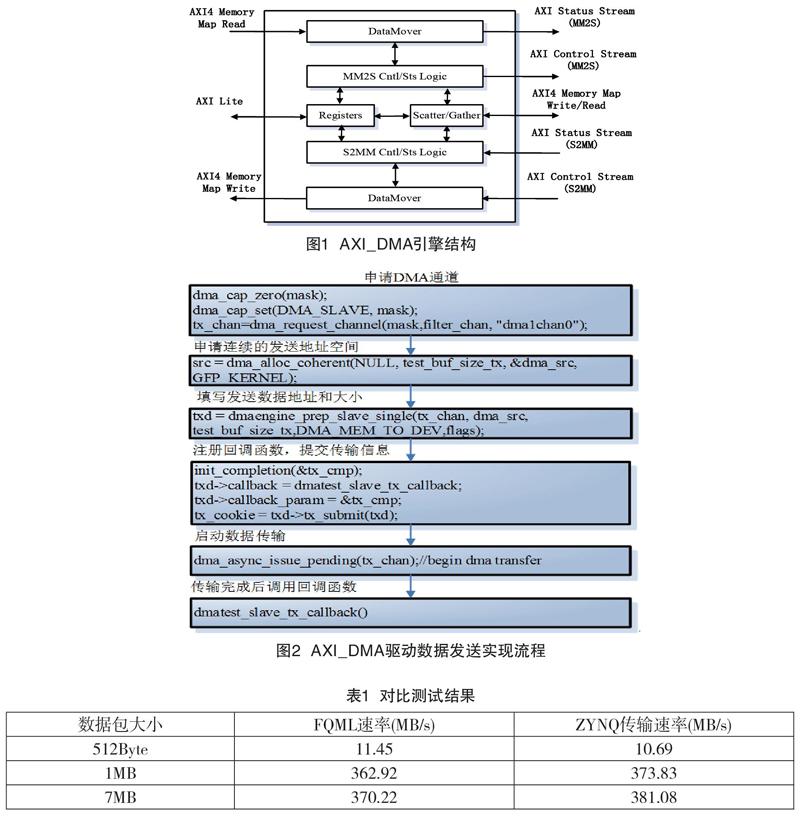

AXI_DMA主要包含四個模塊。AXI_DMA引擎結構如圖 1所示。

數據模塊用來實現存儲器接口和流接口的轉換;Scatter/Gather模塊用來實現設置DMA對非連續內存訪問的支持;狀態寄存器主要用來寄存DMA的工作狀態等信息,用戶可通過 AXI GP接口讀取這些狀態信息;配置寄存器模塊主要用來對AXI_DMA通過GP接口進行初始化的配置以使其能正常工作。

Direct Register Mode具備DMA的基本功能,給出源(目的)地址和傳輸長度之后就可以開啟一次傳輸。配置完一次寄存器之后只能完成存儲器連續地址空間的讀寫,在此模式下發送數據為MM2S_LENGTH寄存器所填寫的長度。

當發送數據大于收數據時會產生中斷,中斷處理函數中讀取狀態寄存器發現S2MM_DMASR[DMAIntErr]錯誤提示,此錯誤正好是填寫的收數據緩沖空間小于需要收的數據空間(自環下為發空間)。讀取內存數據查看實際已經傳輸了填寫的收數據空間的數據。當發送數據小于收數據時會產生中斷,讀取S2MM_LENGTH寄存器,收取數據為發送數據長度,收數據中斷由tlast信號觸發,表示收數據完成,軟件可以讀取S2MM_LENGTH寄存器查看真實收到的數據包大小。

3? FMQL AXI_DMA實現及測試

PL搭建與LINUX系統文件制作:選擇AXI_DMA IP CORE,搭建FPGA BD工程,短接收發通道,加入ILA監測信號。編譯生成BIT、HDF文件。通過FMQL開發環境PROCISE解析PL配置,生成設備樹源文件夾、FSBL工程,IAR編譯生成flsb.out用于第一階段啟動配置。由復旦微提供的BSP包編譯生成u-boot.、內核鏡像、設備樹、根文件系統。由PROCISE工具打包生成BOOT.bin。

AXI_DMA驅動軟件實現:數據發送模塊用來將數據從PS 搬遷到PL,數據接收模塊負責將PL數據搬遷到PS。收發數據在大體流程上基本一致,最大的差別在于通道的申請上,收發數據需要申請兩個相對獨立的DMA通道,填寫收發地址和回調函數注冊時也需要對應到相應通道上去。數據收發流程如圖2所示,接收部分與此類似。

PS控制AXI_DMA: PS采用內存映射的方式將外設的寄存器映射進PS的內存空間,可采用指針操作的方式對外設的寄存器進行訪問。

設備樹修改:FMQL設備樹關于DMA部分修改PS中斷號為25、26。

測試:PS應用測試程序下發不同大小的數據包,通過PL側自環,PS讀數據通道將AXI_DMA數據取回效驗。對比結果總結見表 1。

4? 結語

國產復旦微FMQL系列芯片PS與PL數據交互性能不亞于ZYNQ 7000系列,在時鐘頻率100MHZ和總線位寬為32位的情況下,實測PS與PL數據傳輸傳輸速率最高可達370MB/s左右。增加總線位寬、時鐘頻率、突發長度可以得到更高的傳輸速率。AXI_DMA傳輸速率隨著幀長增加而增加,適用于大包數據傳輸。

參考文獻

[1] 吳汶泰,詹璨銘.基于Zynq的AXI總線數據傳輸軟件優化[J].通信技術,2017,50(7):1576-1580.

[2] 楊海學,吳凡,李林,等.XCZU9的高速大容量數據采集存儲系統設計[J].單片機與嵌入式系統應用,2019,19(12):84-87.

[3] 莊瓊. 基于AXI總線的DMA高速通道及驅動的設計與實現[D].成都:電子科技大學,2019.

[4] 陳卓然,張宇.基于ARM+FPGA的心電信號疲勞駕駛檢測方法的研究[J].科技創新導報,2019,16(31):46,48.

[5] 曾俊,李雪江,楊勝.基于FPGA的集成式溫度采集裝置設計[J].科技創新導報,2019,16(35):49-50,52.

[6] 楊博,楚要欽,景德勝,等.基于AXI4總線的So C中離散量信號控制IP核的設計與驗證[J].信息通信,2020(3):90-92.