基于eFPGA 的通信基帶加速器的邏輯重構(gòu)設(shè)計

(中國電子科技集團(tuán)公司 第五十四研究所,石家莊 050000)

0 引言

隨著微電子技術(shù)進(jìn)入SoC(system on chip,片上系統(tǒng))時代,小型化成為集成電路的發(fā)展方向之一。由于特征尺寸的不斷縮小,NBTI(negative bias temperature instability,負(fù)偏壓溫度不穩(wěn)定性)效應(yīng)、HCI(Hot Carrier Injection,熱載流子注入)效應(yīng)引發(fā)的器件可靠性問題愈發(fā)凸顯。在航天應(yīng)用中,受空間輻射影響,星載電子設(shè)備中CMOS器件邏輯電平翻轉(zhuǎn)引發(fā)錯誤的現(xiàn)象時有發(fā)生。當(dāng)SoC芯片出現(xiàn)功能性故障或可靠性故障時,傳統(tǒng)的糾錯方法主要是通過模塊冗余(如三模冗余)方法實(shí)現(xiàn),存在資源開銷大、執(zhí)行效率低等缺陷。

SoC芯片集成度的不斷提高使得第三方IP核復(fù)用成為芯片設(shè)計的關(guān)鍵思路。eFPGA由于面積小、可移植性好,能夠以IP核的形式嵌入SoC芯片中,在改善信號延遲、提升計算性能方面具備優(yōu)勢。eFPGA的可編程性使得通過邏輯重構(gòu)實(shí)現(xiàn)故障電路的自愈功能成為可能。通信基帶加速器作為SoC芯片的關(guān)鍵部分,承擔(dān)著數(shù)字信號處理的功能,通常使用ASIC平臺實(shí)現(xiàn)。當(dāng)通信基帶加速器發(fā)生功能故障時,可以從FLASH中取出預(yù)先存儲的比特流信息,通過JTAG掃描鏈導(dǎo)入eFPGA進(jìn)行配置實(shí)現(xiàn)邏輯重構(gòu),同時斷開通信基帶加速器的互連總線,并配置eFPGA的互連關(guān)系,從而利用eFPGA執(zhí)行通信基帶加速器功能,實(shí)現(xiàn)電路故障自愈。對通信基帶加速器的邏輯重構(gòu),關(guān)鍵在于對其核心算法的實(shí)現(xiàn)和執(zhí)行。

1 eFPGA技術(shù)優(yōu)勢

FPGA(Field Programmable Gate Array,現(xiàn)場可編程門陣列)作為ASIC(application specific integrated circuit,專用集成電路)領(lǐng)域中的一種半定制電路出現(xiàn),其優(yōu)點(diǎn)在于其邏輯功能可由用戶通過軟件編程實(shí)現(xiàn)在線配置,并且可以反復(fù)擦寫。但隨著芯片不斷向小型化發(fā)展,傳統(tǒng) FPGA 使用中存在的缺點(diǎn)逐漸顯現(xiàn):在硬件加速應(yīng)用中,通常會浪費(fèi)很多可編程資源和外圍接口資源;標(biāo)準(zhǔn)FPGA與ASIC 之間的接口存在顯著的延遲,難以滿足高速計算的需求;功耗高、面積大、成本浪費(fèi)嚴(yán)重。eFPGA(embedded FPGA,嵌入式FPGA)則很好地克服了上述缺點(diǎn)。eFPGA是指可作為IP(intellectual property,知識產(chǎn)權(quán))模塊集成到SoC中的 FPGA(如圖1所示),可將 ASIC 設(shè)計的高性能和 FPGA模塊的靈活性有效結(jié)合起來,面積小、功耗低,可顯著降低資源開銷。

圖1 SoC集成eFPGA

eFPGA對比傳統(tǒng)FPGA具有諸多優(yōu)點(diǎn)。從連接方式上看,eFPGA通過內(nèi)部連線直接集成SoC,不需要大型可編程輸入/輸出緩沖,降低了接口延遲,提高了接口帶寬的性能(可實(shí)現(xiàn)10000個以上的I/O連接);從功能定制上看,靈活度更高,可根據(jù)應(yīng)用需求定義LUT(look-up table,查找表)、BRAM(block RAM,塊隨機(jī)存儲器)和cDSP(core DSP,數(shù)字信號處理器核)的數(shù)量,優(yōu)化資源配置。

eFPGA承擔(dān)數(shù)字信號處理功能,可顯著提升數(shù)據(jù)吞吐率。eFPGA省去了SERDES(高速串并轉(zhuǎn)換器)、PLL(鎖相環(huán))、硬核IP總線接口、GPIO(通用輸入/輸出)緩存等結(jié)構(gòu),通過精細(xì)時鐘門控(fine grain clock gating)降低了動態(tài)功耗,通過高密度互連節(jié)省了面積。

圖2為eFPGA的基本結(jié)構(gòu)。eFPGA基本單元為RBB(Reconfigurable Building Block,可重構(gòu)單元塊)。RBB按照功能可分為Logic RBB、DSP RBB、I/O RBB三類,分別執(zhí)行邏輯運(yùn)算、數(shù)字信號處理、輸入/輸出接口的功能。eFPGA經(jīng)過平面規(guī)劃后生成陣列結(jié)構(gòu),包含外圍I/O RBB、Logic核、DSP核、內(nèi)嵌BRAM。圖示eFPGA為2個Logic核、2個DSP核構(gòu)成的2x2結(jié)構(gòu)。其中DSP核由Logic RBB、DSP RBB、互連網(wǎng)絡(luò)及I/O RBB構(gòu)成。DSP RBB是由22位預(yù)加器、22x22位定點(diǎn)乘法器、48位累加器構(gòu)成的乘積累加器,可實(shí)現(xiàn)乘加運(yùn)算;Logic核不包含DSP RBB,由Logic RBB構(gòu)成,Logic RBB包含4個6輸入LUT及8個FF(Flip-Flop,觸發(fā)器),用以實(shí)現(xiàn)可編程邏輯;I/O RBB包含4個FF,支持觸發(fā)、直通模式,其中2個連接輸入端,2個連接輸出端。RBB資源與內(nèi)嵌BRAM、互連網(wǎng)絡(luò)、外部I/O接口共同構(gòu)成了eFPGA的基本結(jié)構(gòu)。

圖2 eFPGA結(jié)構(gòu)

eFPGA邏輯重構(gòu)流程如圖3所示。在系統(tǒng)設(shè)計階段對邏輯重構(gòu)目標(biāo)進(jìn)行系統(tǒng)評估,完成各個功能模塊的設(shè)計。使用RTL(Register Transfer Level,寄存器傳輸級)語言編寫HDL文件輸入綜合工具,綜合后生成門級網(wǎng)表,映射到eFPGA邏輯器件。編譯器分析映射后網(wǎng)表文件生成資源利用評估報告。平面規(guī)劃實(shí)現(xiàn)對基本邏輯單元、數(shù)字處理單元的資源選擇及分配,生成Logic核與DSP核的陣列結(jié)構(gòu),并在DSP外圍插入內(nèi)嵌BRAM。經(jīng)過布局布線完成內(nèi)部資源的連接,并生成時序報告。最后將布局布線后的網(wǎng)表文件編程配置,生成二進(jìn)制比特流,預(yù)先存儲到外部FLASH中。邏輯重構(gòu)時,比特流通過JTAG加載至eFPGA,完成配置后執(zhí)行目標(biāo)功能。

圖3 eFPGA邏輯重構(gòu)流程

2 基于JTAG測試模式的互連關(guān)系重構(gòu)

隨著SoC芯片集成度的提高,為改善傳統(tǒng)電路可靠性測試方法的不足,業(yè)界提出了電路可測試性設(shè)計(design for testability,DFT)。其中的JTAG(joint testaction group,聯(lián)合測試工作組協(xié)議)技術(shù)利用邊界掃描(Boundary scan)實(shí)現(xiàn)電路內(nèi)部的測試,并應(yīng)用于在系統(tǒng)內(nèi)可編程(In-System Programmable,ISP)技術(shù)中。

JTAG邊界掃描寄存器鏈由TAP(test access port)控制器控制。TAP是一個標(biāo)準(zhǔn)端口,有5個信號接口,分別為輸入接口:TCK(test clock,測試時鐘)、TRST(test reset,測試重置復(fù)位)、TMS(test mode select,測試模式選擇)、TDI(test data input,測試數(shù)據(jù)輸入)和輸出接口:TDO(test data output,測試數(shù)據(jù)輸出)。TCK驅(qū)動TAP 狀態(tài)機(jī)的運(yùn)行,TRST對TAP控制器進(jìn)行復(fù)位,TMS控制TAP狀態(tài)機(jī)的狀態(tài)轉(zhuǎn)換,TDI與TDO串行輸入和輸出測試數(shù)據(jù)。在正常工作模式下,邊界掃描寄存器鏈處于旁路狀態(tài),數(shù)據(jù)由Input輸入,從Output輸出;在測試模式下,邊界掃描寄存器鏈啟用,實(shí)現(xiàn)對eFPGA輸入輸出引腳及內(nèi)部邏輯信號的觀測,也可以加載比特流到eFPGA內(nèi)部電路,從而進(jìn)行邏輯功能重構(gòu)。通過TDI和TDO端口串行輸入和輸出測試數(shù)據(jù),可實(shí)現(xiàn)對eFPGA的調(diào)試(如圖4所示)。

圖4 帶有JTAG邊界掃描寄存器鏈的eFPGA

通信基帶加速器正常工作時,信號由外部存儲器經(jīng)DMA(direct memory access,直接存取)讀取送入總線,在總線上傳輸至通信基帶加速器,經(jīng)過處理后將計算結(jié)果返回總線,進(jìn)入下一級。數(shù)據(jù)通路為:外部存儲器—DMA—總線—通信基帶加速器—總線。當(dāng)系統(tǒng)檢測到通信基帶加速器某模塊發(fā)生功能故障時,信號傳輸至故障模塊前經(jīng)JTAG掃描鏈導(dǎo)入eFPGA,eFPGA實(shí)現(xiàn)故障模塊功能,在eFPGA中處理后,再返回通信基帶加速器進(jìn)行故障模塊之后的處理。此時的數(shù)據(jù)通路為:外部存儲器—DMA—總線—通信基帶加速器—JTAG掃描鏈—eFPGA—JTAG掃描鏈—通信基帶加速器—總線。具體實(shí)現(xiàn)方法如圖5所示。

圖5 eFPGA互連關(guān)系重構(gòu)

在通信基帶加速器外圍JTAG掃描鏈中接入故障監(jiān)測傳感器,當(dāng)故障發(fā)生時,傳感器將故障信息發(fā)送至CPU,由CPU向eFPGA發(fā)送信息,eFPGA在內(nèi)置FCU(FPGA configuration unit,F(xiàn)PGA配置單元)控制下進(jìn)入配置模式(configuration mode)。FCU選擇Flash模式直接從Flash中讀取預(yù)先存儲的比特流信息,導(dǎo)入eFPGA中,編程配置內(nèi)部邏輯。配置完成后,F(xiàn)CU將eFPGA轉(zhuǎn)換為用戶模式(user mode),執(zhí)行故障模塊的邏輯功能。信號在輸入通信基帶加速器故障模塊(如FFT算法模塊、FIR濾波模塊)前,在故障模塊的輸入端口被JTAG控制器讀取,越過故障模塊,經(jīng)由JTAG掃描鏈接入eFPGA輸入端口。數(shù)據(jù)在eFPGA中處理后由輸出端口輸出,經(jīng)JTAG掃描鏈傳輸回通信基帶加速器的下一功能模塊執(zhí)行后續(xù)的處理。借助JTAG掃描鏈屏蔽掉故障模塊重構(gòu)了互連關(guān)系,從而形成了新的完整數(shù)據(jù)通路。

3 通信基帶加速器典型算法設(shè)計

在通信基帶加速器中,OFDM(Orthogonal Frequency Division Multiplexing,正交頻分復(fù)用)技術(shù)由于能夠有效改善頻率選擇性衰落、提高頻譜利用率而得到了廣泛應(yīng)用。選取OFDM典型算法:FFT(Fast Fourier Transform,快速傅里葉變換)算法、FIR(Finite Impulse Response,有限脈沖響應(yīng))濾波算法進(jìn)行設(shè)計,用于eFPGA對通信基帶加速器邏輯重構(gòu)的仿真及驗(yàn)證。

OFDM基帶信號處理流程如圖6所示。比特流輸入后進(jìn)行前向糾錯編碼及交織以提升糾錯能力,在串并變換模塊中,串行高速數(shù)據(jù)轉(zhuǎn)換為低速并行數(shù)據(jù)以減小傳輸中出錯概率。每一路并行數(shù)據(jù)分配到各個子信道上(即映射到相互正交的窄帶子載波上),經(jīng)過IFFT(Inverse FFT,快速傅里葉逆變換)變換為時域的疊加信號,插入循環(huán)前綴后構(gòu)成實(shí)際發(fā)送信號。經(jīng)過處理的各路并行信號變換為串行信號,經(jīng)過數(shù)/模變換、低通濾波,上變頻后進(jìn)入信道中傳輸。在接收端執(zhí)行相反的流程。下變頻后進(jìn)行低通濾波、模/數(shù)變換、串/并變換,各路并行信號分別去除循環(huán)前綴后通過FFT模塊,實(shí)現(xiàn)各個子載波上的數(shù)據(jù)提取,進(jìn)而還原出每一路并行數(shù)據(jù)。經(jīng)過并/串變換、解交織、前向糾錯譯碼,最終輸出原始比特流。OFDM實(shí)現(xiàn)了多載波調(diào)制,將信道劃分為若干相互正交的窄帶子載波,將串行高速數(shù)據(jù)轉(zhuǎn)化為并行低速數(shù)據(jù)調(diào)制到子信道上傳輸,從而有效抑制符號間干擾(inter-symbol interference, ISI),提升抗多徑和抗衰落能力。

圖6 OFDM基帶信號處理流程

由信號處理流程分析可見,OFDM系統(tǒng)調(diào)制、解調(diào)并行數(shù)據(jù)的核心算法是IFFT與FFT:在發(fā)送端通過IFFT模塊用多路基帶數(shù)字信號調(diào)制子載波并疊加;在接收端通過FFT模塊實(shí)現(xiàn)子載波分離并解調(diào)。

DFT(discrete fourier transform,離散傅里葉變換)實(shí)現(xiàn)了數(shù)字信號由時域到頻域的變換,是基帶數(shù)字信號處理的常用方法。DFT將時域的周期離散信號變換為頻域的離散傅里葉級數(shù),將待分析的信號分解為相互正交的正弦波,以便提取信號的頻率及相位特征。DFT快速算法統(tǒng)稱FFT,顯著改善了DFT計算效率低的問題。對于N點(diǎn)序列的計算,傳統(tǒng)DFT算法需要N2次復(fù)乘、N(N-1)次復(fù)加,而FFT算法可將復(fù)乘及復(fù)加次數(shù)降低至約(N/2),有效提升了計算速度。

N點(diǎn)DFT定義為式(1):

m=0,1,…,N-1

(1)

基帶信號經(jīng)調(diào)制進(jìn)入信道傳輸?shù)倪^程中,信道時變現(xiàn)象調(diào)制子載波,會削弱子載波間的正交性,引入子載波間干擾(inter-carrier interference, ICI)。在基帶信號進(jìn)入信道之前使用低通濾波器濾除高頻分量,以抑制干擾。FIR濾波器的設(shè)計關(guān)鍵在于單位脈沖響應(yīng)h[k]的設(shè)計,使增益響應(yīng)滿足濾波指標(biāo)要求。FIR低通濾波器將輸入信號x[n]與h[k]卷積運(yùn)算得到輸出信號,高于截止頻率的高頻分量在卷積過程中被濾除,從而實(shí)現(xiàn)低通濾波。式(2)給出了FIR濾波算法的卷積公式,其中N為濾波器階數(shù)。

y[k]=x[k]*h[k]=h[k]*x[k]=

(2)

FIR低通濾波器在數(shù)字電路中由延遲線、加法器、乘法器組成的復(fù)合結(jié)構(gòu)實(shí)現(xiàn),每個乘法器對應(yīng)一個FIR系數(shù)h[k],即Tap(抽頭)權(quán)重。h[k]的個數(shù)k與濾波器階數(shù)N相等。圖7所示為40階FIR濾波器結(jié)構(gòu)。

圖7 40階FIR濾波器結(jié)構(gòu)

本文選取40Tap的FIR低通濾波算法進(jìn)行eFPGA仿真。設(shè)計偶對稱的系數(shù)序列作為單位脈沖響應(yīng)h[k],以實(shí)現(xiàn)低通濾波功能。使用Matlab繪圖,如圖8所示。

圖8 抽頭系數(shù)設(shè)計

4 仿真驗(yàn)證分析

使用28 nm工藝制程eFPGA評估板驗(yàn)證FFT算法與FIR算法。使用綜合工具將HDL文件綜合后生成EDIF文件,和IO定義文件、RAM定義文件、Floorplan文件輸入eFPGA編譯器進(jìn)行編譯,經(jīng)過網(wǎng)表映射得到資源利用報告。報告顯示了實(shí)現(xiàn)設(shè)計所需要的三類RBB基本單元(Logic、DSP、I/O)及查找表、觸發(fā)器的數(shù)量。根據(jù)資源需求計算邏輯核、DSP核的數(shù)量,進(jìn)而預(yù)測最小面積。

映射后網(wǎng)表經(jīng)平面規(guī)劃、布局布線后進(jìn)行靜態(tài)時序分析(Static Timing Analysis,STA)得出各時鐘域的時鐘扇出以及可實(shí)現(xiàn)的最高頻率、平均功耗。

根據(jù)布局布線后網(wǎng)表生成Bitstream(比特流),下載到eFPGA中完成配置。輸入激勵信號執(zhí)行邏輯功能。eLA(embedded Logic Analyzer,嵌入式邏輯分析儀)設(shè)計在eFPGA上運(yùn)行,實(shí)現(xiàn)對內(nèi)部信號的觀測及功能的調(diào)試。利用eLA讀取測試結(jié)果,生成波形文件。使用Gtkwave工具觀測波形。

4.1 FFT仿真驗(yàn)證分析

對不同頻率的連續(xù)正弦波疊加后采樣,得到離散數(shù)據(jù),作為激勵輸入。設(shè)定加權(quán)系數(shù)為0.25、0.25、0.75,對頻率為1.5625 MHz、6.25 MHz、25 MHz的cos函數(shù)、sin函數(shù)分別疊加得到兩路連續(xù)信號,再以200 MHz的采樣頻率分別采樣得到兩路離散信號,作為實(shí)部、虛部兩路正交信號激勵。使用Matlab仿真256點(diǎn)FFT,得到頻譜圖,如圖9所示。

圖9 FFT算法Matlab仿真結(jié)果

圖中縱坐標(biāo)與信號幅值成正比例關(guān)系,橫坐標(biāo)為點(diǎn)數(shù),每一個點(diǎn)對應(yīng)一個頻率。由于采用256點(diǎn)FFT算法,采樣頻率設(shè)定為200 MHz,故第256點(diǎn)對應(yīng)200 MHz頻率。以此類推,第k個點(diǎn)對應(yīng)頻率為(k-1)*(200/256)MHz。由FFT理論可知,復(fù)信號實(shí)部FFT實(shí)部圖像偶對稱,復(fù)信號虛部FFT實(shí)部圖像奇對稱,復(fù)信號FFT實(shí)部圖像是兩個圖像的疊加結(jié)果,負(fù)頻率抵消,正頻率加倍。由復(fù)信號FFT實(shí)部頻譜圖可知,在第2點(diǎn)、第8點(diǎn)、第32點(diǎn)處出現(xiàn)明顯峰值,且比例為1:1:3,對應(yīng)頻率1.562 5 MHz、6.25 MHz、25 MHz。

Bitstream下載至eFPGA評估板完成配置,輸入激勵后生成波形文件。在Gtkwave中觀測驗(yàn)證結(jié)果。從圖10中可以看出,指定RDY為eLA_TRIGGER,在20 ns處RDY拉低后開始執(zhí)行FFT算法。截取20 ns后1024 ns波形為一個周期,觀測到FFT實(shí)部輸出信號DOR在第8 ns、第32 ns、第128 ns處出現(xiàn)明顯峰值,幅度比為1:1:3,分別對應(yīng)1.562 5 MHz、6.25 MHz、25 MHz頻率。驗(yàn)證結(jié)果與Matlab仿真結(jié)果對比,頻譜基本一致。

圖10 FFT算法eFPGA評估板驗(yàn)證結(jié)果

使用eFPGA編譯器進(jìn)行資源利用評估,評估結(jié)果如表1所示。

表1 FFT算法eFPGA資源利用與性能評估

由表1可見,此FFT算法仿真可實(shí)現(xiàn)177.78 MHz的工作頻率。eFPGA功耗為82.67 mW,面積為6.4 mm2,面積及功耗較為理想,可以滿足SoC集成的要求。

4.2 FIR仿真驗(yàn)證分析

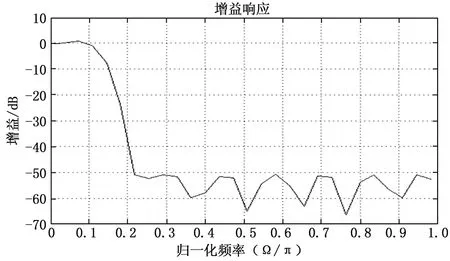

設(shè)定采樣頻率為200 MHz,截止頻率為20 Mhz。設(shè)計Tap個數(shù)為40的低通濾波器。使用Matlab計算得到圖11中的增益響應(yīng)。

圖11 FIR濾波器增益響應(yīng)MATLAB仿真結(jié)果

圖中橫坐標(biāo)為歸一化頻率,數(shù)值1處與200 MHz頻率對應(yīng)。在0~0.1之間(對應(yīng)0~20 MHz頻段)增益響應(yīng)為0 dB,0.1(20 MHz頻率)后快速衰減,在0.2(40 MHz)后降至-40 dB。此FIR濾波器模型可濾除高于20 MHz頻率的信號分量。

將編譯后得到的Bitstream加載到eFPGA評估板完成配置,將頻率為31.25 MHz、7.8125 MHz的兩路正弦波疊加后采樣,得到輸入信號DI,作為激勵輸入eFPGA。計算后輸出波形文件,顯示輸出信號DO近似為7.8125 MHz正弦波。

圖12 FIR算法eFPGA評估板驗(yàn)證結(jié)果

使用eFPGA編譯器進(jìn)行資源利用評估,評估結(jié)果如表2所示。

表2 FIR濾波器eFPGA資源利用與性能評估

由表2可見,此FIR濾波器仿真可實(shí)現(xiàn)211.73 MHz的工作頻率。eFPGA功耗為115.17 mW,面積為4.8 mm2,面積及功耗較為理想,可以滿足SoC集成的要求。

5 結(jié)束語

本文提出了一種基于eFPGA的邏輯重構(gòu)方案,用于通信基帶加速器發(fā)生故障時實(shí)現(xiàn)功能自愈。通過JTAG掃描鏈重構(gòu)互連關(guān)系,將eFPGA接入數(shù)據(jù)通路,利用eFPGA重構(gòu)故障模塊的邏輯,進(jìn)而代替通信基帶加速器執(zhí)行特定功能實(shí)現(xiàn)自愈。使用eFPGA編譯器進(jìn)行典型算法仿真,并在eFPGA評估板上完成驗(yàn)證,結(jié)果顯示eFPGA有比較理想的面積與功耗,預(yù)期的設(shè)計功能可以實(shí)現(xiàn)。此方案克服了傳統(tǒng)自愈方案資源開銷大、執(zhí)行效率低的缺陷,可有效提高系統(tǒng)可靠性與靈活性,為電路自愈技術(shù)提供了參考思路。