WiFi芯片的高速SDIO接口設計與驗證

劉衡祁

摘? ?要:近年來,隨著互聯網技術的發展,WiFi技術具有較強的穩定性,而且具備數據傳輸速度快、功能消耗較低等優點,目前在無線通信中已經具有十分重要的作用。隨著時代發展進步,對WiFi芯片的要求越來越高,對研發者來說,快速高效拓展WiFi芯片外部功能是當前面臨的主要問題。文章提出外部拓展接口,即SDIO接口,可在WiFi芯片架構中集成,能夠為該芯片提供快速信息傳輸接口,闡述了該芯片總體架構,分析了SDIO Host仿真模型搭建仿真平臺,能夠完成相應的仿真驗證,最后通過芯片測試表明該SDIO接口不同的子功能,設計合理,具有較強的可操作性。

關鍵詞:WiFi芯片;高速;安全數字輸入輸出卡;接口;設計;驗證

近年來,隨著深亞微米技術的發展,集成電路芯片的功能越來越豐富,芯片是IC的重要核心原件,一個系統芯片可集成多種功能模塊,包括CPU儲存器、模擬單元等,該技術可將原有多芯片實現的功能集成到同一芯片,提高系統集成度、降低研發成本、提高芯片應用性。在當前電子產品逐漸推陳出新的過程中,為滿足人們對產品的需求,市場傾向于接口豐富且拓展功能性強的芯片,在芯片中集成多種可通用接口,不僅可快速突破功能要求和成本,同時也能為芯片升級、功能拓展提供幫助。目前傳輸接口存在多種樣式,本研究主要以安全數字輸入輸出卡(Secure Digital Input and Output,SDIO)接口作為WiFi信息高效傳輸接口進行闡述。

1? ? WiFi芯片

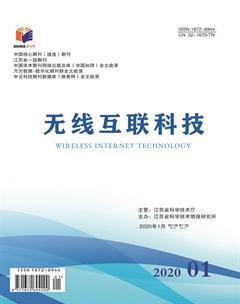

WiFi芯片架構是目前無線領域傳輸速度較快的產品,筆者研究的WiFi芯片是基于802.11n標準協議,可實現320 Mbps的傳輸速度,在芯片架構上選擇AMBA總線架構,具體結構如圖1所示。

該總線是一種多層總線結構,可定義多種功能總線,其中,系統總線(Advanced High performance Bus,AHB)可解決高性能的設計需求。AHB是外圍總線,實現高帶寬總線,為低帶寬設備間提供信息橋梁,具有結構簡單、功能消耗低等特點。該芯片采用一層外圍總線(Advanced Peripheral Bus,APB)和雙層AHB共同構成芯片相互連接的系統,其中AHB總線能夠提供高帶寬接口并完成大量數據傳輸。在AHB總線互聯上,該系統包含多個master同時在AHB總線中,master數量不能高于16個。master傳輸時可提供HADDR和HWRITE,控制信息系統中包含多個slave,可實現master發出的傳輸信號響應,并將結果返回給master,系統需要包含Arbiter,同時多個master申請占用總線時,通過特殊機制允許優先最高master獲得總線占有權。此外,每個AHB互聯的系統都包含一個dcoder對傳輸結果進行編碼,同時根據編碼結果生成slave所需要的信號。在AHB總線傳輸過程中,傳輸前AHB master需要向Arbiter發出信號請求,如果MACR被允許占用總線后才能夠開始信號傳輸,整個過程包括一個addiss phase和多個data phase。前者持續一個時鐘周期,所有slave需要在該時間段內進行信號采集,如果在這一時間段內沒有采集到有效信息,將會使傳輸信號失敗,而后者包含多個時鐘周期,通過拉低信號可插入等待周期,進一步延長數據采集周期,為設備獲得充足的數據采集時間。

2? ? SDIO總線協議

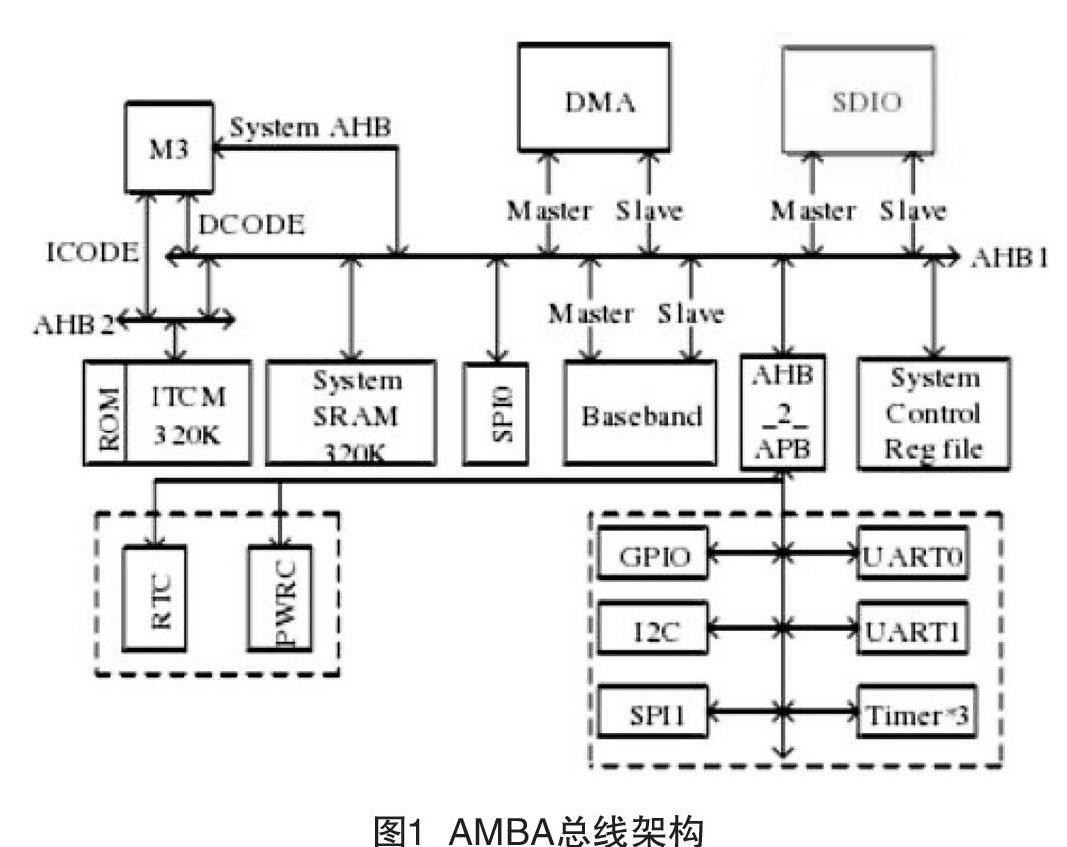

芯片SDIO接口是基于SD總線協議逐漸發展而來的,這兩種主線在兼容性上主要體現于軟件、機械信號等多個方面,除能夠與SD總線時間兼容之外,SDIO接口還具有獨特性。首先,較強的可拓展性,可支持多個I/O功能模塊,可面向移動和固定設備運用;其次,SDIO接口能夠像SDIO Host返回信號中斷;最后,其工作過程中電壓較低,信息傳輸速度快,能夠為移動設備提供高效傳輸且功率消耗低的I/O接口,從類型上可將SDIO卡分為高速卡、低速卡兩種,高速卡可實現SPI,SDI和SD4這3種模式運行,最高信息傳輸速率可達到200 Mbps;低速卡可實現SPI和SDI兩種模式運行,傳輸速度相對較低,傳輸速率僅為400 kbps。在處于不同運行模式下,各管腳功能存在差異。從其傳輸持續上來看,總線通信是通過命令響應數據傳輸進一步實現的總線設備,可通過相互兼容的方式使技術標準傳輸時序實現,在傳輸時期中,SD總線包含兩種基本傳輸,即寫數據傳輸和讀數據傳輸。在基本函數中,整個過程包含的命令響應通信具體傳輸時序如圖2所示。

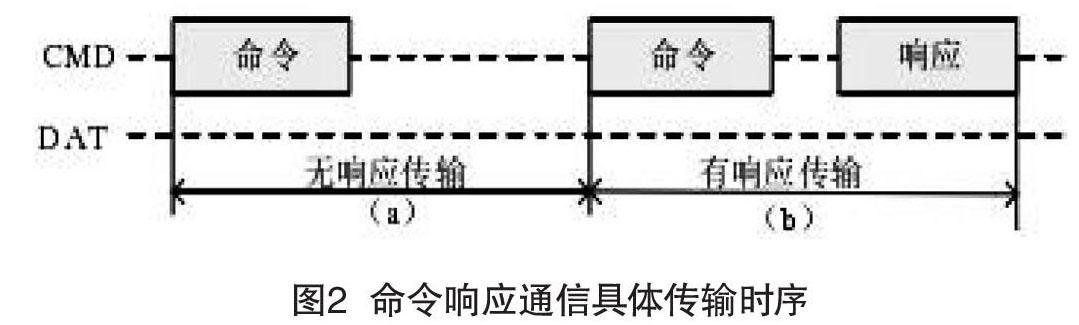

在該圖中,基本傳輸過程包含無響應和有響應兩種傳輸操作,整個傳輸時可借助CMD線實現,不需要通過數據總線DAT參與信息傳輸過程,在寫數據傳輸過程中,該過程包含命令響應數據通信,數據的傳輸是由SDIO HOST向SDI卡進行傳輸,具體傳輸實際圖如圖3所示。

在該數據傳輸中,寫數據傳輸共包含單數據和多數據塊字節傳輸兩種方式,完成每單位數據傳輸后,SDIO卡需要對通訊數據進行校驗,結果會自動返回至SDIO HOST中。在讀數據傳輸中,整個過程包含命令響應數據通訊,其傳輸方式為由SDIO卡發至SDIO HOST中,具體的傳輸時序如圖4所示。

根據圖4可知,讀數據傳輸是與寫數據傳輸方式基本一致,每單位數據傳輸完成后,需要由SDIO HOST對通信數據進行校驗,并將結果決定是否保留接收數據作為最終的有效數據。

3? ? SDIO接口設計和實現

基于上述設計需求特點,研究SDIO接口硬件結構設計,如圖5所示。

在該模塊中,SDIO接口結合不同的功能需求由命令解析、循環冗余、校驗生成、SD接口、AHB接口、數據控制等多個功能構成,SD接口和AHB接口是總線接口,在不同時鐘域下兩個接口工作,對設計SDIO接口來說是異步的,異步處理模塊對兩者信息通信實現一步操作,比如命令解析模塊,該模塊主要實現采樣CMD線命令,正確進行命令參數信息體系可將對應參數轉為有效信號,進而能夠顯示SDIO接口操作,在本設計中可以使用有限狀態機(Finite State Machine,FSM)實現命令的接收功能,具體狀態機實現如圖6所示。

在響應產生模塊設計過程中,可根據其他模塊返回的信息正確向主設備返回卡的操作環境,檢驗結果卡狀態信息具體功能,實現狀態機如圖7所示。

通過圖7可發現,響應產生狀態期主要包含空閑、SD模式、等待、有效數據響應位、響應CRC等工作狀態。當硬件上軟件復位后,狀態機則處于SIDLE狀態中。在數據控制模塊中,當SDIO HOST發起數據傳輸命令之后,能夠對相應數據進行緩存、轉換以及多路選擇等操作,確保數據在傳輸過程中不會丟失,并能夠嚴格按照協議進行持續傳輸[1]。數據控制模塊可實現讀寫操作的一系列流程,為降低模塊設計復雜性,需要合理進行數據控制,將模塊功能分割為多個子模塊,實現所有功能,數據控制模塊的結構如圖8所示。

圖8中,方框部分為數據控制模塊,該模塊被劃分為字節計數、數據接收、發送、選擇這4個功能模塊,右側讀寫模塊是對傳輸數據實現同步操作。

AHB接口模塊,能夠高效處理SDIO接口傳輸的信息,同時將SDIO接口集成到芯片架構中,整個接口模塊,主要由AHB從設備和主設備兩種功能模塊構成。在同設備中,整個設計可實現SDIO接口與CPU的交互,通過CPU對SDIO接口寄存器完成讀寫,同時SDIO接口可將讀寫過程中斷并返回至相應的CPU,并且使CPU實時監控SDIO接口的數據傳輸情況。在芯片設計架構中,SDIO接口的機制為0x4000xxxx.,在SDIO接口實現數據傳輸時,需要CPU對功能寄存器完成正確配置,同時實時檢查狀態寄存器的運行情況,確保數據可實現正常傳輸。對于AHB主設備來說,該模塊可實現SDIO接口數據協議轉換并完成標準SD總線形式數據和標準AHB總線數據之間的轉換,當利用SDIO HOST進行大量數據傳輸時,采用傳統的輸入指令或者中斷方式來有效控制信息傳輸過程,最終會使CPU被長時間占用,導致部分數據丟失。采用DAM的傳輸方式可以減少CPU所占用的時間,進一步提高信息處理能力,在AHB總線中進行SDIO集成設計可以使用AHB主設備傳輸方式,進而實現DMA信號傳輸。SD總線在傳輸速度上有一定限制,為確保數據能夠快速傳輸,該模塊需要支持的Burst,類型可以在標準協議傳輸中進行篩選[2]。

4? ? 仿真與驗證分析

在整個驗證中,功能仿真式的主要內容是分析所設計的RTL邏輯性,確保RTL可滿足相應的應用需求。功能仿真無需考慮時序問題,且仿真速度快,可通過所輸出的文件波形快速進行結果分析,為全面檢測SDIO接口功能和搭建下列測試平臺。完成測試平臺中不同功能模塊設計后,應按照相應流程進行仿真測試,在具體方針中要求仿真具有高效性,能夠在短時間內進行錯誤糾正。同時還需要具備一定完備性,在設計中存在錯誤要求仿真可達到功能覆蓋率。通過測試,發現所設計的SDIO接口各功能可實現正常運行,且處于SD4運行模式下能夠支持的最高時鐘頻率可達到70 MHz,最穩定的數據傳輸效率最大可達到280 Mbps。

5? ? 結語

本文主要分析了WiFi芯片架構,對系統總線AHB協議進行分析,闡述AHB在Burst傳輸過程的具體情況,為后續SDIO接口實現數據批量傳輸奠定基礎。闡述了SDIO總線接口特點功能,根據協議需求設計相應的SDIO接口結構,在WiFi芯片上集成SDIO接口并能夠完成相應的測試,最終表明SDIO接口在WiFi芯片上可實現正常運行,最快傳輸率可達到280 Mbps。

[參考文獻]

[1]劉雨沁,郭元興,劉繼平.基于FPGA的SDIO通信接口的設計實現[J].通信技術,2017(11):248-252.

[2]邰雪鳳.基于WiFi的振動信號采集儀的研究與實現[D].天津:天津工業大學,2017.

Abstract:In recent years, with the development of internet technology, WiFi technology has strong stability, fast data transmission speed, low function consumption, etc. The advantages have already played a very important role in wireless communication. With the development of the times, advancements of WiFi chips are increasingly demanding. At present, it is a major problem for developers to quickly and efficiently expand the external functions of WiFi chips. In this paper, an external expansion interface, namely the SDIO interface, can be integrated in the WiFi chip architecture, which can provide a fast information transmission interface for the chip. This study describes the overall architecture of the chip, analyzes the SDIO HOST simulation model to build a simulation platform, and can complete the corresponding simulation verification. Finally, the chip test shows that the SDIO interface has different subfunctions, is reasonable in design, and has strong operability.

Key words:WiFi chip; high speed; secure digital input and output; interface; design; verification