一種基于FPGA的二維DBF實現方法

陳 亮 劉國浩 袁子喬 崔向陽 田 歡

(1.西安電子工程研究所 西安 710100;2.陸軍裝備部駐西安地區軍事代表局 西安 710032)

0 引言

本文提出的DBF架構主體內容包括兩部分,第一部分是將多路A/D數據寫入雙口RAM,根據DBF模塊工作時鐘和A/D數據有效速率的N(N為正整數)倍關系,將每個采樣點的A/D數據從雙口RAM中讀取N次,以保證RAM讀寫等速率。速率轉換的過程[1],將每個采樣點的A/D數據讀取次數參數化,可兼容雷達系統的不同采樣頻率;第二部分是基于DSP48構建復數乘法單元,利用DSP48的PCIN/PCOUT端口,對多路A/D間的復乘結果級聯累加[2],由于級聯端口之間有專用的布線資源,從而保證DBF模塊達到更高時鐘頻率,或者同等資源利用率的情況下,FPGA更容易達到時序收斂。本文所述的陣元間直接加權的DBF方法,雖然比降維DBF方法占用更多DSP48資源,但增加了雷達系統波束形成的靈活性和不同采樣頻率的兼容性。DBF模塊設計充分利用DSP48內部加法器、級聯管腳和專用的布線資源,相比于直接使用復乘和累加IP Core,節約資源的同時更加易于時序收斂。

1 A/D數據速率轉換

1.1 系統速率分析

假設FPGA收到的M路并行的A/D數據,其中每路有N個通道的串行數據,即單個采樣點的數據量K=M×N,單個采樣點的回波數據可用式(1)表示

(1)

理論上對N個通道的串行數據si1,si2…siN,其中i=1,2…M,對應N個接收DBF權值wi1,wi2…wiN,這里的接收DBF權值包含了方位維和俯仰維的指向信息[3],則單個采樣點的DBF結果可表示為式(2)

(2)

假設雷達系統采樣頻率為fs,則上述M路A/D數據有效速率為fs×N,則DBF模塊時鐘頻率fdbf可以取值為式(3)

fdbf=I×fs×N

(3)

式(3)中I為正整數,DBF模塊時鐘頻率fdbf可結合需求合理設置I的取值。

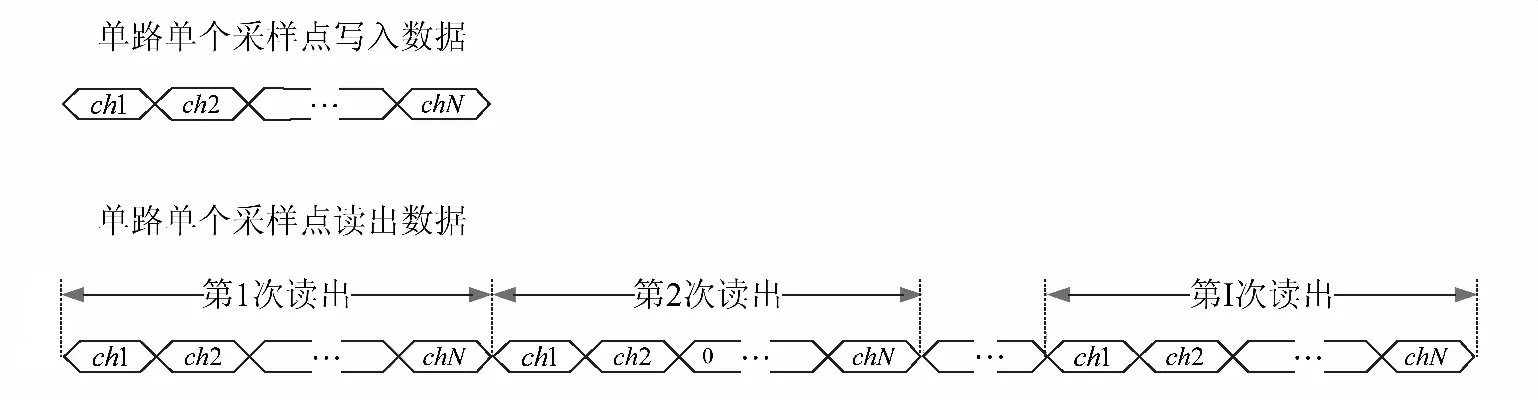

1.2 雙口RAM讀寫控制

根據式(3)的速率關系,M路A/D數據流分別寫入M個雙口RAM,寫有效速率為fwr=fs×N,RAM的讀時鐘frd=fdbf,則frd=fwr×I,即讀時鐘是寫有效速率的I倍。通過控制每個RAM的讀節奏,保證每個采樣點的N個串行數據重復讀取I次,可以保證讀寫的有效速率相等。單路單個采樣點的N通道數據的RAM讀寫數據時序圖如圖1所示。

圖1 RAM讀寫數據時序

RAM將單路單個采樣點的N通道數據重復讀取I次,對應I個指向的DBF接收權值,可同時形成I個接收波束,在FPGA資源使用合理的情況下,對RAM讀出數據并行使用L次,則最多可同時形成波束個數P為

P=I×L

(4)

若雷達系統有兩個基帶采樣頻率fs1和fs2,根據式(3)合理設置DBF模塊時鐘頻率fdbf,保證fdbf與fs1、fs2均是整數倍關系,即

fdbf=I1×fs1×N

fdbf=I2×fs2×N

(5)

根據當前雷達工作的采樣頻率,參數化控制RAM讀出每個采樣點的次數I。因此這種RAM轉換速率的方式可以兼容雷達系統的兩種采樣頻率,適用于具備搜索、跟蹤等多功能的相控陣雷達。

2 級聯DSP48的DBF模塊設計

對于上述M×N形式的數據下傳格式,M路并行數據,每路每個采樣點有N個串行通道數據。由式(2)可知,先對第i路(i=1,2…M)的I×N串行數據與對應的DBF權值進行復乘運算,再對M路復乘結果并行求和,最后對求和結果進行N個串行累加,最終得到單個采樣點的I個波束數據。本節先基于DSP48構建復乘單元,再利用級聯的方式將M個復乘單元級聯相加輸出,最后構建累加器,將串行數據累加輸出波束數據。

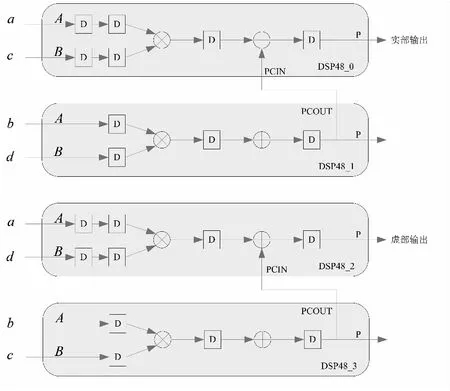

2.1 基于DSP48的復乘模塊結構

復數乘法運算過程如式(6)所示

(a+jb)×(c+jd)=(ac-bd)+(ad+bc)j

(6)

基于式(6)的復數乘法表示,構建的復乘器結構如圖2所示,圖2中使用了4個DSP48,進行了4次乘法運算與2次加法運算,稱為4M2A架構。

圖2 4M2A結構的復乘單元

將式(6)的復乘表示方式轉換,其結果也可用式(7)的方式表示。

(a+jb)×(c+jd)=[(a-b)×d+(c-d)×a]+

[(a-b)×d+(c+d)×b]j

(7)

由式(7)可知,實部、虛部有公共項(a-b)×d,因此可通過級聯的方式,進行3次乘法和5次加法,只需3個DSP48便可實現復乘運算,稱為3M5A結構,其復乘器結構如圖3所示。

圖3 3M5A結構的復乘單元

對于上述兩種復乘結構,單個3M5A結構的復乘單元更節約DSP48資源,但在大型陣列雷達DBF實現過程,多路A/D數據與對應的DBF系數復乘后仍需要并行相加,即將多個復乘單元級聯起來,一路的復乘結果作為輸入與另一路復乘結果相加,采用復乘單元間級聯的方式實現多路復乘結果并行相加。本文針對4M2A復乘結構,詳細介紹了多路并行DBF實現方法。

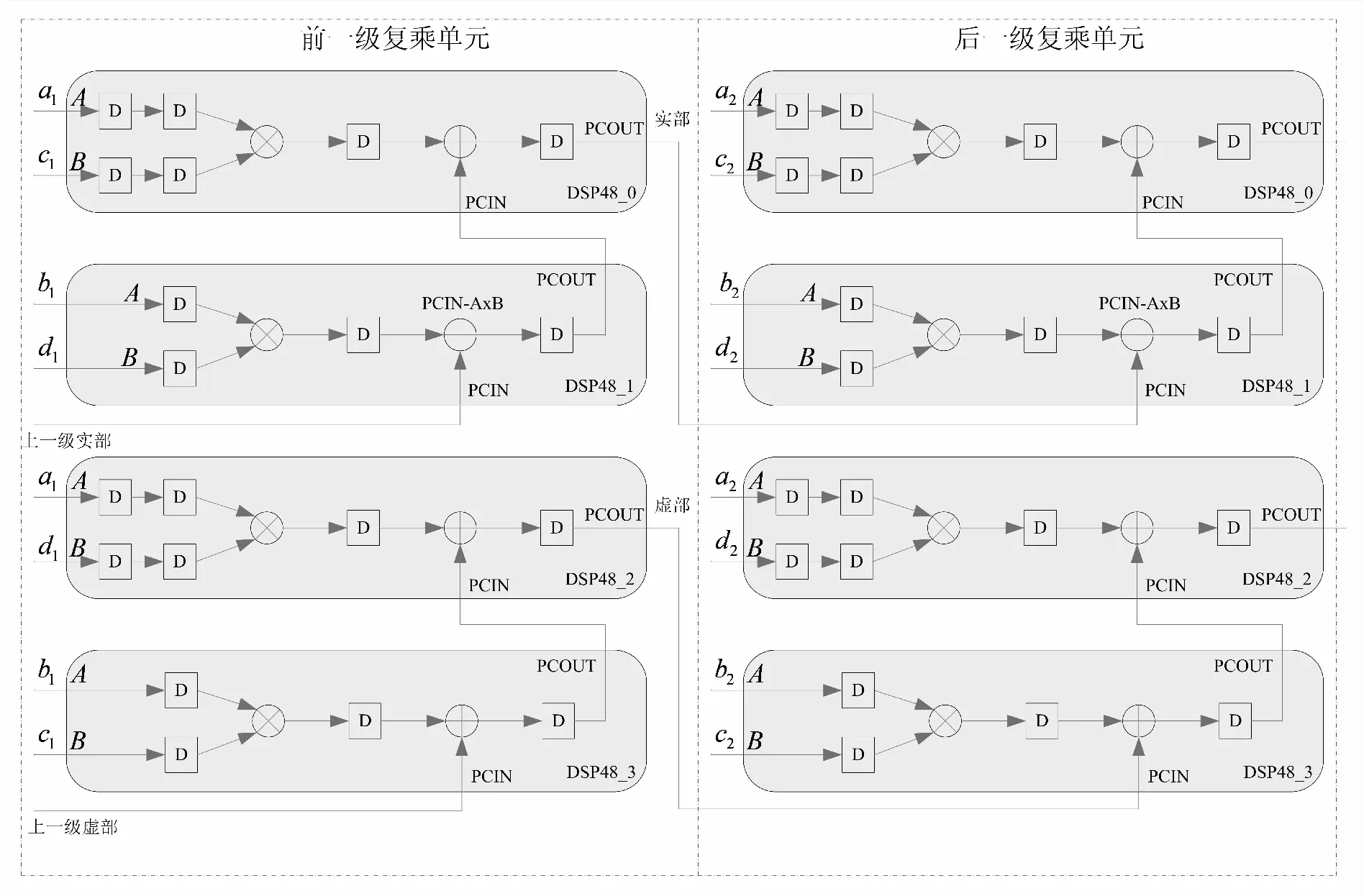

2.2 復乘單元間的級聯結構

將圖2的復乘單元中DSP48_0與DSP48_1最后一級加法器修改,將復乘單元的實部、虛部結果作為輸入,連接到下一個復乘單元,即形成了多個復乘單元的級聯,最后一個復乘單元的輸出即為多路復乘結果的累加結果。需要注意的是相比于前一級復乘單元輸入數據a1,b1,c1,d1,后一級復乘單元輸入數據a2,b2,c2,d2應延遲兩個時鐘節拍,保證復乘單元間級聯相加的數據對齊。圖4給出了相鄰兩個復乘單元的級聯結構。

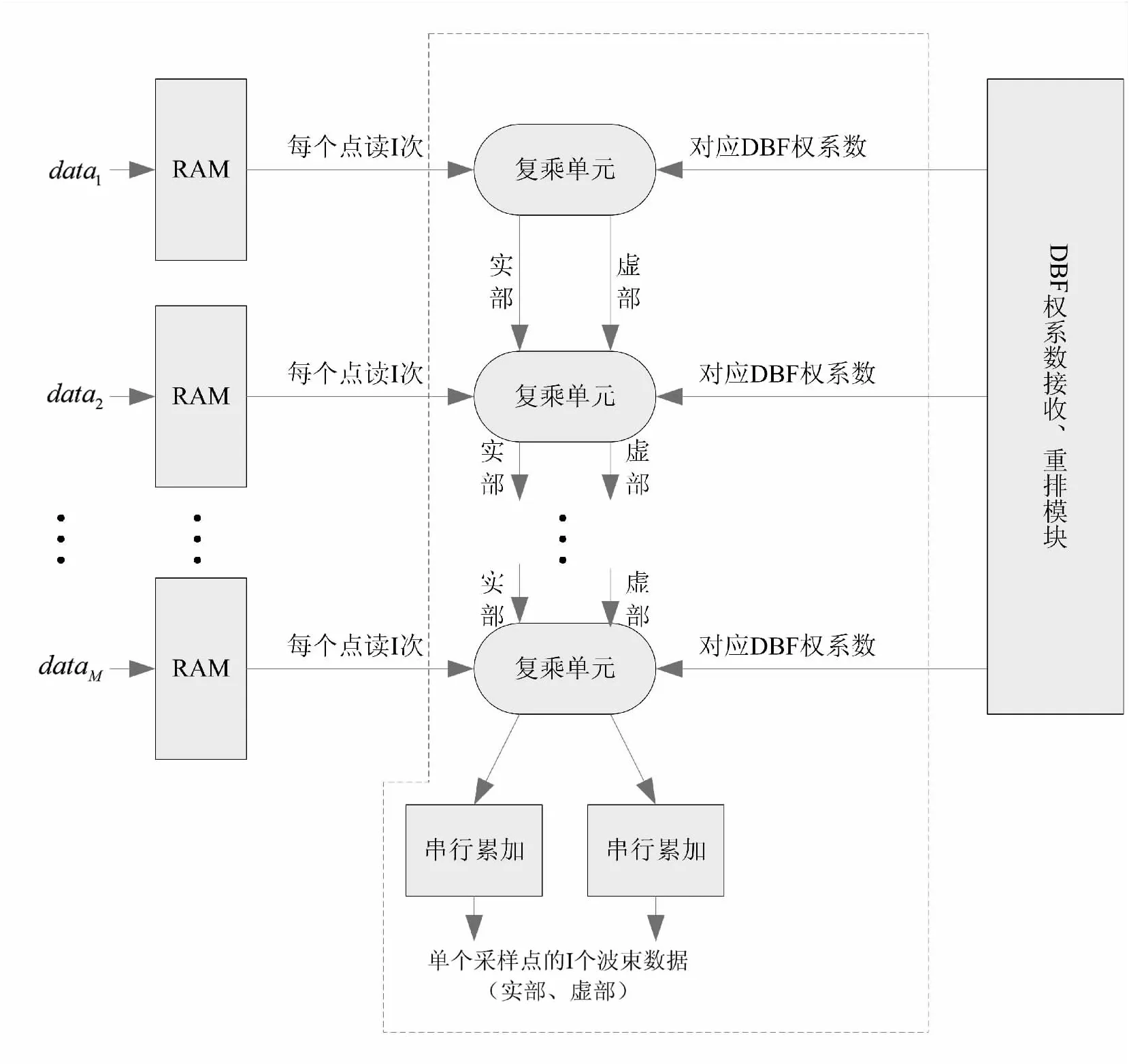

2.3 DBF模塊整體流程

基于1.1節假設的M×N的A/D數據格式(M路并行數據,每路N個通道的串行數據),給出了DBF模塊的整體設計方法:M路并行數據分別寫入RAM,根據寫數據有效速率和讀時鐘頻率的倍數關系,邏輯產生讀節奏控制,將單路單個采樣點的數據重復讀I次,并保證RAM讀寫速率相等。M路RAM讀出的數據進入M個復乘單元,與對應DBF權系數復乘,M個級聯的復乘單元對復乘結果進行并行相加,最后將并行累加結果進行N個串行累加,輸出單個采樣點的I個波束數據。DBF模塊設計流程如圖5所示。

圖5所示的DBF設計模塊,能將M×N的數據合成I個波束數據,若雷達系統要求最多形成P個波束,且P是I的整數倍,即P=I×L,L為正整數。則可將圖5虛線部分重復例化L次。

圖4 相鄰復乘單元間的級聯結構

圖5 DBF模塊整體流程

2.4 DBF實現結果分析

對于全陣列DBF的實現方式,FPGA內部將二維面陣數據等效于一維線陣來做乘累加處理,只是每個陣元對于的DBF權值包含方位維和俯仰維的復合信息。因此為便于實驗的方向圖對比,這里假設二維面陣數據對應DBF權值為一維形式,系統的實驗參數如下所述。

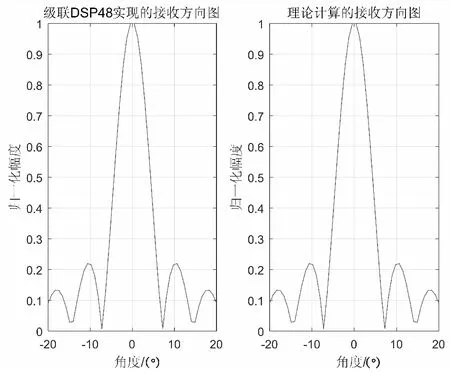

設系統基帶采樣頻率為2.5 MHz,A/D數據格式M×N=4×16,即4路并行數據,每路16個串行通道數據,每路有效數據速率為2.5×16=40 MHz,根據式(3)的時鐘頻率關系,取DBF模塊工作時鐘為240 MHz。按圖5流程,4路數據分別進入4個雙口RAM,每路數據重復讀出6次后,分別進入4個復乘單元與對應6個指向的DBF權復乘。最后一個復乘單元輸出的實部、虛部數據分別進入累加器進行16個數的串行累加,得到單個采樣點的6個DBF數據。并行例化圖5虛線部分8次,在-20°~20°方向等間隔同時形成48個接收波束。圖6給出了基于DSP48級聯的DBF模塊仿真方向圖和理論方向圖。

圖6 FPGA仿真方向圖與理論方向圖對比

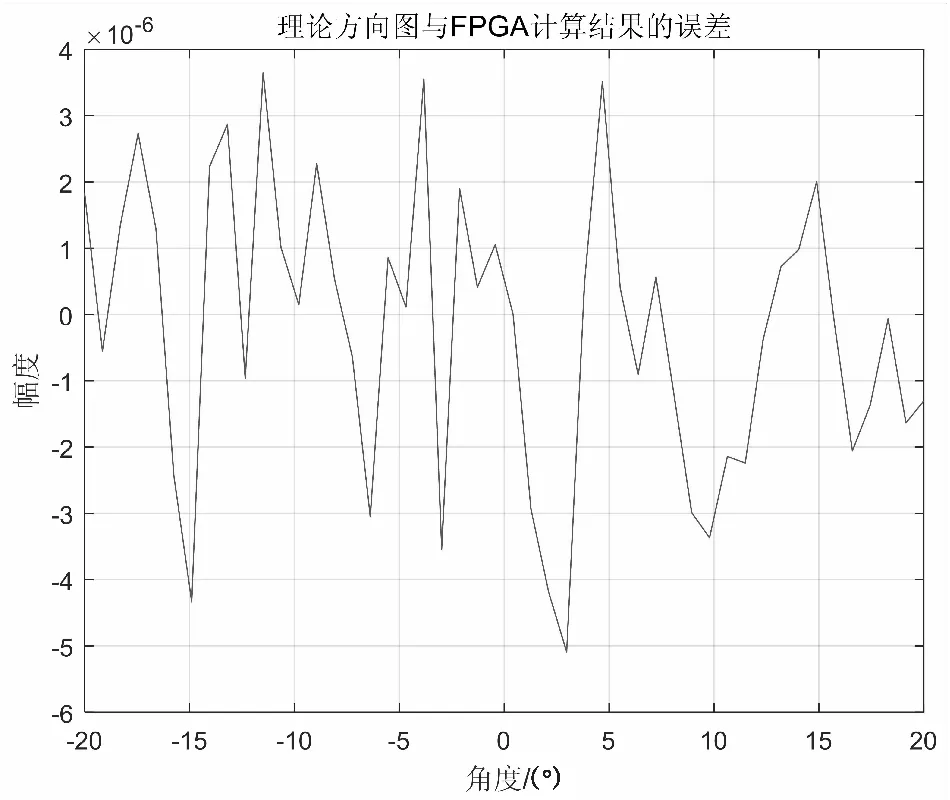

由圖6可以看出,歸一化后FPGA計算的方向圖與理論方向圖的歸一化結果整體相同,兩個方向圖幅度相減得到理論值與實際計算值的歸一化誤差,如圖7所示。

圖7 方向圖實際計算值與理論值誤差

由圖7可知,歸一化方向圖的理論值與實際計算結果誤差在10-6量級,因此本文所述的級聯DSP48的DBF方法具有可實現性。

2.5 DBF模塊優點總結

1)FPGA資源與性能優化:圖5所示的DBF模塊能夠同時形成I個波束數據,其中每個復乘單元使用4個DSP48,最終兩個串行累加器使用2個DSP48,因此若雷達系統要求最多形成P=I×L個波束,則共使用DSP48個數為

(4×M+2)×L

(8)

使用傳統復乘核累加IP Core構建DBF子模塊的方法,每個DBF子模塊使用5個DSP48(復乘占用3個DSP48,實部、虛部累加占用2個DSP48),則在同等條件下共使用DSP48的個數為

5×M×L

(9)

對比式(8)、式(9),M×L較大時,即A/D數據量大、形成波束個數多的情況。級聯DSP48的DBF方法比傳統方法的DSP48利用率降低了約20%,且級聯DSP48的方式使用了DSP48內部專用布線資源,更有利于FPGA時序收斂,在工程實現上具有突出的優勢。

2)雷達系統靈活性提高:本文所述DBF方法,采用對陣元直接加權的方法,每個陣元對應一個包含方位相位、俯仰相位的綜合DBF權值[4]。對于二維相控陣雷達,這種陣元級直接加權的DBF方法增加了方位維、俯仰維形成的波束個數靈活程度;對A/D數據寫入RAM進行速率轉換的模塊,可兼容雷達系統多種采樣頻率,滿足雷達系統搜索、跟蹤等多功能需求。

3)DBF計算誤差降低:FPGA乘法器輸出會帶來數據位寬的成倍擴展,因此需要對乘法結果進行截位,截位的末位舍棄會對處理結果帶來誤差。傳統DBF方式一般進行兩級截位,級聯DSP48結構的DBF模塊,只需對累加結果進行一級截位,因此級聯DSP48的DBF方法能夠提高計算精度。

4)具備模塊可復用性:本文所述的RAM讀寫控制模塊、圖5虛線中DBF子模塊均能夠滿足不同雷達系統DBF功能需求,只需根據系統需求修改相應參數,具備可移植性。

3 結束語

本文根據雷達系統對波束形成靈活性的需求,充分利用FPGA內部DSP48結構和功能,采用DSP48級聯的方式構建復乘單元,且對多個復乘單元級聯的方式,構建DBF總體模塊。同樣在大陣面多波束形成條件下,相對于傳統基于復乘、累加IP Core的DBF模塊方法[5],級聯DSP48的DBF實現方法節約了近20%的DSP48資源,且級聯使用DSP48專用的布線資源,更利于FPGA時序收斂。本方法兼容雷達系統的不同采樣頻率,工程上具有一定的復用性。