低功耗高性能的全MOS電壓基準源設計*

仲召揚,李 嚴

(北京信息科技大學理學院,北京100192)

1 引言

目前市場上比較流行的便攜式、可穿戴式電子產品都需要低功耗做支持,所以電源管理芯片的研究成為了關鍵。電源管理芯片由多個模塊構成,這些模塊有一個共同點——都包含基礎模塊,如低壓差線性穩壓源(LDO)、模數轉換器(ADC)、數模轉換器(DAC)等。而基準源的主要作用就是為這些模塊提供參考和對比電壓或者電流。尤其是在模數轉換電路中,基準源更是有著舉足輕重的作用,其溫度穩系數和電源電壓抑制比的高低決定著模數轉換器的精度好壞[1]。

然而,傳統的雙極型晶體管和電阻構成的帶隙基準源已經逐漸無法滿足要求。以MOS管為主要器件的基準源,具有低輸出電壓、低功耗和面積小的優點,已成為優先選擇。

在此,利用Vth-VT溫度補償(熱電壓VT與溫度成正相關,閾值電壓Vth與溫度成負相關)的原理,實現與溫度和電源電壓無關的帶隙基準。采用共源共柵結構來增大PSRR,增強抗噪聲性能;使用MOS管代替了電阻,約去了輸出電壓表達式的載流子偏移率,增強了溫度特性;使用基本全亞閾值MOS管的結構,造就了該結構的超低功耗性能。

2 亞閾值CMOS基準源

一般認為,當柵源電壓(VGS)大于閾值電壓(VTH)時,MOS管開啟,反之,MOS管截止。但實際上,在VGS小于VTH的一定范圍內(通常約為0.2~0.4V),MOS管的源漏間會有一個非常小的電流。這個漏電流本質上是一種擴散電流,這是一個有別于開啟和截止的特殊的狀態——亞閾值狀態。這種工作狀態下的MOS管與雙極型晶體管類似,源漏電流與柵源電壓呈指數關系。

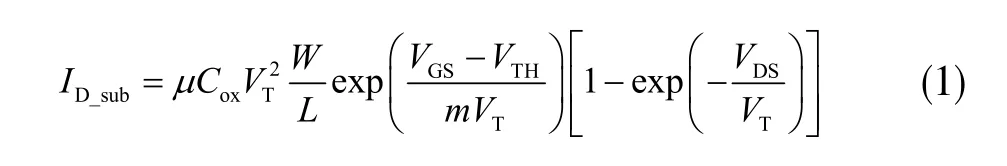

亞閾值狀態下的漏電流公式如下:

其中,μ是載流子遷移率,m是亞閾值修正系數,Cox是柵極氧化層單位面積電容,VT是熱電壓(室溫下約為26 mV)。根據式(1),亞閾值電流ID_sub和柵源電壓VGS之間為指數關系。但基本上在所有情況下,VDS都遠大于VT,從而 1-exp(-VDS/VT)≈1,式(1)可簡化為:

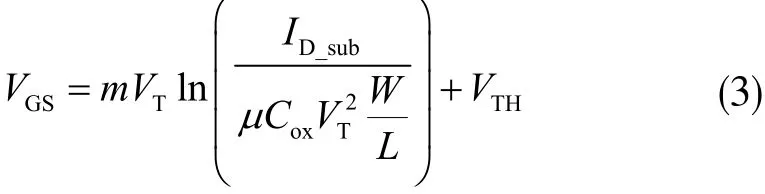

通過對式(2)移項處理,可以得到柵源電壓VGS的表達式:

而VT和VTH分別與溫度成正相關和負相關,所以,通過調整寬長比就可以得到與溫度無關的電壓VGS。但是,可調的寬長比在對數里,需要調整的范圍較大,通過一個MOS管是無法得到的。通過VGS的差值可以將其分配到多個MOS管上,如下式:

其中,K1和K2是MOS管的寬長比。令輸出電壓為n個ΔVGS與VGS的和,即可得到與溫度無關的電壓。

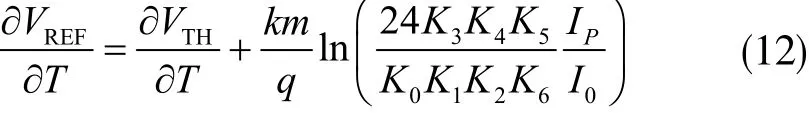

3 基準電壓源電路設計

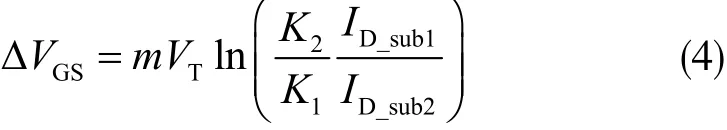

圖1為本次設計的基準電壓源的整體電路圖,可見其由共源共柵電流源電路、溫度補償電路和啟動電路構成。M8、M9、M10、M11、M17、M18、M29 和M30為共源共柵電流源電路,M0~M6為溫度補償電路,M13~M16和 MS為啟動電路,M19~M28為偏置電路。

圖1 所設計基準電壓源的完整電路圖

3.1 共源共柵電流源電路設計

在實際應用中,電流源電路會受到很多因素的影響,尤其是溝道長度調制效應,造成其輸出電阻無法達到理論上的無窮大,對電路的PSRR和線性調整率的影響較大。對此,可采用共源共柵結構,來克服溝道長度調制效應。

在圖1所示電路中,M9工作在深線性區,M12工作在工作飽和區并為M9提供偏置電壓,其他MOS管均工作在亞閾值區。

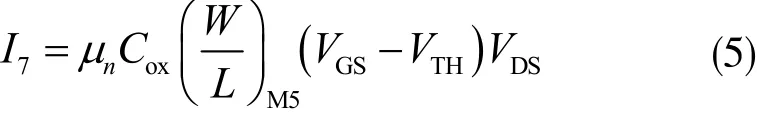

通過M7來確定電流值的大小,并且令M7處于深線性區,VDS接近于0,由漏電流公式可得:

令M12處于飽和區,設 M19和M18的寬長比的比值為M,即I7=MI12,由于M7、M12柵端連接在一起,柵源電壓相等,并且寬長比相等,則可得:

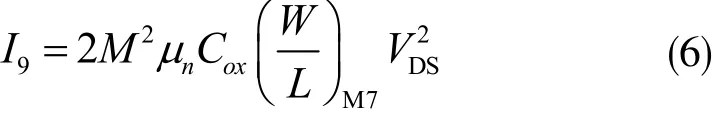

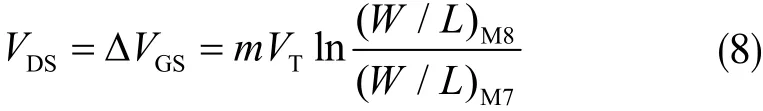

根據亞閾值漏電流公式可得:

因此,M5的漏源端電壓VDS為:

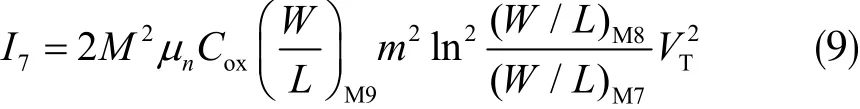

將式(8)帶入式(6)得:

根據式(9)以及載流子遷移率與熱電壓的溫度關系,該電流和溫度有微弱的關系,可以將其忽略。

3.2 溫度補償電路設計

根據上述亞閾值電壓源原理的分析可知,理論上可以通過適當的調節MOS管的寬長比來得到與溫度無關的VGS。但是,實際上單個MOS管是無法達到這么大的寬長比,所以須通過多個柵源電壓的差值和一個柵源電壓串聯來獲得[2]。

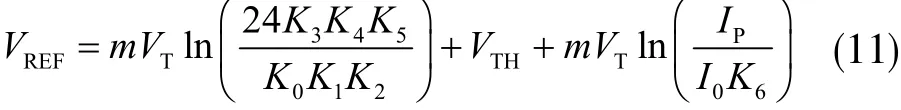

由電壓關系可以得知,M6、M0、M1和 M2管的電流IDS分別為IP、2IP、3IP和 4IP,基準電壓VREF為:

通過亞閾值漏電流公式,可以求得IP的表達式,忽略μ的溫度特性,忽略襯偏效應,最終可得:

VT與溫度成正相關,VTH與溫度成負相關,而VREF是這兩個電壓的線性相加,顯然,只要合理地設計管子的寬長比K0~K6,就可以得到基本和溫度無關的基準輸出電壓。

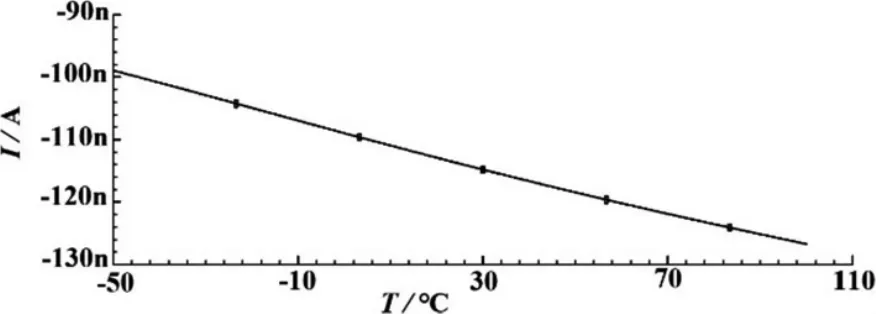

對式(11)兩邊同時對溫度求偏導,得到基準輸出電壓的溫度系數:

令式(12)為0,即可得到與溫度無關的基準電壓。

3.3 啟動電路設計

在各類的偏置電路中,“簡并”點的存在可能會使電流源電流無法正常工作。在設計啟動電路時有以下兩個原則:

①電源上電時,啟動電路向核心電路輸入啟動電流,克服“0”簡并點,使核心電路進入正常的工作狀態;

②啟動電路絕對不能對核心工作電路產生影響,即啟動電路不能對核心工作電路產生輸出,最好是啟動電路在電路開啟后能夠不產生功耗[3-4]。

如圖2,是一個對經典啟動電路的改進版本,略有不同的地方就是此處將一個NMOS管源漏短接當作電容使用。M1和M3是一個反相器,當電路進入正常工作狀態時,把M2的柵極與地接通,其便進入截止區,隔離啟動電路對核心電路的影響。該啟動電路與其他的啟動電路相比,會略微提高總體電路的電源電壓抑制比。M0的柵極與地相連,將其等效為一個電阻,與等效為電容的M4構成了充電電路。當給電源上電時,等效電容M4等于斷路M0的漏端等于VDD,所以M3截止M1和M2導通,M1的漏電流通過M2源端進入到基準電路,給基準電路輸入電流,消除“0”簡并點。電容充電完成后,M1和M3組成的反相器,把截止的M2源極短路到地,從而啟動電路和核心電路基本完全脫離。

圖2 改進的啟動電路示意圖

4 版圖設計及電路后仿真

基于SMIC0.18μm CMOS工藝,進行了設計、版圖繪制、和前、后仿真。如圖3所示為本基準源的版圖設計。

圖3 所設計電路的版圖

在-50~100℃溫度范圍內,輸出電壓溫度特性的后仿真結果如圖4所示,溫度變化值為3.5mV,溫度系數為39ppm/℃。

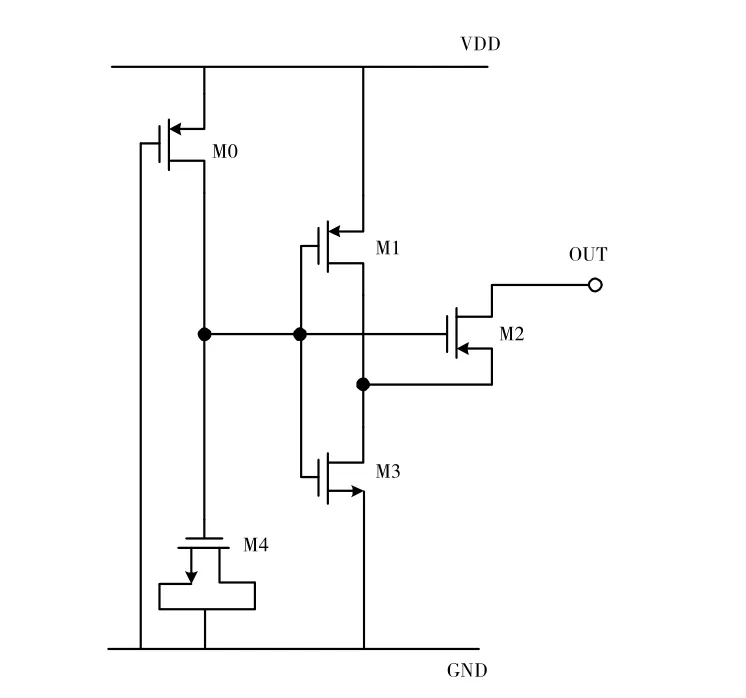

在常溫(25℃)下,圖5為靜態電流溫度特性的后仿真結果,其靜態電流為113.8nA,電路功耗僅為204.84nW,基準輸出電壓為596.9mV。

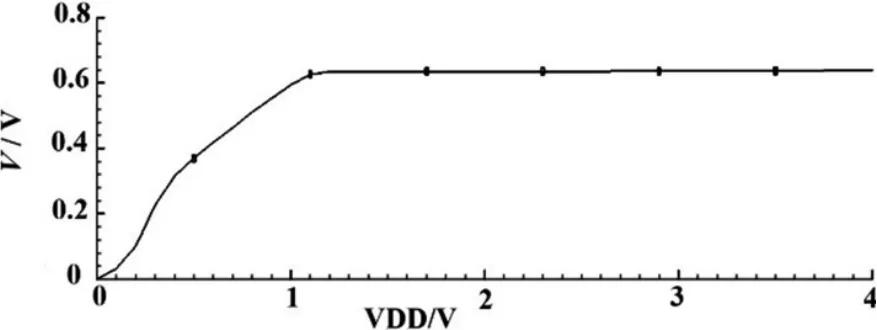

圖6為基準源電壓調整率的后仿真結果,電源電壓范圍為1.1~3.0V時,電源電壓的線性調整率為0.05%。

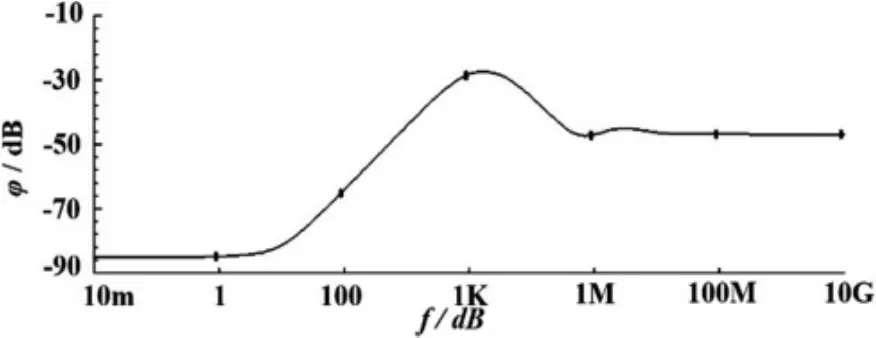

圖7為基準源的PSRR的后仿真結果,當噪聲為100Hz時的電源電壓抑制比為64.17dB,1kHz時為44.26dB。

本設計仿真后的各項參數與其他文獻設計的基準源電路性能對比如表1所示。

圖4 基準輸出電壓溫度特性曲線

圖5 基準靜態電流溫度特性曲線

圖6 電壓調整率仿真曲線

圖7 電源電壓抑制比曲線

表1 本設計改進基準源與其他基準源的對比

5 結束語

本次設計的基準源電路在線性調整率和靜態功耗方面具有很明顯的優勢;溫度系數只比文獻[6]略高,但是這對于結構簡單的一階補償方法來說,已經是很好的結果;對比文獻中的PSRR都較高,差距不大,都具有較好的抗電源噪聲能力。可見,所設計的基準電壓源,可以做到低溫度系數、低線性調整率、高PSRR和低功耗,可以適應便攜式、可穿戴式電子產品的使用。