基于以頂層ITO為像素電極設計的產品工藝優化

呂艷明,操彬彬,栗芳芳,安 暉,葉成枝,李法杰,楊增乾,彭俊林,馮耀耀,劉增利,陸相晚,李恒濱

(合肥鑫晟光電科技有限公司,安徽 合肥230001)

1 引 言

高開口率高級超維場轉換技術(HADS)薄膜晶體管(TFT)中使用的有機膜絕緣層膜厚可達數微米,并且介電常數低、平坦度高[1-2],極大地增加了信號線(Data)與公共電極(Common)、像素電極(Pixel)之間的間距,有利于減少寄生電容、降低功耗、增大開口率。

負性有機膜因感光性好、顯影速率高、產能高、工藝步驟少等優點,在TFT-LCD行業中應用最為廣泛。但負性有機膜由于需要大面積曝光交聯,因此更容易受光路中的顆粒物影響,造成光刻后圖案厚度偏薄甚至缺失。對于頂層氧化銦錫(ITO)為像素電極(Pixel Top)、首層ITO為整面覆蓋的公共電極的TFT而言,若信號線上方的有機膜厚度偏薄將會拉近信號線與公共電極之間的距離,嚴重時將導致兩者之間的短路(Data-Common Short,DCS),造成暗線不良。在此背景下,本文通過工藝流程變更從源頭上規避了上述形式DCS不良的發生,有效提升了良率,節約了生產成本。

2 有機膜產品DCS不良介紹

2.1 DCS不良現象

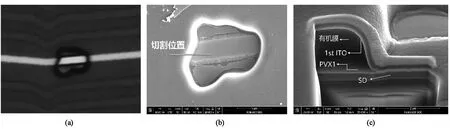

圖1(a)為TFT陣列工藝終檢工序電學測試檢出的DCS不良顯微鏡圖,圖中可見不良位置存在膜層異常。圖1(b)為不良位置聚焦離子束俯視圖,圖中可見不良位置存在明顯的膜層缺失產生的凹坑。進一步用離子束按圖1(b)標示位置對凹坑處切割,從圖1(c)切割后截面圖可以清晰地看出有機膜和第一鈍化絕緣層(PVX1)缺失,但未見膜層熔融痕跡,可排除靜電擊穿。顯然絕緣層的缺失造成了信號線與公共電極ITO之間的直接導通,導致該處信號線信號被公共電極信號拉動,從而被電學檢測檢出DCS。

圖1 DCS不良。(a)顯微鏡圖;(b)聚焦離子束俯視圖;(c)聚焦離子束截面圖。

2.2 DCS不良機理分析

從圖1(c)中可以看出DCS位置的公共電極ITO上方各膜層以及下方的信號線膜層均正常,因此不良產生工序應為有機膜至PVX1之間。通常有機膜厚度相對較厚(2~3 μm),有機膜涂覆時烘烤的熱交聯效應及曝光時的射線衍射易導致開孔區底部形成殘膜,故常利用干法刻蝕進行表面處理(PVX1刻蝕):一方面利用干法刻蝕的物理轟擊、化學氧化作用清除殘膜;另一方面對于首層ITO為像素電極設計的HADS產品,可利用有機膜做掩膜同步形成像素ITO與TFT信號線源/漏極導通的開孔。一般情況下,PVX1刻蝕對有機膜厚度的損耗僅為0.2~0.3 μm,顯然不足以將有機膜刻穿。因此,圖1中有機膜的缺失應主要與其自身制程的異常相關,其中最常見的情況為制程中顆粒導致的負性光阻異常。如圖2所示,曝光過程中異物附著在有機膜表面,產生類似光罩(Mask)的遮光效應,遮光嚴重情況下會導致顯影時有機膜的缺失。進一步地,PVX1刻蝕掩膜的缺失將導致PVX1膜層的缺失,最終導致頂層ITO為像素電極設計的HADS產品的公共電極ITO與信號線在異常區域短接形成DCS不良。

圖2 DCS不良發生機理

3 DCS不良改善方案與實驗驗證

鑒于行業內TFT制程中微小顆粒異物無法做到100%管控規避,通過提高設備內的潔凈度管控來改善有機膜異常導致的DCS不良效果有限。對于頂層ITO為像素電極的產品而言,顯示區內公共電極ITO無須與源/漏極直接導通,故可考慮將PVX1刻蝕工序省略。基于上述DCS不良發生機理,即使有機膜發生缺失,PVX1的存在仍可有效對公共電極ITO與信號線起到絕緣作用。

由此可以建立如圖3(b)所示新的TFT制作工藝流程,與圖3(a)所示現有工藝流程對比:(1)PVX1刻蝕省略,即新工藝流程中公共電極ITO沉積前PVX1完全保留;(2)顯示區和周邊過孔全部在第二鈍化絕緣層(PVX2)刻蝕時形成,即PVX2、PVX1、柵極絕緣層(GI)3層氮化硅同步刻蝕。最終如圖4所示,有效避免了有機膜異常導致的公共電極ITO與信號線短接現象。

3.1 “一步刻蝕”工藝初探

為驗證新工藝流程對DCS改善效果,在某高分辨率以頂層ITO為像素電極設計的HADS有機膜產品上進行實驗。按照圖3(b)所示新工藝流程進行全膜層TFT基板制作,制作完成后對TFT基板進行電學檢測,確認DCS發生率。測試時輸出界面基板缺陷圖出現大量黃斑、黃線,報出大面積不良,但顯微鏡確認未發現明顯異常。通過掃描電子顯微鏡進一步確認周邊跨接過孔截面,結果如圖5所示,連通柵極的跨接過孔在PVX1層存在非常嚴重的底切(Undercut)現象,導致ITO在PVX1處斷裂。信號斷路后造成大面積不良發生,無法甄別DCS是否得到有效改善。

圖3 工藝流程變更。(a)原工藝流程;(b)新工藝流程。

圖4 DCS改善原理

鑒于PVX1處存在底切現象,推測PVX1膜質相對偏軟。進一步地對單層膜進行刻蝕率測試發現PVX1刻蝕率最大(見圖6標示),即PVX1膜質最軟,與此前分析相符。圖6表示了PVX1層底切的發生機理:干法刻蝕同時存在物理性各向異性刻蝕和化學性各向同性刻蝕。物理性刻蝕主要通過離子轟擊,垂直于基板方向進行刻蝕,對PR膠形貌依賴性大;而化學性刻蝕則對被刻蝕膜層的膜質依賴性大,刻蝕效率高,膜層間刻蝕率不匹配情況下容易在膜質較軟膜層處產生底切現象。

圖5 TFT柵極過孔截面

圖6 PVX1 底切形成機理

3.2 刻蝕率匹配調整

PVX1位置膜層出現底切的根本原因在于PVX1刻蝕率大于PVX2刻蝕率,要解決底切問題首先需要進行膜質變更以實現膜層刻蝕率匹配,即要保證膜層刻蝕率滿足PVX2>PVX1>GI。在3種氮化硅膜層中,PVX1作為有機膜第一鈍化層,功能性要求低且厚度最薄,膜質變更品質風險最小,因此選擇調整PVX1膜質較為合適。為此按表1所列成膜條件進行PVX1膜質變更的4因子2水平實驗設計,對各條件對應的PVX1單膜刻蝕率進行測量,測量結果如表1所示。

表1 PVX1 等離子增強化學氣相沉積成膜工藝優化實驗設計

續 表

(“-”表示同改善前條件)

從圖7刻蝕率測試結果的主效應圖可以看出,在選定的實驗條件下,增大成膜射頻功率、降低成膜壓力、減小電極間距以及增大SiH4∶NH3氣體流量比均可降低膜層刻蝕率;標準化效應正態圖顯示射頻功率、壓力、電極間距對刻蝕率影響顯著,氣體流量比影響不顯著。

圖7 PECVD成膜參數對刻蝕率影響分析。(a)主效應圖;(b)標準化效應正態圖。

各成膜條件對膜質影響機理如下:增大成膜射頻功率可以提高反應氣體激活效率及沉積速率,增加等離子體密度,可增加薄膜中Si—N鍵,減少Si—H鍵、N—H鍵,使薄膜無序程度降低,提高薄膜表面均勻性和有序性[3],提高薄膜的致密性[4]和膜層硬度。降低反應腔體壓力,可使反應物自由電子的平均自由程變長,在高頻電場中碰撞加速獲得更多能量[5],提高激活反應氣體的能力,可減少成膜成分中Si—H、N—H鍵及雜質成分,雖然反應氣體分解得到的活性等離子體向基底運動動能變大,但單位時間內到達基板表面的粒子數目變少,沉積速率會下降,這也利于氮化硅薄膜的整齊均勻生長,增大氮化硅密度[6-10]。電極間距過大會影響薄膜沉積速率,造成顆粒性粉塵問題;而電極間距過小會使離子反應速度過快,薄膜沉積質量下降。在適當區間內減小電極間距雖然沉積速率會有所下降,但會使等離子體密度提高,Si—N鍵結合增強,可以得到相對較好的成膜質量和良好的薄膜平坦度。當NH3流量較大時,等離子增強化學氣相沉積成膜物質中Si—H鍵、N—H鍵含量高,氮化硅膜質會較疏松[11],而通過減少NH3流量即增加SiH4∶NH3流量比可減少Si—H成鍵,成膜成分傾向于Si3N4原子計量比,從而提高膜層硬度。

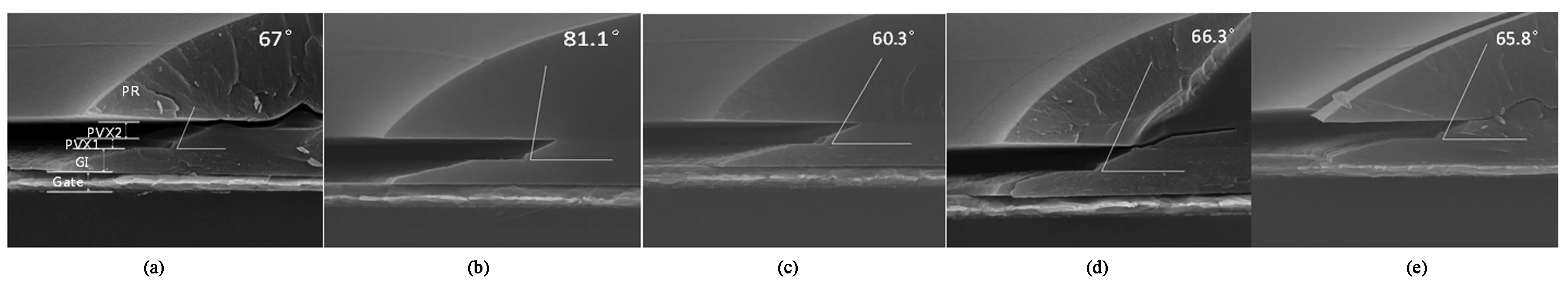

從表1中各成膜條件對應的PVX1刻蝕率結果可以看出,成膜條件2、7刻蝕率較大,不滿足刻蝕率要求,成膜條件1、3、4、5、6滿足刻蝕率匹配要求。但圖8掃描電子顯微鏡觀察到的使用條件1、3、4、5、6成膜的樣品,柵極過孔刻蝕截面有明顯差異。其中條件3的刻蝕后PVX1層坡度角超過80°,ITO鍍膜斷線風險較大;條件1、5、6 PVX1層坡度角差異不大,均在66°左右;條件4坡度角為60.3°,相對最好。

以上雖然通過等離子增強化學氣相沉積成膜優化已經得到了較好的成膜條件,PVX1層底切有明顯改善,但從圖8中可以看到最優條件4的PVX1刻蝕臺階仍比較明顯,在PVX1、PVX2交界面可觀察到輕微的尖角。這種情況可以通過干法刻蝕調整進一步優化。

圖8 柵極過孔掃描電子顯微鏡圖。(a)條件1;(b)條件3;(c)條件4;(d)條件5;(e)條件6。

3.3 PVX1刻蝕坡度角改善

為進一步改善膜層界面的刻蝕臺階,減緩刻蝕坡度角,在成膜條件4基礎上按表2所示工藝條件使用增強型等離子體耦合干法刻蝕機進行干法刻蝕工藝優化實驗,其中條件A為理論惡化條件(壓力降低,物理刻蝕加強)作為參照,各實驗條件對應的柵極過孔掃描電子顯微鏡圖如圖9所示。

表2 干法刻蝕工藝優化

(“-”表示同改善前條件)

圖9 不同刻蝕條件柵極過孔掃描電子顯微鏡圖。(a)條件A;(b)條件B;(c)條件C;(d)條件D。

增強型等離子體耦合干法刻蝕設備的主要特征是其下部電極接有13.56 MHz源極射頻和3.2 MHz的偏置射頻。其中源極射頻頻率相對高,主要用來解離反應氣體,生成自由基和離子。帶電粒子在源極射頻產生的電場中運行距離短,對基板轟擊作用小,主要依靠自由基與基板表面的薄膜發生反應進行化學性刻蝕。而偏置射頻頻率相對較低,波長長,帶電粒子在偏置射頻產生的電場中運行距離長,對基板表面的離子轟擊效果較大,物理性刻蝕效果明顯[12]。

干法刻蝕反應腔室的壓力變化會直接影響等離子體密度和化學反應方向。壓力升高反應腔室內化學活性的自由基和離子濃度增加,化學刻蝕作用增強,刻蝕坡度角會有降低趨勢[13]。而壓力降低時,離子之間、離子與原子之間碰撞減少且自由基濃度降低,橫向刻蝕速率降低,離子轟擊基板表面的物理刻蝕作用增強。

從圖9中過孔掃描電子顯微鏡圖像和PVX1層坡度角可以看出,條件A刻蝕壓力降低,由于物理刻蝕增強,刻蝕坡度角惡化變大。而刻蝕壓力變大、偏置射頻功率降低的化學刻蝕增強條件B~D的刻蝕臺階均較表1中條件4對應的量產刻蝕條件的坡度角有所改善,其中壓力和偏置射頻功率變更組合條件D與僅變更壓力或僅變更偏置射頻功率的條件B、C相比,不僅PVX1層坡度角最小,而且PVX1層刻蝕臺階最短,幾乎觀察不到膜層界面尖角。條件A~C的柵極過孔掃描電子顯微鏡圖像均能看到3種不同氮化硅絕緣膜層坡度角不同形成的3個斜坡,而條件D的PVX1、PVX2層的坡度角差異較小,過孔截面僅能看到兩個膜層斜坡且膜層間臺階過渡自然平緩。

綜合以上實驗結果,使用成膜條件4進行PVX1層成膜并采用刻蝕條件D進行干法刻蝕可以解決“一步刻蝕”工藝流程的柵極過孔PVX1膜層底切問題,獲得良好的刻蝕坡度角。

4 量產投入驗證

對采用成膜條件4搭配刻蝕條件D的“一步刻蝕”工藝條件進行生產投入驗證,“一步刻蝕”條件與量產條件各投入120張玻璃基板加工至TFT完成,進行陣列電學檢試并通過陣列維修工序全抓圖判定,統計DCS不良發生率,結果如圖10所示。

圖10 DCS改善前后良率對比。(a)DCS改善效果;(b)有機膜缺失型DCS改善效果。

從圖10可以看出,采用優化后的“一步刻蝕”工藝,總DCS不良率較同批次量產條件下降了0.9%,而有機膜缺失型的DCS不良發生率降為0。說明優化后的新工藝流程可徹底改善頂像素電極設計HADS產品有機膜缺失型DCS不良。

5 結 論

本文從HADS有機膜產品DCS不良產生的機理入手,提出了PVX1刻蝕工序省略,在PVX2刻蝕時進行外圍柵極跨接過孔處多層氮化硅“一步刻蝕”的工藝方案。通過優化PVX1成膜工藝進行刻蝕率匹配消除跨接過孔PVX1層底切不良,并在優化后的PVX1膜層基礎上調整干法刻蝕工藝進一步改善過孔刻蝕坡度角和刻蝕臺階,使得過孔處膜層間臺階過渡自然平緩,實現“一步刻蝕”工藝的導入,HADS有機膜產品特有的有機膜缺失類型DCS不良得到徹底解決。新的工藝流程不僅提升了產品良率和產品在市場中的競爭力,還縮減了工藝步驟,大幅提升了產能,收到了良好的經濟效益。實驗中通過工藝流程變更進行不良改善的思路,以及等離子增強化學氣相沉積、干法刻蝕工藝優化方法,也為新產品、新工藝的開發提供了指導和借鑒。